### Ultra-Low Power and Reliable SRAM for System-on-Chip

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science

University of Virginia

in partial fulfillment of the requirements for the degree

Doctor of Philosophy

by

Harsh Naranbhai Patel

December 2017

# **APPROVAL SHEET**

### This Dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Author Signature: <u>Harsh N. Patel</u>

This Dissertation has been read and approved by the examining committee:

Advisor: Prof. Benton H. Calhoun

Committee Member: Prof. John Lach

Committee Member: Prof. Mircea R. Stan

Committee Member: Prof. Kevin Skadron

Committee Member: Prof. Scott T. Acton

Committee Member: \_\_\_\_\_

Accepted for the School of Engineering and Applied Science:

OB

Craig H. Benson, School of Engineering and Applied Science

December 2017

© 2017 Harsh Naranbhai Patel

### Abstract

The number of ubiquitous sensors has increased to more than double the human population and is expected to continue growing in the future. The pervasive use of sensors for applications such as personal healthcare and the Internet of Things (IoT) presents a growing sustainability challenge concerning the availability and accessibility of power sources. With 50 billion devices expected to be connected to the Internet by 2020, recharging or replacing batteries at a regular interval will result in enormous time and cost overhead due to the restricted growth of batteries. Therefore, the need for the self-powered systems is being researched as an alternative solution to operate at scaled supply voltage below its threshold voltage to minimize an active power  $(CV_{DD}^2)$ . The important metrics for such applications change from the traditional performance-driven to low-energy (i.e., longer battery life) and reliability. To address these challenges, it has become critical to re-evaluate the different design decisions made under high-performance requirements and to revalidate any different trade-offs among the metrics under consideration.

While analyzing the major contributors for power dissipation in present state-of-the-art low-power ICs, it has been found that Static Random Access Memory (SRAM) consumes almost 65% of the total chip power. Therefore, designing an SRAM to operate in the subthreshold region of operation provides an opportunity for reducing the overall power dissipation in such low-power ICs. However, the SRAM functionality in the sub-threshold operation becomes extremely sensitive to the process and temperature variations, and other environmental conditions such as radiation-induced soft errors. As a result of these factors, the power reduction and robustness become major challenges for the subthreshold design targeting ULP platforms.

In this work, we present various circuits and architectural techniques to enable ULP and reliable SRAMs to optimize energy per operation for a complex System-on-Chip (SoC). We investigate various subthreshold SRAM design trade-offs to achieve a sub-uW batteryless BSN system. First, we explore different design knobs for an optimal SRAM design targeting ULP applications. These knobs include leveraging advanced fabrication technology, optimal device selection, circuit design techniques, and architectural techniques. Next, we evaluate the efficacy of different read and write peripheral assist techniques for improving reliability and energy efficiency of subthreshold SRAMs and provide stability, power, and performance trade-offs for system level optimization. The result of various optimization approaches resulted in a leakage and energy optimized SRAM operating over with leakage power reduced to 1.5 pW/bit while consuming only 6.24 pJ/access energy that is 40% more efficient than the previous version. To address a wide range of IoT applications with energy optimization, we propose a Canary sensor based minimum supply voltage ( $V_{MIN}$ ) tracking with optimal selection of the peripheral assist techniques. Later, we address the reliability issue at subthreshold operation using a process, voltage, and temperature (PVT) variation mitigation controller. Finally, the impact of the radiation-induced soft error is evaluated to provide a comprehensive study on reliability for the ULP SRAM at scaled  $V_{DD}$ . Dedicating what all I learn in my life to

'Gurus' in my life — for enlightening my life with the knowledge,

My Parents — for always giving me the courage to achieve impossible,

My Wife - Pooja — for her unwavering love and motivation

### ॐ असतो मा सद् गमय। तमसो मा ज्योतिर्गमय। मृत्योर्माऽमृतम् गमय ॥

Meaning: Lead me from the unreal to the real; from darkness(ignorance) to light(knowledge); and from death to immortality.

### Acknowledgments

कायेन वाचा मनसेंद्रियैर्वा । बुद्ध्यात्मना वा प्रकृतिस्वभावात् । करोमि यद्यत् सकलं परस्मै । नारायणायेति समर्पयामि ॥ ॥

Meaning:

Whatever I perform with my body, speech, mind, limbs, intellect, or my inner self either intentionally or unintentionally, I dedicate it all to that Supreme Lord Vishnu...

I can still remember the day when I received an email from UVA about my acceptance for Ph.D. I cannot thank god ever enough in my life to give this opportunity. I would like to acknowledge many people throughout my journey of seeking for the knowledge without whom I would not be able to achieve what I have done till date. I hope I will able to remember everyone those have helped me along the way of this journey of learning. I will always remember the days I spent at UVA.

First and foremost, I would like to thank my Guru/adviser - Professor Ben Calhoun. This journey is only possible due to his ability to see me achieving what I am till date. I clearly remember my first 'most sloppy ever' plot of results that I shared with him. Since then, his advice made me like a polished diamond from a raw carbon over the period. His highly influential teaching skill made a significant impression on my mind about 'how to teach.' I am thankful to him for learning not just technical skills but many more non-technical skills those help me (and will be helping me in future!) throughout my course of Ph.D. Thank you, Ben, for everything you did to support and your incredible guidance. I hope my gratitude to you can be seen in my commitment to becoming the best version of myself,and in my determination to strive for perfection.

vi

I am also grateful to have Professor John Lach, Professor Kevin Skadron, Professor Mircea Stan, and Professor Scott Acton as my committee members. I thank all committee members for their continuous support and providing insightful feedback to my research - Thank you all!

A major part of my learning came from working with awesome friends and colleagues at Bengroup. I consider myself very lucky to work in Bengroup with amazing students. I like to thank Jim Boley for his patience during my early days at UVA with lots of questions. I also thank Bengroup senior students: Alicia Klinefelter, Yousef Shakhsheer, Aatmesh Shrivastava, and Kyle Craig, for their support. I am very privileged to work in close collaboration with Jim Boley, Farah Yahya, Arijit Banerjee, and Ningxi Liu as the SRAM team. Especially, I appreciate and thank Farah Yahya, with whom I worked a lot throughout my Ph.D., for her support and readiness to exchange ideas. I am glad to have an opportunity to work with Abhishek Roy and Divya Akella for the continuous exchange of ideas we had throughout the work. As a part of Rice Hall Lab 322, I enjoyed the company of Seyi Ayorinde, Chris Lukas, He Qi, Ningxi Lui, Kevin Leach, Henry Bishop, and Daniel Truesdell. I would also like to thank Kevin Leach for providing his technical expertise on my research work and technical papers. I would like to give my special thanks to Terry Tigner for her 'Dove' love. Her tremendous support made us possible to test our chips timely and a hassle-free conference journey!

I want to thank all the sponsors who have supported my research. Special thanks to Tom Gray - my manager, and Brian Zimmer - my mentor, at NVIDIA for giving me an opportunity to be a part of a cutting edge research work.

Besides my life at the lab doing the research work, I immensely enjoyed my stay in Charlottesville. I am very much grateful to my neighbors for their pleasant company during my stay. I am also grateful to the members of Swadhyay Parivar for their selfless love.

Last but never the least, I would like to thank my family members. I am very grateful for my parents, Naranbhai and Induben, for their continuous support and motivation for pursuing higher education. Especially, I thank my mother for always keeping me in her prayer while my father for giving me the courage to achieve whatever seems impossible to me. I thank my sister - Rinku - for her sisterly love. I cannot encompass my gratitude to my wife, Pooja, with the words for her support. She always been a lovely wife with continuous support. I am also indebted to almighty God for his blessing of two beautiful children, Samyak and Swara — my best stress busters! I cannot image myself completing my Ph.D. without the help of all these three - my wife and my kids — Thank you so much!

# Contents

| List of Tables       x         List of Figures       xi         1       Introduction       1         1.1       Motivation       1         1.2       Thesis Statement       4         1.3       Dissertation Organization       5         1.3.1       Background       5         1.3.2       Subthreshold SRAM for ULP Body Sensor Node       5         1.3.3       SRAM V <sub>MIN</sub> Tracking using Canary and Optimal Assist Selection       6         1.3.4       Reliability at Ultra-Low Voltage Operation       6         1.3.5       Conclusions       7         2       Background       8         2.1       Basic Operations       9         2.1.1       Write Operations       9         2.1.2       Read Operations       10         2.1.3       Hold Operations       10         2.1.3       Hold Operations       10         2.1.4       Write Operations       11         2.2       Resist Echniques: An Overview       11         2.3       Subthreshold SRAM Design for an ULP BSN       19         3.1       Introduction       19         3.2       Research Approach       21         3.3 <th>C</th> <th>onter</th> <th>nts</th> <th>viii</th>                                                                                                                                                   | C        | onter | nts                                                                     | viii |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------------------------------------------------------------------------|------|

| 1Introduction11.1Motivation11.2Thesis Statement41.3Dissertation Organization51.3.1Background51.3.2Subthreshold SRAM for ULP Body Sensor Node51.3.3SRAM $V_{MIN}$ Tracking using Canary and Optimal Assist Selection61.3.4Reliability at Ultra-Low Voltage Operation61.3.5Conclusions72Background82.1Basic Operations92.1.1Write Operations92.1.2Read Operations102.1.3Hold Operations102.1.3Hold Operations112.4Assist Techniques: An Overview112.3Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | List  | of Tables                                                               | х    |

| 1.1       Motivation       1         1.2       Thesis Statement       4         1.3       Dissertation Organization       5         1.3.1       Background       5         1.3.2       Subthreshold SRAM for ULP Body Sensor Node       5         1.3.3       SRAM V <sub>MIN</sub> Tracking using Canary and Optimal Assist Selection       6         1.3.4       Reliability at Ultra-Low Voltage Operation       6         1.3.5       Conclusions       7         2       Background       8         2.1       Basic Operations       9         2.1.1       Write Operations       9         2.1.2       Read Operations       10         2.1.3       Hold Operations       10         2.1.3       Hold Operations       11         2.2       Assist Techniques: An Overview       11         2.3       Subthreshold SRAM Design Challenges       13         3       Energy Efficient Subthreshold SRAM Design for an ULP BSN       19         3.1       Introduction       19         3.2       Research Approach       21         3.3       Technology Consideration: Deeply Depleted Channel       23         3.3.1       DDC Technology Advantages and Low-Power Optimiz                                                                                                                                       |          | List  | of Figures                                                              | xi   |

| 1.2       Thesis Statement       4         1.3       Dissertation Organization       5         1.3.1       Background       5         1.3.2       Subthreshold SRAM for ULP Body Sensor Node       5         1.3.3       SRAM V <sub>MIN</sub> Tracking using Canary and Optimal Assist Selection       6         1.3.4       Reliability at Ultra-Low Voltage Operation       6         1.3.5       Conclusions       7         2       Background       8         2.1       Basic Operations       9         2.1.1       Write Operations       9         2.1.2       Read Operations       10         2.1.3       Hold Operations       11         2.2       Assist Techniques: An Overview       11         2.3       Subthreshold SRAM Design Challenges       13         3       Energy Efficient Subthreshold SRAM Design for an ULP BSN       19         3.1       Introduction       19         3.2       Research Approach       21         3.3       Technology Consideration: Deeply Depleted Channel       23         3.3.1       DDC Technology Advantages and Low-Power Optimization       24         3.3.2       Body Biasing: Leakage Minimization and Reliability Challenge       26 <td>1</td> <td>Intr</td> <td>roduction</td> <td>1</td>                                                          | 1        | Intr  | roduction                                                               | 1    |

| 1.3 Dissertation Organization       5         1.3.1 Background       5         1.3.2 Subthreshold SRAM for ULP Body Sensor Node       5         1.3.3 SRAM V <sub>MIN</sub> Tracking using Canary and Optimal Assist Selection       6         1.3.4 Reliability at Ultra-Low Voltage Operation       6         1.3.5 Conclusions       7         2 Background       8         2.1 Basic Operations       9         2.1.1 Write Operations       9         2.1.2 Read Operations       9         2.1.3 Hold Operations       10         2.1.3 Hold Operations       11         2.2 Assist Techniques: An Overview       11         2.3 Subthreshold SRAM Design Challenges       13         3 Energy Efficient Subthreshold SRAM Design for an ULP BSN       19         3.1 Introduction       19         3.2 Research Approach       21         3.3 Technology Consideration: Deeply Depleted Channel       23         3.3.1 DDC Technology Advantages and Low-Power Optimization       24         3.3.2 Body Biasing: Leakage Minimization and Reliability Challenge       26         3.3.3 Results       30         3.4 Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1 Comparison of Evaluation Metrics       36         3.4.2 Results <td></td> <td>1.1</td> <td>Motivation</td> <td>1</td> |          | 1.1   | Motivation                                                              | 1    |

| 1.3.1Background51.3.2Subthreshold SRAM for ULP Body Sensor Node51.3.3SRAM $V_{MIN}$ Tracking using Canary and Optimal Assist Selection61.3.4Reliability at Ultra-Low Voltage Operation61.3.5Conclusions72Background82.1Basic Operations92.1.1Write Operations92.1.2Read Operations92.1.3Hold Operations102.1.3Hold Operations112.4Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 1.2   | Thesis Statement                                                        | 4    |

| 1.3.2Subtreshold SRAM for ULP Body Sensor Node51.3.3SRAM $V_{MIN}$ Tracking using Canary and Optimal Assist Selection61.3.4Reliability at Ultra-Low Voltage Operation61.3.5Conclusions72Background82.1Basic Operations92.1.1Write Operations92.1.2Read Operations92.1.3Hold Operations102.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 1.3   | Dissertation Organization                                               | 5    |

| 1.3.3SRAM $V_{MIN}$ Tracking using Canary and Optimal Assist Selection61.3.4Reliability at Ultra-Low Voltage Operation61.3.5Conclusions7 <b>2</b> Background82.1Basic Operations92.1.1Write Operations92.1.2Read Operations102.1.3Hold Operations102.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges13 <b>3</b> Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |       | 1.3.1 Background                                                        | 5    |

| 1.3.4       Reliability at Ultra-Low Voltage Operation       6         1.3.5       Conclusions       7         2       Background       8         2.1       Basic Operations       9         2.1.1       Write Operations       9         2.1.2       Read Operations       9         2.1.3       Hold Operations       10         2.1.3       Hold Operations       11         2.2       Assist Techniques: An Overview       11         2.3       Subthreshold SRAM Design Challenges       13         3       Energy Efficient Subthreshold SRAM Design for an ULP BSN       19         3.1       Introduction       19         3.2       Research Approach       21         3.3       Technology Consideration: Deeply Depleted Channel       23         3.3.1       DDC Technology Advantages and Low-Power Optimization       24         3.3.2       Body Biasing: Leakage Minimization and Reliability Challenge       26         3.3.3       Results       30         3.4       Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1       Comparison of Evaluation Metrics       36         3.4.2       Results       45         3.5       E                                                                                                                                                 |          |       | 1.3.2 Subthreshold SRAM for ULP Body Sensor Node                        | 5    |

| 1.3.5Conclusions72Background82.1Basic Operations92.1.1Write Operations92.1.2Read Operations102.1.3Hold Operations102.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |       | 1.3.3 SRAM $V_{MIN}$ Tracking using Canary and Optimal Assist Selection | 6    |

| 2Background82.1Basic Operations92.1.1Write Operations92.1.2Read Operations102.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |       | 1.3.4 Reliability at Ultra-Low Voltage Operation                        | 6    |

| 2.1       Basic Operations       9         2.1.1       Write Operations       9         2.1.2       Read Operations       10         2.1.3       Hold Operations       11         2.2       Assist Techniques: An Overview       11         2.3       Subthreshold SRAM Design Challenges       13         3       Energy Efficient Subthreshold SRAM Design for an ULP BSN       19         3.1       Introduction       19         3.2       Research Approach       21         3.3       Technology Consideration: Deeply Depleted Channel       23         3.3.1       DDC Technology Advantages and Low-Power Optimization       24         3.3.2       Body Biasing: Leakage Minimization and Reliability Challenge       26         3.3.3       Results       30         3.4       Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1       Comparison of Evaluation Metrics       36         3.4.2       Results       45         3.5       Enabling the Next Generation BSNs SoC       47                                                                                                                                                                                                                                                                                                  |          |       | 1.3.5 Conclusions                                                       | 7    |

| 2.1       Basic Operations       9         2.1.1       Write Operations       9         2.1.2       Read Operations       10         2.1.3       Hold Operations       11         2.2       Assist Techniques: An Overview       11         2.3       Subthreshold SRAM Design Challenges       13         3       Energy Efficient Subthreshold SRAM Design for an ULP BSN       19         3.1       Introduction       19         3.2       Research Approach       21         3.3       Technology Consideration: Deeply Depleted Channel       23         3.3.1       DDC Technology Advantages and Low-Power Optimization       24         3.3.2       Body Biasing: Leakage Minimization and Reliability Challenge       26         3.3.3       Results       30         3.4       Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1       Comparison of Evaluation Metrics       36         3.4.2       Results       45         3.5       Enabling the Next Generation BSNs SoC       47                                                                                                                                                                                                                                                                                                  | <b>2</b> | Bac   | ckground                                                                | 8    |

| 2.1.1Write Operations92.1.2Read Operations102.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |       | -                                                                       | 9    |

| 2.1.2Read Operations102.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |       |                                                                         | 9    |

| 2.1.3Hold Operations112.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       | -                                                                       | 10   |

| 2.2Assist Techniques: An Overview112.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |       | •                                                                       | 11   |

| 2.3Subthreshold SRAM Design Challenges133Energy Efficient Subthreshold SRAM Design for an ULP BSN193.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 2.2   | 1                                                                       | 11   |

| 3.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       | -                                                                       |      |

| 3.1Introduction193.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3        | Ene   | ergy Efficient Subthreshold SBAM Design for an ULP BSN                  | 19   |

| 3.2Research Approach213.3Technology Consideration: Deeply Depleted Channel233.3.1DDC Technology Advantages and Low-Power Optimization243.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -        |       |                                                                         |      |

| 3.3       Technology Consideration: Deeply Depleted Channel       23         3.3.1       DDC Technology Advantages and Low-Power Optimization       24         3.3.2       Body Biasing: Leakage Minimization and Reliability Challenge       26         3.3.3       Results       30         3.4       Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1       Comparison of Evaluation Metrics       36         3.4.2       Results       45         3.5       Enabling the Next Generation BSNs SoC       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | -     |                                                                         |      |

| 3.3.1DDC Technology Advantages and Low-Power Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |       |                                                                         |      |

| 3.3.2Body Biasing: Leakage Minimization and Reliability Challenge263.3.3Results303.4Optimizing SRAM Bitcell Energy and Reliability343.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 0.0   |                                                                         |      |

| 3.3.3       Results       30         3.4       Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1       Comparison of Evaluation Metrics       36         3.4.2       Results       45         3.5       Enabling the Next Generation BSNs SoC       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |       |                                                                         |      |

| 3.4       Optimizing SRAM Bitcell Energy and Reliability       34         3.4.1       Comparison of Evaluation Metrics       36         3.4.2       Results       45         3.5       Enabling the Next Generation BSNs SoC       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |       |                                                                         |      |

| 3.4.1Comparison of Evaluation Metrics363.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 3.4   |                                                                         |      |

| 3.4.2Results453.5Enabling the Next Generation BSNs SoC47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 0.1   |                                                                         |      |

| 3.5 Enabling the Next Generation BSNs SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |       | •                                                                       |      |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 3.5   |                                                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 0.0   | 3.5.1 SRAM Architecture                                                 | 49   |

| 3.5.2 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |       |                                                                         |      |

|              | 3.6          | Conclusions                                                              | 54       |  |

|--------------|--------------|--------------------------------------------------------------------------|----------|--|

| 4            | SRA<br>niqu  | AM $V_{MIN}$ Tracking and Selection of an Energy Optimal Assist Techne   | ı-<br>56 |  |

|              | 4.1          | Introduction                                                             | 56       |  |

|              | 4.2          | Research Approach                                                        | 58       |  |

|              | 4.3          | Improving Reliability and Energy Requirements of subthreshold SRAM using |          |  |

|              |              | Assist Techniques                                                        | 59       |  |

|              |              | 4.3.1 Reliability Improvement                                            | 60       |  |

|              |              | 4.3.2 Energy Consideration                                               | 65       |  |

|              |              | 4.3.3 Results                                                            | 67       |  |

|              | 4.4          | Self-Tunable Wide-Range SRAM using Assist Controller                     | 72       |  |

|              |              | 4.4.1 System Architecture                                                | 72       |  |

|              |              | 4.4.2 Assist Controller                                                  | 75       |  |

|              |              | 4.4.3 Results                                                            | 77       |  |

|              | 4.5          | Conclusions                                                              | 79       |  |

| <b>5</b>     | Reli         | ability at Ultra-Low Voltage Operation                                   | 82       |  |

| -            | 5.1          | Introduction                                                             | 82       |  |

|              | 5.2          | Research Approach                                                        | 85       |  |

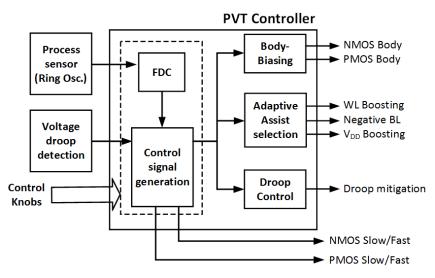

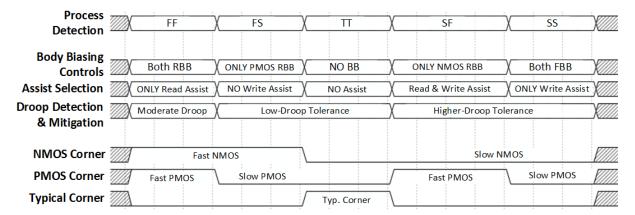

|              | 5.3          | Adapting PVT Variation using Digital Controller                          | 86       |  |

|              |              | 5.3.1 Variation: Impact and Mitigation                                   | 87       |  |

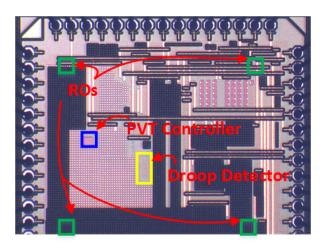

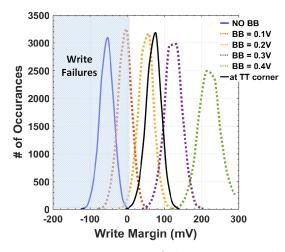

|              |              | 5.3.2 Results                                                            | 91       |  |

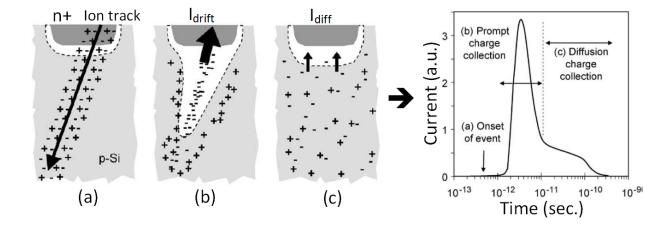

|              | 5.4          | Soft Errors: Reliability Challenges at Ultra-Low Voltage                 | 97       |  |

|              |              | 5.4.1 Theory and Mechanism Behind the Single Event Upset (SEU)           | 98       |  |

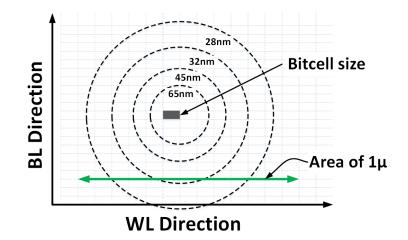

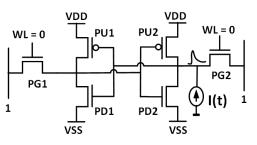

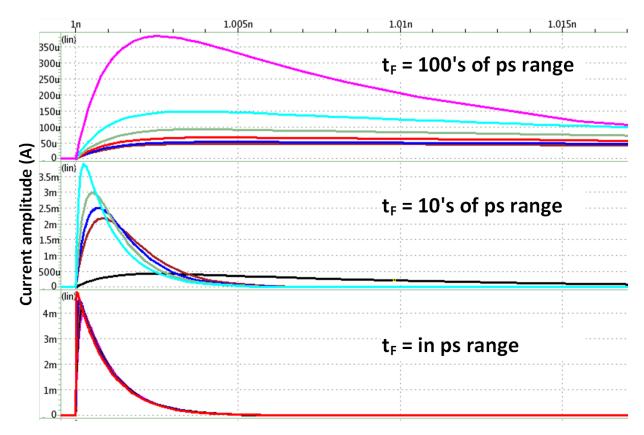

|              |              | 5.4.2 Simulation Setup                                                   | 100      |  |

|              |              | 5.4.3 Results                                                            | 102      |  |

|              | 5.5          | Conclusion                                                               | 105      |  |

| 6            | Con          | clusions                                                                 | 107      |  |

| U            | 6.1          | Summary of Contributions                                                 | 107      |  |

|              | -            | Conclusions and Open Problems                                            | 111      |  |

|              |              |                                                                          | ***      |  |

| A            | open         | dices                                                                    | 114      |  |

| $\mathbf{A}$ | Pub          | lications                                                                | 115      |  |

| в            | Acr          | onyms                                                                    | 118      |  |

| Bi           | Bibliography |                                                                          |          |  |

# List of Tables

| Different Bitcells with device type mapping                                                          | 35                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                      | 37                                                                                                                                                                                                                                                                                                                                              |

| Design specifications and features of the proposed SRAM macro $\ \ldots \ \ldots \ \ldots$           | 48                                                                                                                                                                                                                                                                                                                                              |

| Applied percentage of assist vs. biasing voltage mapping                                             | 61                                                                                                                                                                                                                                                                                                                                              |

| Achievable $V_{MIN}$ for different assist techniques                                                 | 64                                                                                                                                                                                                                                                                                                                                              |

| Range of $V_{DD}$ s and applied assist for a reliable SRAM operation for different assist techniques | 64                                                                                                                                                                                                                                                                                                                                              |

| Selection algorithm for the supply voltage tuning (using LDO) and correspond-                        |                                                                                                                                                                                                                                                                                                                                                 |

| ing assist selection.                                                                                | 76                                                                                                                                                                                                                                                                                                                                              |

| Comparison of proposed Canary-based close loop SRAM sub-system with                                  |                                                                                                                                                                                                                                                                                                                                                 |

| present state-of-the-art work.                                                                       | 81                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                      | Applied percentage of assist vs. biasing voltage mapping $\ldots$ Achievable $V_{MIN}$ for different assist techniques $\ldots$ Range of $V_{DD}$ s and applied assist for a reliable SRAM operation for different assist techniques $\ldots$ Selection algorithm for the supply voltage tuning (using LDO) and corresponding assist selection. |

# List of Figures

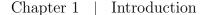

| 1.1          | Power consumption of present state of the art ULP SoCs (a) $[1]$ (b) $[2]$                                                                                           | 3               |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

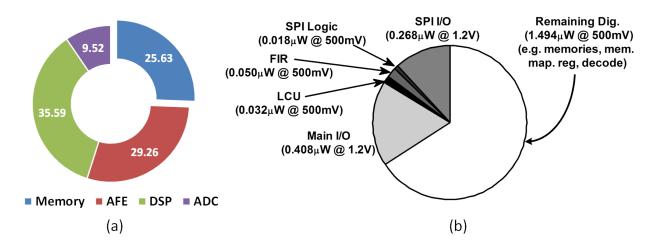

| $2.1 \\ 2.2$ | Conventional SRAM Bitcells                                                                                                                                           | 9<br>10         |

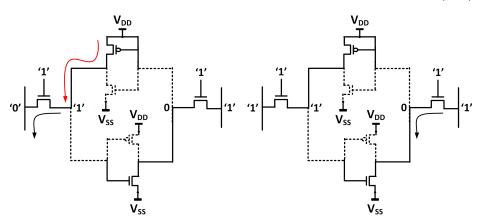

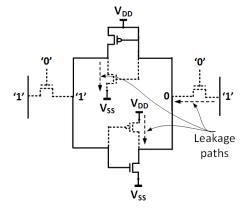

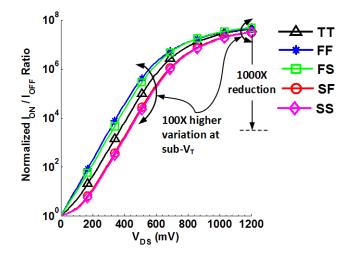

| 2.3          | Write Assist Techniques: a) $V_{DD}$ Lowering, b) $V_{SS}$ Raising, c) Wordline (WL)<br>Boosting and d) Negative bitline (NegBL); Read Assist Technique: e) $V_{DD}$ |                 |

| 2.4          | Boosting                                                                                                                                                             | $12 \\ 15$      |

| 2.5          | Impact of process variation on SRAM $V_{MIN}$ scaling                                                                                                                | 15              |

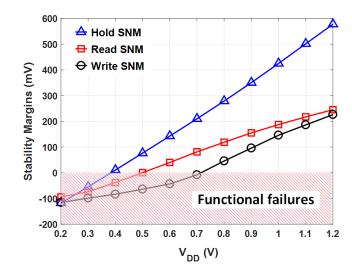

| 2.6          | Reduced stability margins at scaled $V_{DD}$                                                                                                                         | 16              |

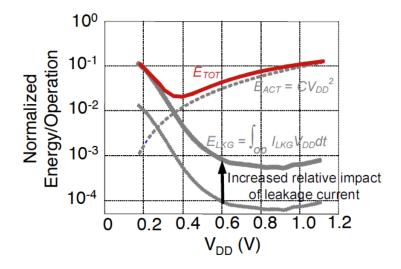

| 2.7          | Relative increase in leakage power dominance in sub-theshold: An SRAM                                                                                                |                 |

| 0.0          | contribution [3]                                                                                                                                                     | 17              |

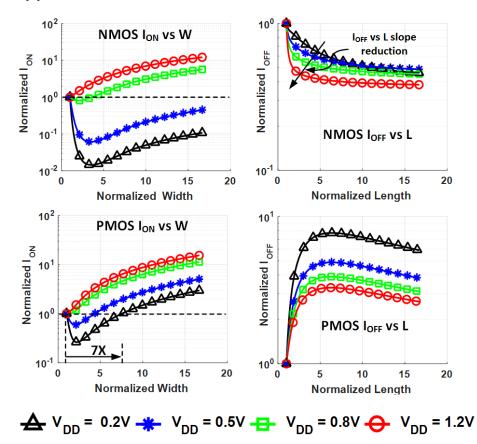

| 2.8          | Device sizing becomes a less effective knob for increasing $I_{ON}$ in subthreshold (130nm technology)                                                               | 17              |

|              | (150mm technology)                                                                                                                                                   | 11              |

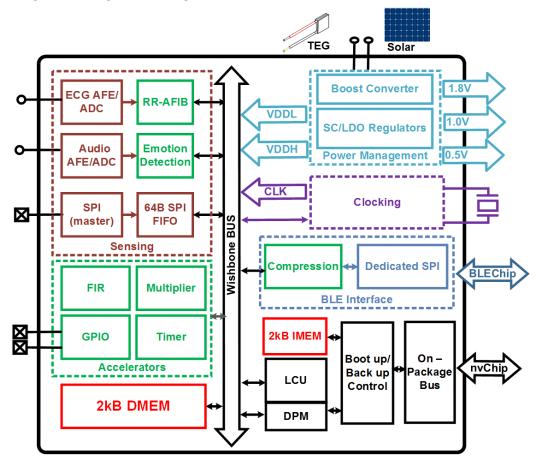

| 3.1          | Block diagram of SoC showing harvesting system, memories, sensing modalities,                                                                                        |                 |

| 0.0          | accelerators, cold-boot management, and radio interface [4].                                                                                                         | 20              |

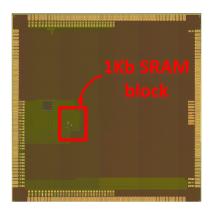

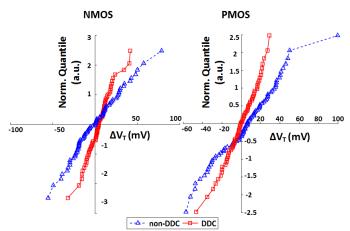

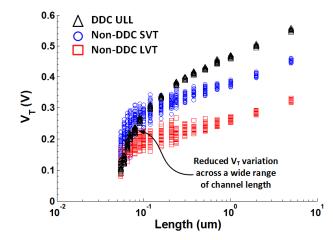

| $3.2 \\ 3.3$ | Fabricated testchip with 1Kb SRAM $\dots \dots \dots$                | $\frac{24}{25}$ |

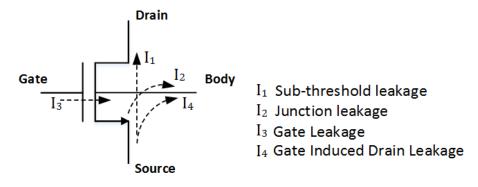

| 3.3<br>3.4   | Major contributing leakage currents $\ldots \ldots \ldots$                                            | $\frac{25}{27}$ |

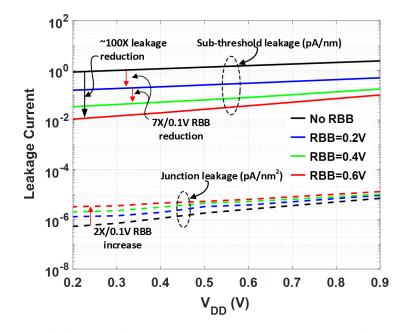

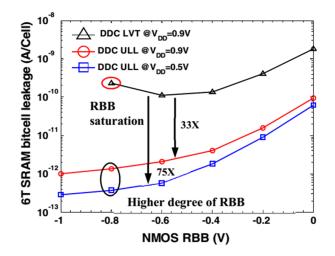

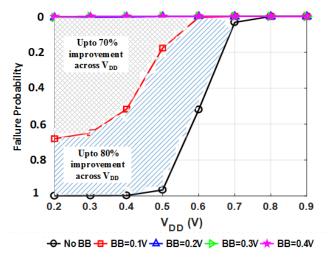

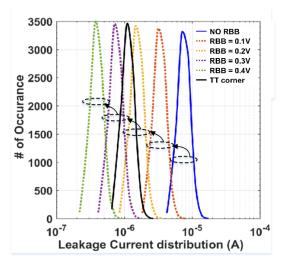

| 3.5          | Effective leakage reduction using RBB — Increasing degree of RBB reduces                                                                                             | 21              |

|              | subthreshold leakage by 100X while increases junction current increases by                                                                                           |                 |

|              | less than 10X across supply voltages                                                                                                                                 | 28              |

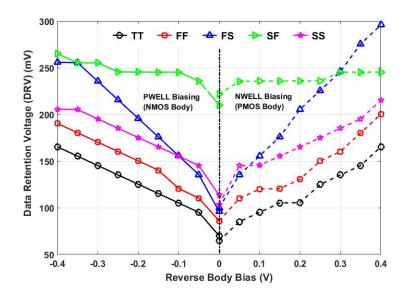

| 3.6          | Reduced ON current increases DRV that leads towards a higher standby current                                                                                         | 28              |

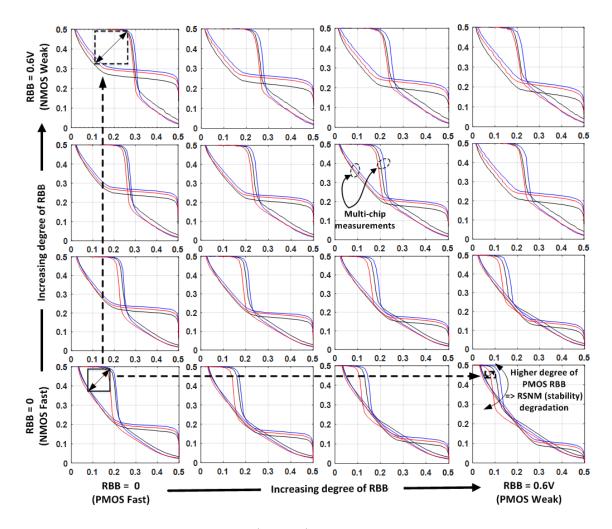

| 3.7          | Read Static Noise Margin (RSNM) of the 6T bitcell at different combinations                                                                                          | 00              |

| 3.8          | of PMOS and NMOS body biasing                                                                                                                                        | 29              |

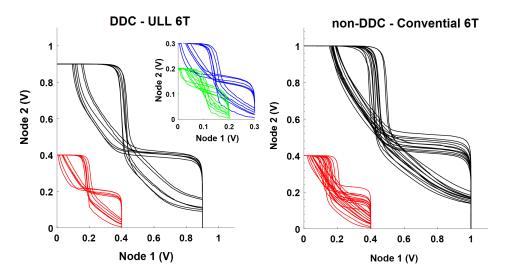

| <b>J</b> .0  | degree of RBB                                                                                                                                                        | 31              |

| 3.9          | Butterfly curves for SRAM 6T bitcell: DDC ULL vs. non-DDC (conventional)                                                                                             | 01              |

|              | bitcell                                                                                                                                                              | 31              |

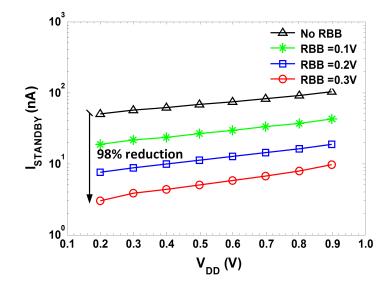

| 3.10         | Standby leakage of fabricated 1kb SRAM macro reduction with different                                                                                                |                 |

|              | degrees of reverse body-biasing                                                                                                                                      | 32              |

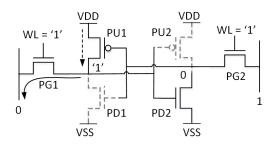

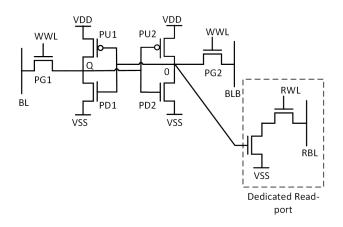

|              | 6T SRAM bitcell: Write-0 operation                                                                                                                                   | 33              |

|              | Impact of RBB on functional yield improvement                                                                                                                        | 33<br>34        |

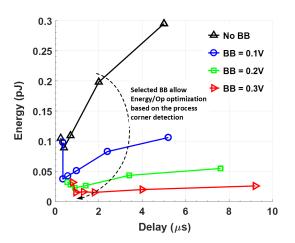

| 0.10         | Sitam energy and performance optimization using DDC OLL devices and RDD.                                                                                             | 94              |

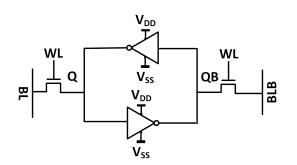

| 3.14 | 8T SRAM bitcell                                                                          | 35 |

|------|------------------------------------------------------------------------------------------|----|

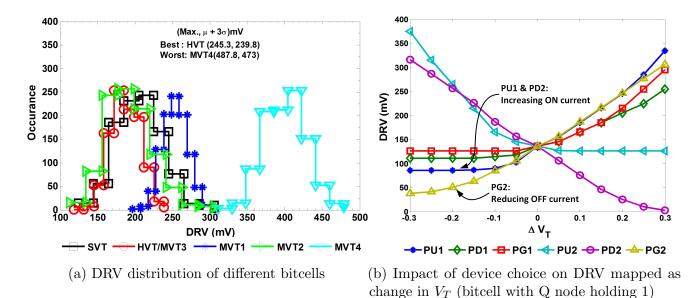

|      | Comparison of the different Bitcells for DRV                                             | 38 |

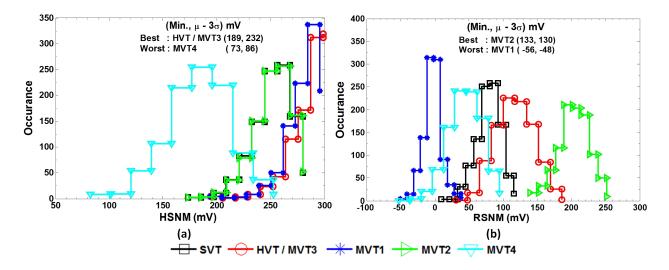

|      | Noise margin comparison: a) HSNM, b) RSNM - Distribution under local                     |    |

|      | variation and optimal choice                                                             | 39 |

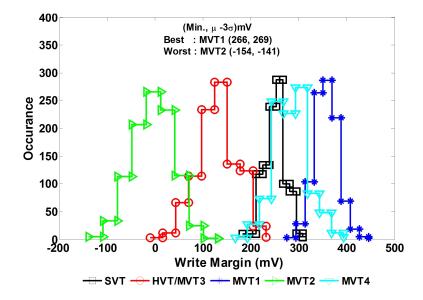

| 3.17 | WM distribution of different bitcells for $V_{DD}=0.5$ V                                 | 39 |

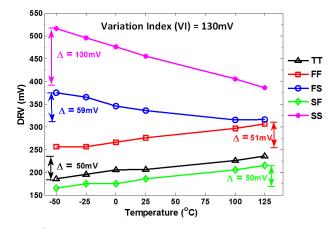

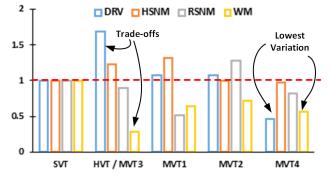

| 3.18 | Comparison of the different Bitcells under the variation                                 | 40 |

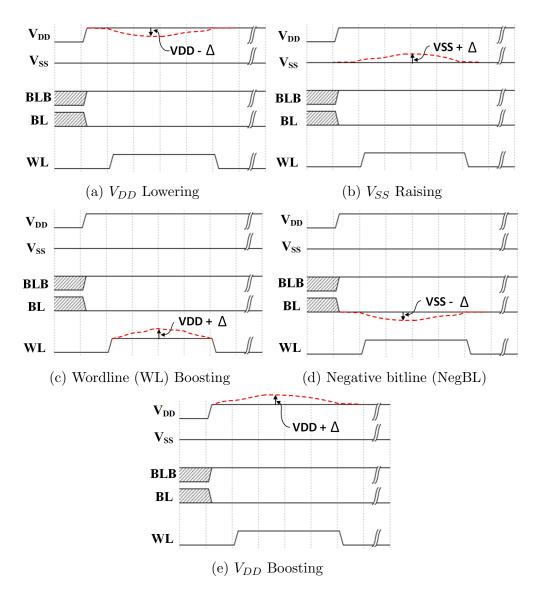

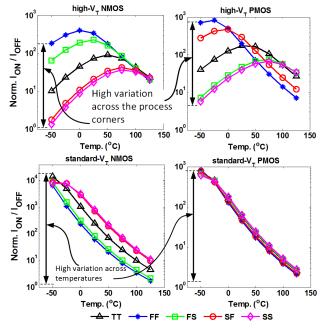

| 3.19 | Normalized $I_{ON}/I_{OFF}$ characteristics for different devices across process corners |    |

|      | and temperatures                                                                         | 42 |

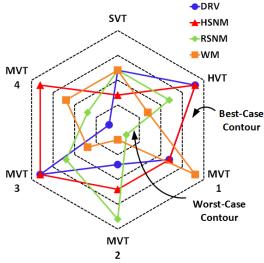

|      | Optimal Bitcell selection based on static metrics                                        | 42 |

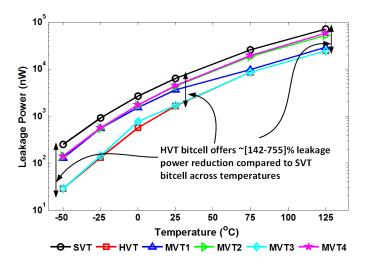

|      | Leakage power of 1KB array across temperature for different bitcells                     | 43 |

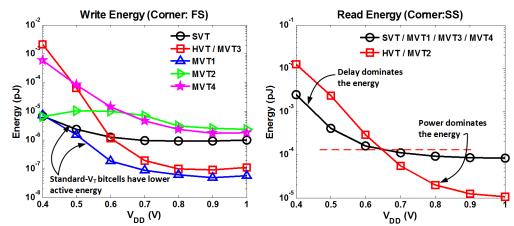

|      | Write and Read energy comparison of the different bitcells across the $V_{DD}$ s .       | 44 |

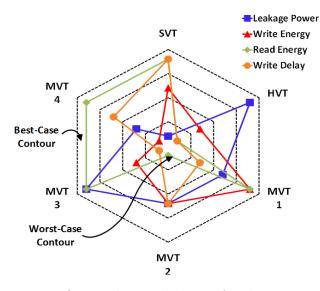

| 3.23 | Optimal Bitcell choice for dynamic metrics                                               | 45 |

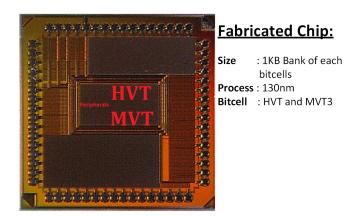

| 3.24 | Die micrograph of chip showing HVT and MVT banks                                         | 45 |

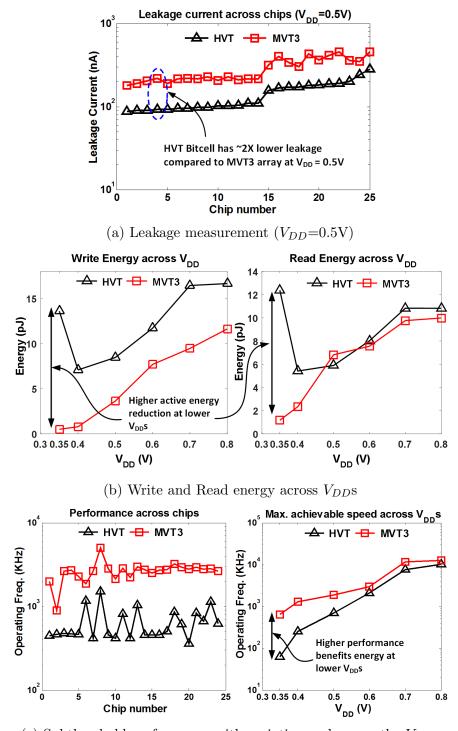

| 3.25 | Measurement result comparison between HVT and MVT3 bitcells from 24 chips                | 46 |

| 3.26 | Architecture of a low-power 2KB SRAM macro with various power management                 |    |

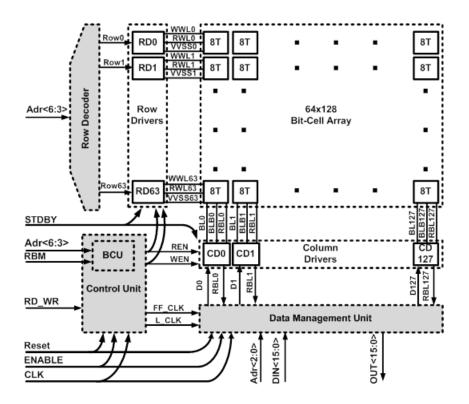

|      | schemes                                                                                  | 49 |

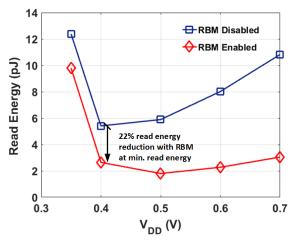

| 3.27 | Energy minimization using RBM                                                            | 51 |

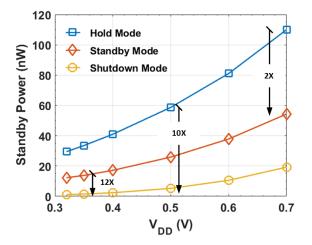

| 3.28 | Leakage power reduction using different modes: 2X leakage power reduction                |    |

|      | when data retention is required (standby mode) and 10X power saving with                 |    |

|      | data loss (shutdown mode)                                                                | 51 |

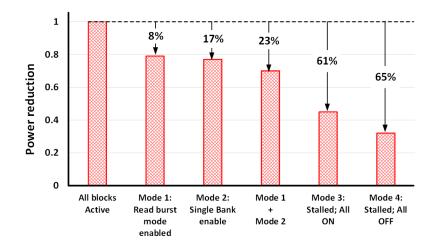

| 3.29 | System-level effectiveness of various power/energy saving techniques imple-              |    |

|      | mentation in SRAM                                                                        | 52 |

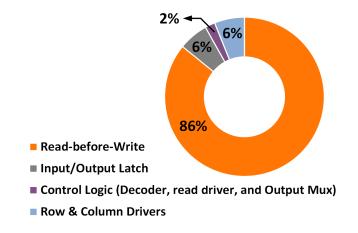

| 3.30 | Power distribution in 2KB SRAM Peripheral blocks                                         | 53 |

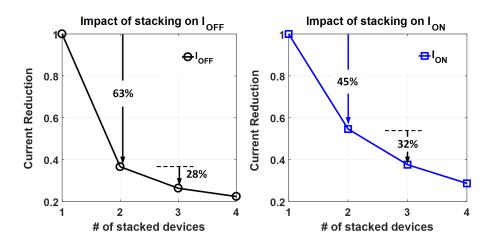

| 3.31 | Impact of increase in device stacking on $I_{ON}$ and $I_{OFF}$ currents                 | 54 |

| 0.01 |                                                                                          | -  |

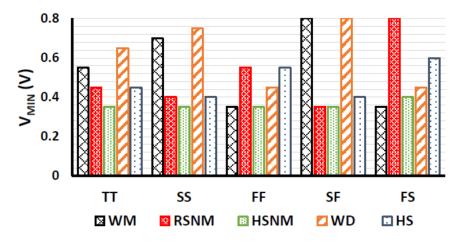

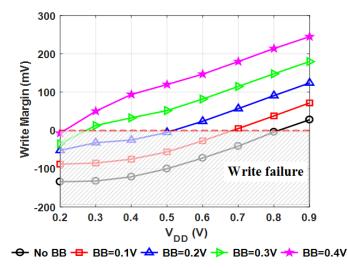

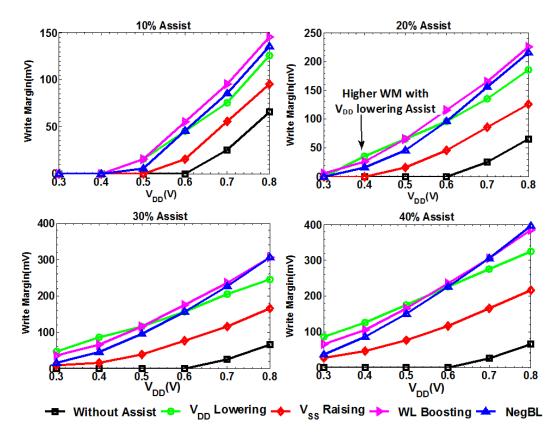

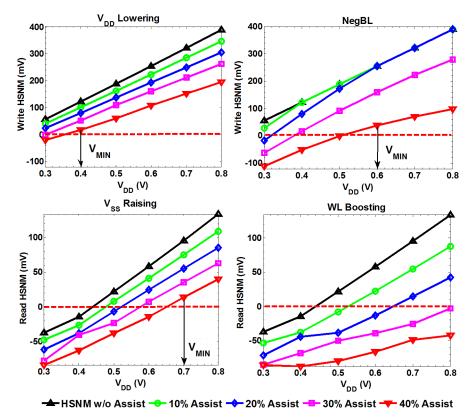

| 4.1  | Impact of different assist techniques: WM metric                                         | 61 |

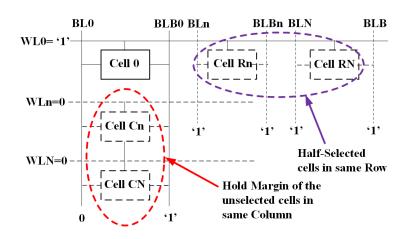

| 4.2  | Representation of an NxM array with row and column half-selected (HS) cells              | 63 |

| 4.3  | Impact of aggressive assist on Read and Write HSNM of HS cells                           | 63 |

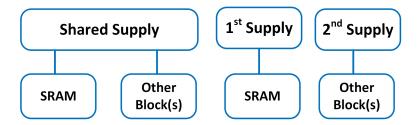

| 4.4  | System level supply voltage configuration: I) Shared supply II) Split supply             | 65 |

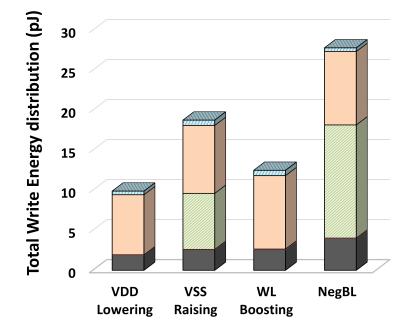

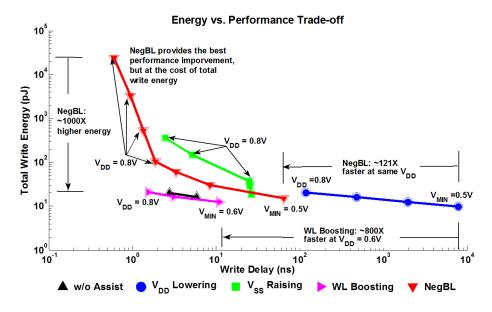

| 4.5  | Total write energy distribution across assist techniques (at array $V_{MIN}$ ) .         | 67 |

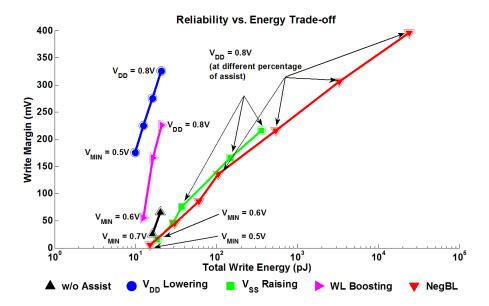

| 4.6  | WM (reliability) vs. total write energy optimal contours (EOCs) for different            |    |

|      | assist techniques at achievable $V_{MIN}$                                                | 68 |

| 4.7  | Total Write Energy vs. write delay (performance) contours for different assist           |    |

|      | techniques with achievable array $V_{MIN}$                                               | 70 |

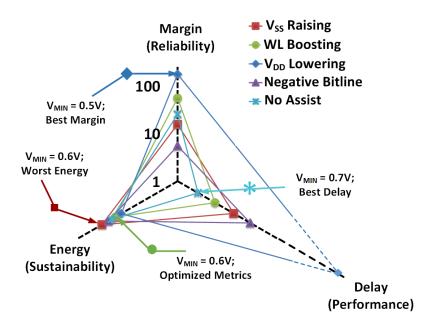

| 4.8  | Write margin - write delay - array write energy trade-offs at the lowest achiev-         |    |

|      | able $V_{MIN}$                                                                           | 71 |

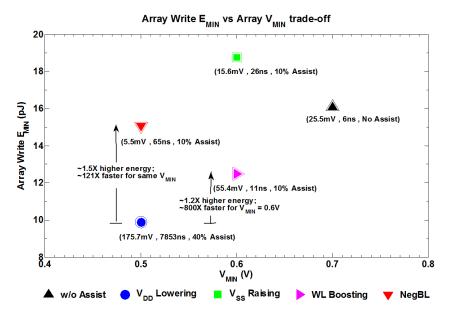

| 4.9  | Array write $E_{MIN}$ vs. Array $V_{MIN}$ for different assist techniques with achiev-   | -  |

|      | able (WM, delay, and assist)                                                             | 71 |

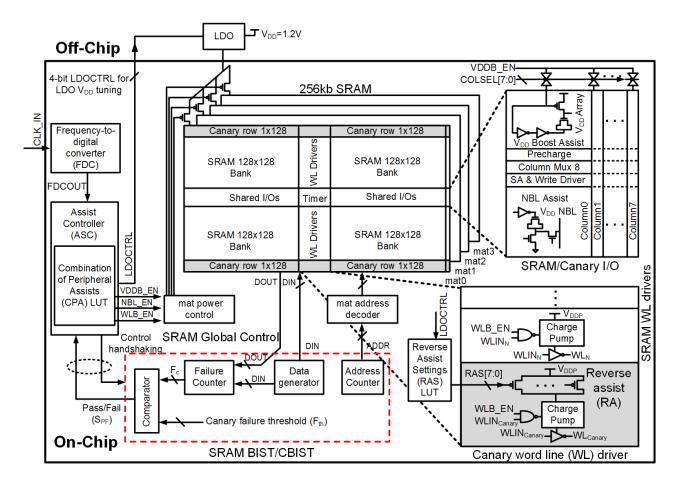

| 4.10 | Block diagram of an SRAM sub-system with adaptively tunable assist controller            |    |

| 1.10 | and other blocks                                                                         | 73 |

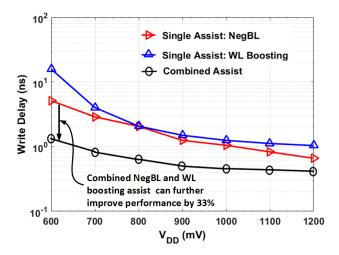

| 4 11 | Flowchart and corresponding system waveforms of the SRAM tracking and                    | 10 |

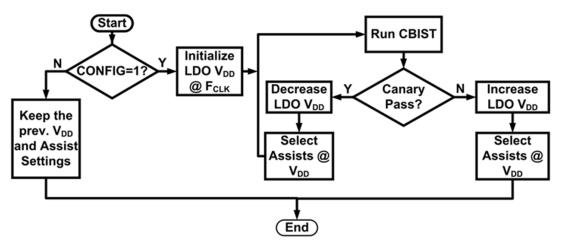

| 7,11 | assist selection using Canary SRAM.                                                      | 74 |

| 119  | Evaluating optimal assist technique for the performance enhancement at super-            | 14 |

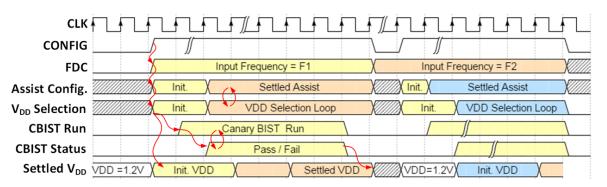

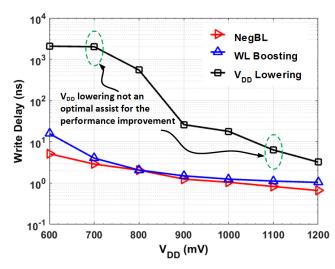

| 4.14 | threshold                                                                                | 75 |

|      |                                                                                          | 10 |

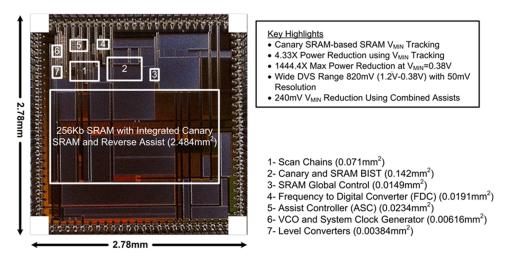

|              | Die photo of the fabricated 256kb SRAM sub-system with sub-blocks and various features of the architecture.                                                                                                                                                                                           | 78                                        |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

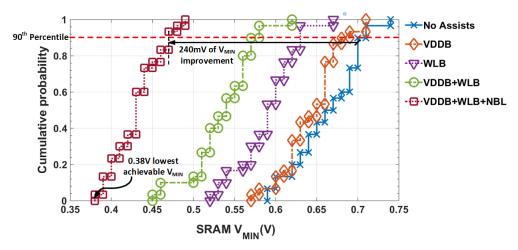

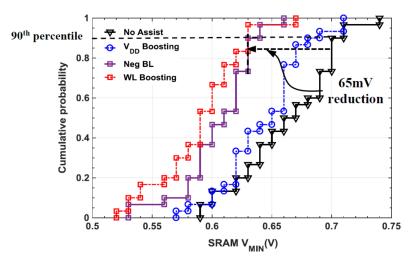

|              | Measured CDF of 256kb SRAM $V_{MIN}$ showing 90 <sup>th</sup> percentile $V_{MIN}$ improvement of 240mV using combined assists of VDDB, WLB, and NBL                                                                                                                                                  | 78                                        |

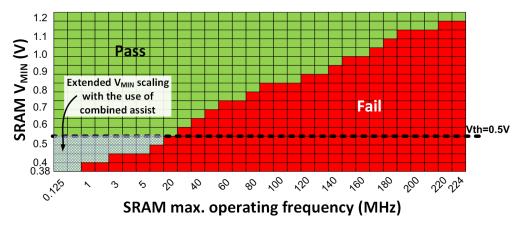

| 4.15         | Measured Shmoo plot highlighting a wide range of operation over frequency<br>and $V_{DD}$                                                                                                                                                                                                             | 78                                        |

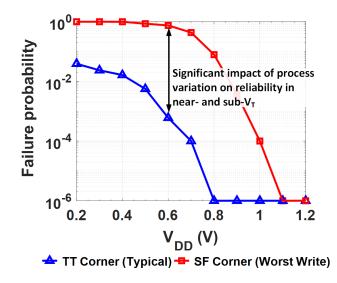

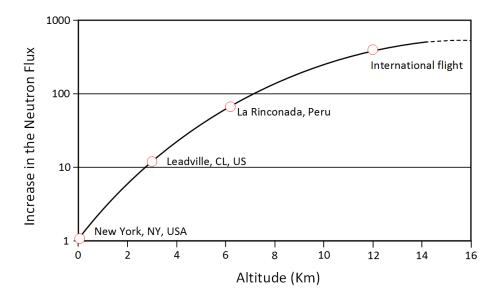

| 5.1<br>5.2   | Impact of process variation on reliability with $V_{DD}$ scaling Increase in Neutron Flux increase with altitude. Highest altitude place in the earth (La Rinconada, Peru with ~6Km) experiences ~100X higher flux while the international flight achieving 39000ft (~12Km) has ~500X greater risk of | 83                                        |

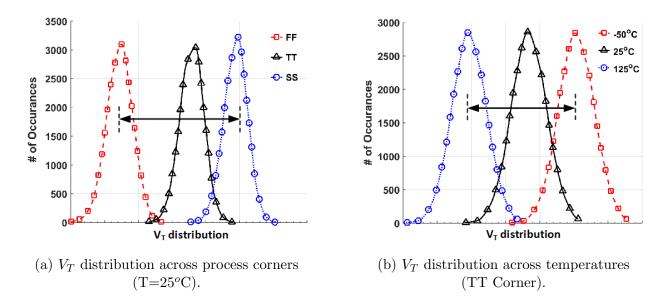

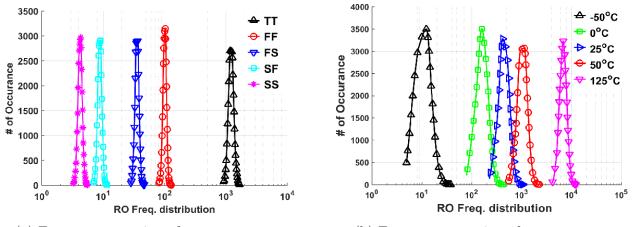

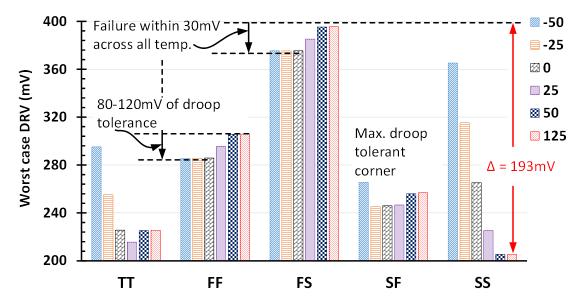

| 5.3          | particle strike then New York City, NY, USA. [5] $\ldots$ Process and temperature variation in device $V_T$ . The plots show distribution                                                                                                                                                             | 84                                        |

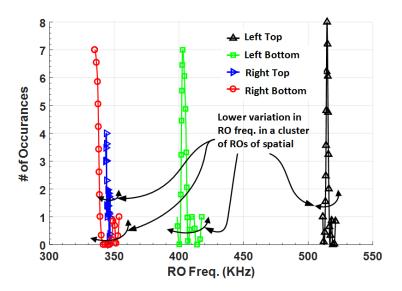

| $5.4 \\ 5.5$ | of 10000 point Monte Carlo simulations at given process corner and temperature.<br>Process and temperature mapping by detection of the different frequencies<br>Impact of Intra-die variation: Due to spatial variation (blocks placed at each                                                        | 88<br>89                                  |

|              | corner of the chip), the measured frequency of 16 ROs varies from 300KHz to $500$ KHz at $V_{DD}=0.4$ V                                                                                                                                                                                               | 89                                        |

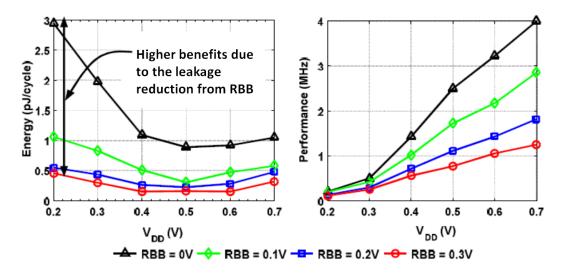

| 5.6          | Evaluating optimal assist technique for the performance enhancement at super-<br>threshold                                                                                                                                                                                                            | 90                                        |

| 5.7          | Die photo of the fabricated chip with PVT controller, ROs as the process sensor, and droop detection sensors                                                                                                                                                                                          | 91                                        |

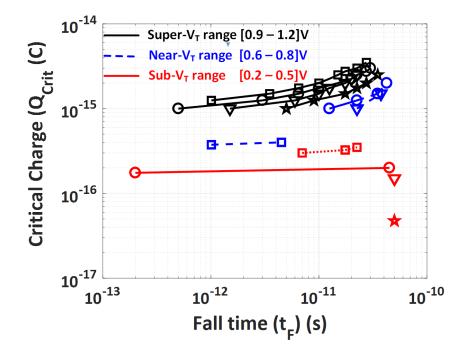

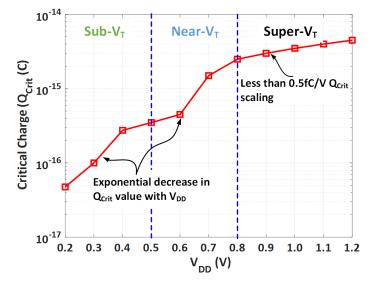

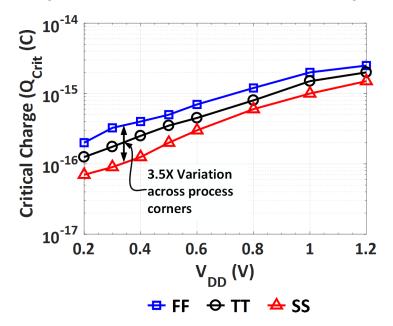

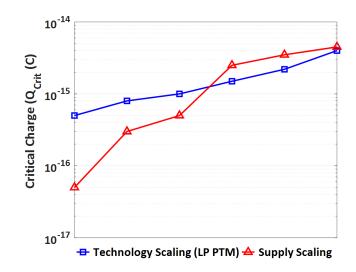

| 5.8          | Effectiveness of PVT based body-bias control on a) Reliability (Write margin),<br>b) Leakage (Power), and c) Energy (Energy per operation)                                                                                                                                                            | 93                                        |