# Modular Battery Management System (BMS)

Dipesh Manandhar, Nripesh Manandhar, Phillip Phan, Nikilesh Subramaniam and William Zhang

12/10/20

Capstone Design ECE 4440 / ECE4991

Signatures

Dipesh Manandhar

Nripssh Manandhar

Phillip Phan

Nikilech Subramaniam

Millian Hrang

## Statement of work:

#### Dipesh Manandhar

I primarily worked on the system design for both the hardware and software, as well as laying out the Cell Node board and setting up the software development environment. I designed the initial drafts of the system diagrams for both Main Node and Cell Node hardware, as well as software flow charts for both. I helped Nripesh set up some of the hierarchical sub-schematics, including the CAN transceivers and the MCUs. Major design changes during the design phase, prior to any PCB fabrication, did result in changes to the hardware system diagrams, and I was responsible for keeping track of all such changes and updating the system diagrams appropriately.

I also set up the software development environment for both Main node and Cell Node, as I had the most experience working with the tools we were using. This included setting up the PlatformIO toolchain and project files, Mbed OS custom target files, and debugging and testing environments to use for both our custom PCBs and the NUCLEO development boards. I also contributed to integrating the code Phillip and Niki wrote for the SOC and SOH calculations, fan logic, and balancing logic into the software for the Main Node, as well as writing the functions for reading the pack voltage and current. After we realized the issue with the pack voltage and current sensor accuracies, I handled the hardware and software changes necessary to reduce the range on these sensors.

### Nripesh Manandhar

I primarily worked on designing the hardware schematics in KiCad for both the Cell Node and Main Node, as well as laying out the Main Node board. I set up all the KiCad component libraries for schematic symbols and footprints of real components not included in KiCad. I also designed the hierarchical structure of the schematics. I designed most of the subschematics for the Main Node and Cell Node, with help from Niki and Dipesh on some of the sub-schematics, such as the temperature sensor on the Cell Node and setting up the MCUs. Most major design decisions were made as a team, such as changing the power supply schematics to always use the external supplies rather than the batteries themselves. However, I made a lot of the decisions on specific components to use, such as the specific regulators in the power supply schematics.

After the first iteration of the hardware was tested, I made most of the modifications to the Cell Node's schematics and layout. I also added LEDs to the Cell Node for ease of debugging. After the hardware was finalized, I also helped write some of the software, especially for the Cell Node. I wrote some of the shared code between Cell Node and Main Node such as the CAN structs used for communication between the Cell Nodes and the Main Node, but I mostly wrote code for the Cell Node specifically. This included setting up the main loop to read

voltage and temperature inputs and setting up the background threads for CAN Rx and Tx. I also performed the final demonstration of the project, with the help of Dipesh who recorded the video, showing all the various functionality of the modular BMS.

### Phillip Phan

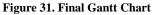

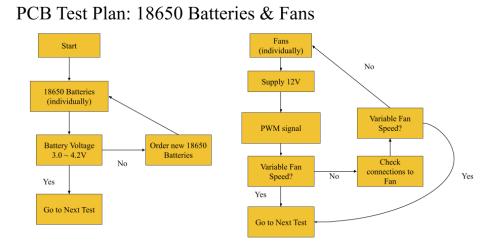

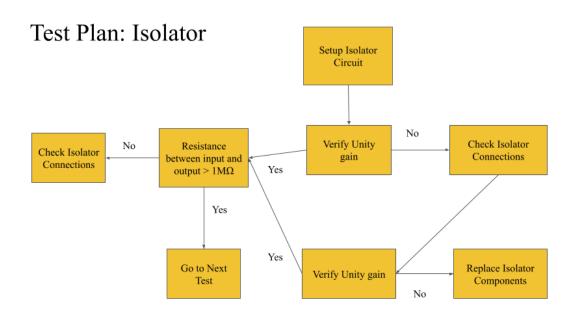

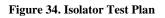

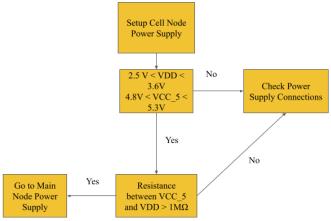

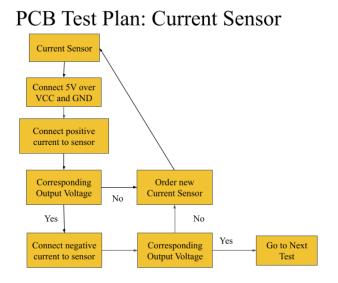

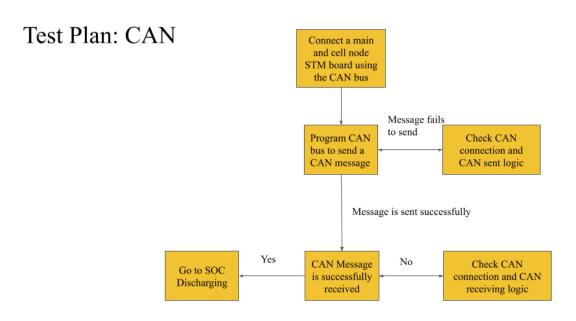

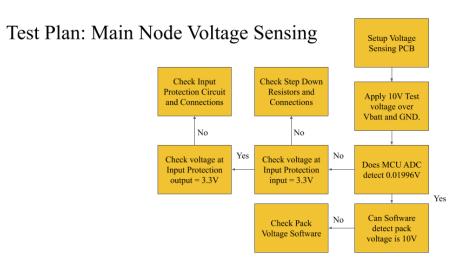

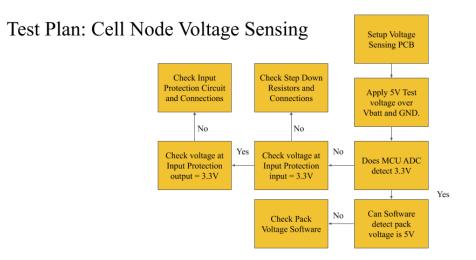

For the modular BMS, I primarily worked on testing the boards and on designing the software for SOC and SOH estimation. I designed the testing methodology for the modular BMS so that the hardware components for the BMS system were tested first individually before doing integration testing with the combined hardware components. The software components in the modular BMS were tested afterwards. I also created diagrams for the hardware and software test plans, which present the test plan in a form of a decision tree to enable the person testing the modular BMS to know what steps to take.

In testing the main and cell boards, I first verified that the hardware components of the modular BMS functioned correctly through voltage and resistance measurements with Niki. Afterwards, Niki and I wrote test programs to verify that the readings from sensors were correct, and verify that components like the relays were controllable through software. When I was designing the software for the modular BMS, I had to conduct extensive research to weigh the pros and cons of various SOC estimation methods before deciding on our chosen SOC estimation method. I also researched various methods to calculate the error from using our chosen SOC estimation method. Additionally, I helped assemble and solder the through hole components onto the main and cell PCBs with William.

### Nikilesh Subramaniam

For this project, I worked on researching cell balancing methods and pack health algorithms. Initially, I looked for active cell balancing schematics that could transfer charge between battery cells to equalize their charge. After some more research and simulating an active cell balancing, I opted for the simpler passive cell balancing circuit because it was simpler. I also researched algorithms for pack health estimation. Initially, I researched a method to use the Kalman filter to estimate state of charge (SOC) and state of health (SOH), but we ended up going with the Coulomb counting method that Phillip researched. I implemented our chosen estimation algorithm in software.

Additionally, I wrote some software for testing and logic. For testing, I wrote small test programs to instantiate GPIO pins and read or write from then. I worked with Phillip to test these GPIO pins such as the analog input to read pack voltage and pack current and the digital output to control cell balancing. Additionally, along with SOC estimation, I helped with main board logic such as fan control and cell balancing.

#### William Zhang

I worked on multiple different aspects of the project, helping out with different areas when needed. In the initial stages of the modular BMS project, I worked on research for the component selection, such as the microcontroller. Initially, I did extensive research on the available hardware options for the microcontrollers for both the main node and cell node, based on the requirements of each. I evaluated the pricing, package, onboard peripherals, power consumption, and software stack for each of the options and helped the team come to a decision on final component selection.

For each round of PCB send outs, once the team received the manufactured PCBs, I organized, prepared, and took the components to be populated by WWW Electronics. Once WWW finished populating the SMD components and I picked up the boards, I worked with Phillip to solder the remaining components and assemble them.

I additionally worked with Phillip and Niki on debugging the boards. With the main node board, I worked with Phillip and Niki to debug the issues we were having with the microcontroller being constantly held in reset, preventing code from being uploaded to the board. I researched different hardware and software solutions, which we tried one by one. When running the software tests on the cell node, I worked with Phillip and Niki to resolve issues with the code failing to print to the serial console properly and the ADC failing to initialize properly. I researched different Mbed target configuration options and other toolchains and tested them to try to resolve the issue.

In addition, I worked with Dipesh on setting up, testing, and debugging the embedded software toolchain and build process, particularly for the main node. I generated and collated the necessary target header and source files from the HAL libraries provided by ST Microelectronics for the toolchain to build for the STM32G473 microcontroller on the main node.

Finally, I also worked on the PC program as the external interface for the modular BMS. I wrote the CAN bridge program in Rust to allow CAN bus frames received on a CAN interface to be relayed over a WebSocket, to a GUI program, which I partially finished.

# **Table of Contents**

| Capstone Design ECE 4440 / ECE4991 1      |

|-------------------------------------------|

| Signatures                                |

| Statement of work:                        |

| Table of Contents                         |

| Table of Figures                          |

| Abstract                                  |

| Background                                |

| Constraints                               |

| Design Constraints                        |

| Economic and Cost Constraints9            |

| External Standards                        |

| Tools Employed                            |

| Ethical, Social, and Economic Concerns 12 |

| Environmental Impact                      |

| Sustainability                            |

| Health and Safety                         |

| Manufacturability                         |

| Ethical Issues                            |

| Intellectual Property Issues              |

| Detailed Technical Description of Project |

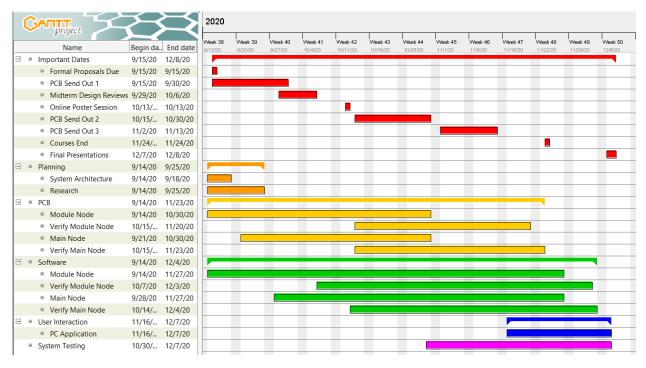

| Project Time Line                         |

| Test Plan                                 |

| Final Results                             |

| Costs                                     |

| Future Work                               |

| References                                |

| Appendix                                  |

# **Table of Figures**

(This should list the page of each figure used in your document, including the full caption.) Word has tools to help you do this very easily)

| Figure 2. Main Node Schematic16Figure 3. Main Node Power Supply Schematic17Figure 4. Main Node MCU Schematic18Figure 5. Connectors Schematic19Figure 6. Current Sensor Schematic20Figure 7. Input Protection Schematic20Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24Figure 13. Main Node PCB25 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4. Main Node MCU Schematic18Figure 5. Connectors Schematic19Figure 6. Current Sensor Schematic20Figure 7. Input Protection Schematic20Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24                                                                                                      |

| Figure 4. Main Node MCU Schematic18Figure 5. Connectors Schematic19Figure 6. Current Sensor Schematic20Figure 7. Input Protection Schematic20Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24                                                                                                      |

| Figure 6. Current Sensor Schematic20Figure 7. Input Protection Schematic20Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24                                                                                                                                                                         |

| Figure 7. Input Protection Schematic.20Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24                                                                                                                                                                                                            |

| Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24                                                                                                                                                                                                                                                   |

| Figure 8. Main Board Step Down Voltage21Figure 9. Isolation Schematic22Figure 10. Fan Control Schematic23Figure 11. Contactor Control Schematic23Figure 12. CAN Communication Schematic24                                                                                                                                                                                                                                                   |

| Figure 10. Fan Control Schematic                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 11. Contactor Control Schematic                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 12. CAN Communication Schematic                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 12. CAN Communication Schematic                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 13. Main Node PCB                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 14. Cell Node Schematic                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 15. Cell Node Power Supply Schematic                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 16. Cell Node MCU Schematic                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 17. Cell Node Connectors Schematics                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 18. Cell Node Voltage Divider                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 19. Temperature Module Schematic                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 20. Cell Balancing Schematic                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 21. Isolated CAN Schematic                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 22. Cell Board PCB                                                                                                                                                                                                                                                                                                                                                                                                                   |

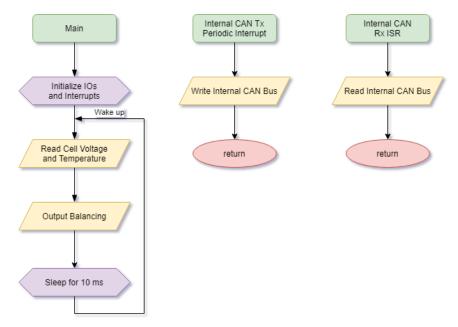

| Figure 23. Cell Node Software Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                    |

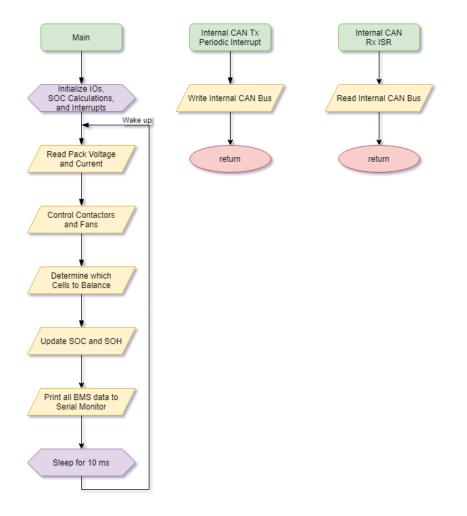

| Figure 24. Main Node Software Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                    |

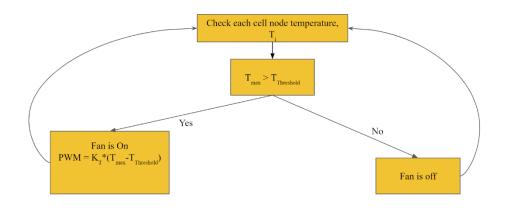

| Figure 25. Fan Software Logic                                                                                                                                                                                                                                                                                                                                                                                                               |

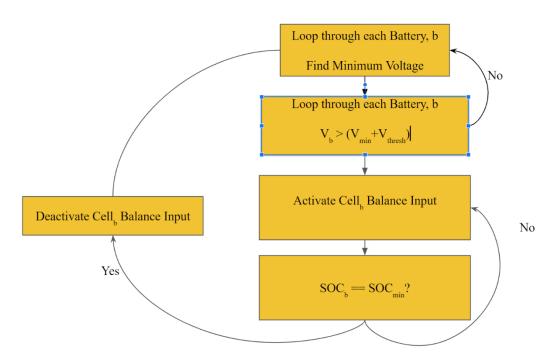

| Figure 26. Cell Balancing Logic                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 27. Voltage vs. SOC Graph for 18650 Batteries [51]                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 28. Enhanced Coulomb Counting Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 29. State Diagram of Combined Coulomb Counting and Voltage-based for SOC                                                                                                                                                                                                                                                                                                                                                             |

| Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 30. Proposal Gantt Chart                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 31. Final Gantt Chart                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 32. Battery and Fan Test Plan                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 33. Power Convertor, Reset Button and Resistor Test Plan                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 34. Isolator Test Plan                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 35. Cell Node Power Supply Test Plan                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 36. Main Node Power Supply Test Plan                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 37. Temperature Sensor Test Plan                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 38. Current Sensor Test Plan 50                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 39. CAN Test Plan                                            | 50 |

|---------------------------------------------------------------------|----|

| Figure 40. Main Node Voltage Sensing Test Plan                      | 51 |

| Figure 41. Cell Node Voltage Sensing Test Plan                      | 51 |

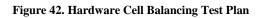

| Figure 42. Hardware Cell Balancing Test Plan                        | 52 |

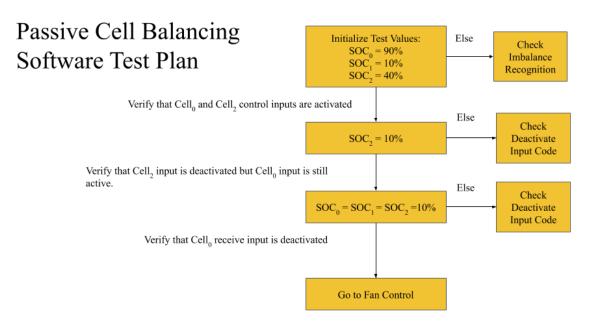

| Figure 43. Passive Cell Balancing Software Test Plan                | 52 |

| Figure 44. SOC Discharging Test Plan                                | 53 |

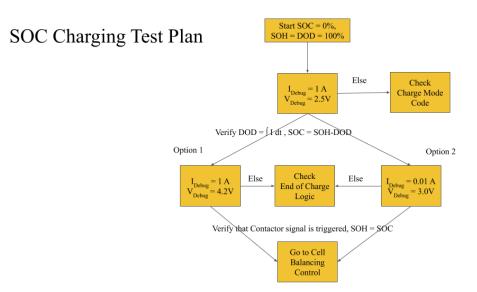

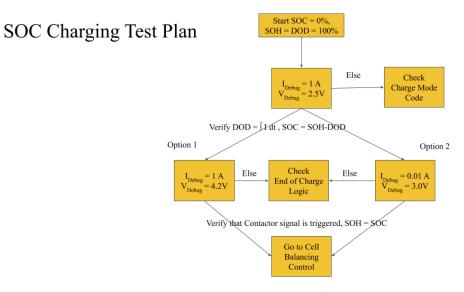

| Figure 45. SOC Charging Test Plan                                   | 53 |

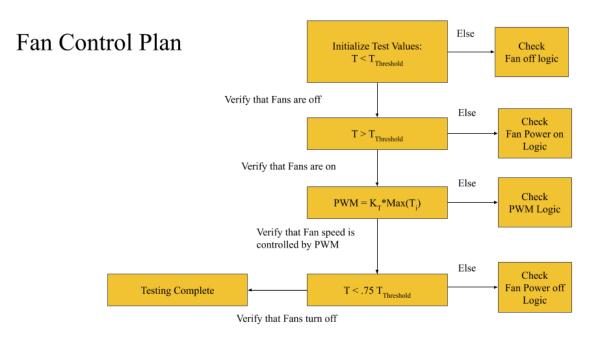

| Figure 46. Fan Control Test Plan                                    |    |

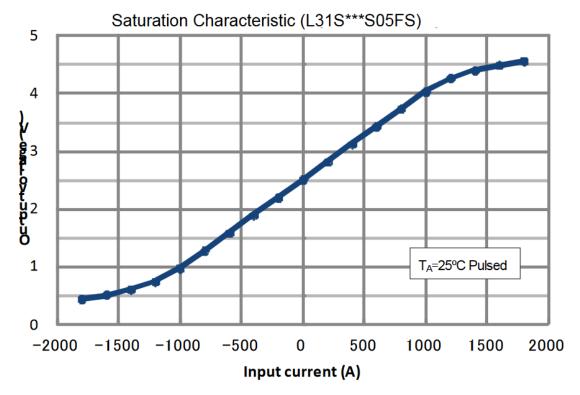

| Figure 47. Saturation Characteristic of the Hall Effect Sensor [42] | 62 |

# Abstract

This project is a battery management system (BMS) designed to monitor, protect, and efficiently use battery packs for electric vehicles. This modular system is a star network of BMS boards that is usable for battery packs of many sizes. The star network consists of a cell board for each battery cell and a main board that interacts with the cell board. The BMS has charge and discharge protection, estimates the state of charge of the battery pack, uses passive cell balancing, and has a user interface to view battery pack data. Each BMS module is small enough to clip onto 18650 cells, rechargeable lithium-ion cells that are commonly used in electric vehicles [1]. This battery management system reduces the battery space needed in electric vehicles and is easily able to adapt to different pack sizes.

# Background

Electric vehicles (EVs) have recently gained popularity as an environmentally friendly alternative to vehicles that need gas [2]. The battery is an essential component of the electric vehicle and its performance determines the driving range of EVs. A battery management system (BMS) is needed in order to prevent the battery from overcharging or supplying high currents which can deteriorate the lifetime of the battery. In addition, a BMS can report important battery information such as state of charge and extend the battery lifetime via cell balancing [3]. Many BMSs can only be used for a certain battery pack with a maximum number of cells [4]. This project proposes a modular BMS design that can handle many different pack types and sizes while still providing essential BMS services.

There have been BMS research in both academia and industry. One paper from a joint European effort detailed different battery modeling methods and cell balancing methods such as passive heat dissipation and active distributed balancing. The paper also sets standards for battery management such as system inputs, responsibilities, and possible sources of error [3]. Shandong University designed and tested a Li-ion BMS using a microcontroller that had charge and discharge protection, single cell voltage and temperature monitoring, and cell balancing. This BMS monitored 16 cells, with each group of 8 cells being monitored by a chip. This chip communicated with the microcontroller via an I<sup>2</sup>C bus [5].

A popular BMS from industry is the Orion BMS [6]. Along with BMSs, Orion offers a user interface that lets users tweak all the parameters of the BMS. Users can monitor temperature, set current limits and device parameters, see live data being gathered, and configure CAN communications. One downfall of the Orion BMS is that it is not modular. Orion offers different BMS sizes of up to 168 cells. But if a user wants to resize their battery pack, they have to buy a new BMS instead of buying an addon module to their existing BMS.

A novel aspect of our project is the module size. The BMS cell modules are small enough to clip on to the side of an 18650 cell. Smaller modules will lead to less space needed for battery storage in EVs.

To complete this project, we have drawn from our engineering curriculum. This project incorporates embedded systems, hardware design, user interface design, and communication. The PCB design and work with power supplies uses information learned in ECE 2630, ECE 2660, and ECE 3750. ECE 3430 provided techniques to write the software of the BMS boards. The user interface that interfaces with the BMS draws from CS 3240. Finally, some of our team members have experience working on the Solar Car team, which gives them knowledge about batteries and embedded systems for electric vehicles.

# Constraints

## **Design Constraints**

This project was a Capstone project for Computer Engineering, so there were some design constraints placed by the course. First, the project had to incorporate an embedded CPU capable of real-time response. Second, the project had to interact with a device that has not been seen in earlier classwork. Finally, the project had to have professional quality mounting, a PCB.

# CPU Limitations

The STM32G473CET6 microcontroller [7] was chosen for the BMS main board and the STM32F042F6P6 microcontroller [8] was chosen for the BMS cell boards. These microcontrollers were chosen because of their CAN capabilities, low power consumption, and price. The cell board microcontroller has 32 Kbytes of Flash memory, which severely limited the amount of software that was on the device.

# Manufacturing Limitations

When designing the PCB layout, there were constraints placed by the PCB manufacturer, Advanced Circuits [9], and the company who soldered components onto the board, WWW Electronics Inc [10]. The PCB limitations included a maximum size of 30 square inches, minimum 5 mil line/space and minimum 10 mil hole size. WWW Electronics required legible silkscreen with a minimum height of 1.5mm and oriented left-to-right or bottom-to-top. Additionally, components such as polarized capacitors and ICs needed a marking to indicate its orientation.

### **Economic and Cost Constraints**

This project was given a budget of \$500. Since this project has many components (1 main board, at least 2 cell boards, lithium-ion batteries), few backup boards were purchased. Only 1 main board and 3 cell boards were manufactured. To save additional costs, the main board was designed with multiple through hole components which can be soldered by a team member instead of paying WWW Electronics to solder them. Further cost savings were achieved by having the UVA Solar Car Team purchasing the 18650 batteries and the Vruzend Battery Kits.

# **External Standards**

#### CAN (Controller Area Network) 2.0B

In order to provide a standard interface for use in a vehicle system with potentially multiple control units, the CAN (Controller Area Network) protocol was used. In particular, CAN 2.0B was used with 11-bit message IDs. This protocol has a message payload of 8 bytes and a data rate of 1 Mb/s [11].

### IPC 2221

The minimum electrical spacing for all traces on the PCBs were determined by the IPC 2221 standard [12]. This is especially important for traces that were isolated from each other, as the spacing was the biggest factor in determining the effective isolation range. This is also very important for high-voltage traces, namely the traces stepping down the pack voltage. If these minimum spacings are not followed, there may be risk of arcing caused by high voltage differences between traces.

### SMD Component Packages

Surface Mount Device (SMD) packages have standardized sizes, allowing for ease of component manufacture and replacement. JEDEC is a leading standardization body [13]. The PCBs use many sizes of SMD components, including 0603, 0805, and 1210 passive components, Size A (EIA 3216-18) Tantalum capacitors, SOD-323 diodes, 8-TSSOP op-amps, SOT-23 regulators, 16-SOIC CAN transceivers, a 20-TSSOP microcontroller and a 48-LQFP microcontroller. The Main Node also uses many through-hole packages for most of its passive components, utilizing both radial and axial components.

### USB (Universal Serial Bus)

USB standards define how a computer can communicate with peripheral devices. The standards are developed and maintained by the USB Implementers Forum (USB-IF) [14]. A USB connection is used by the STLINK-MINI to allow for USB debugging and to allow the microcontroller to print to a serial monitor.

### SWD (Serial Wire Debugging)

The SWD specification, an ARM modification to the JTAG specification, is used for flashing and debugging embedded code [15].

### UART (Universal Asynchronous Receiver-Transmitter)

A UART, or a block of circuitry used for asynchronous communication, was used for communication from the Main Node to a computer for printing pack and cell data. The standard baud rate of 9600 bits/second was used [16].

## RoHS (Restriction of Hazardous Substances) Compliance

RoHS components do not use specific hazardous substances, as specified in Directive 2002/95/EC which originated from the European Union [17]. Most components used were RoHS compliant, minimizing the environmental impact of our design.

# WebSocket

In order to design a BMS configuration/data visualization program (PC Program) with the ability for remote connection, the WebSocket protocol was used to communicate between the two components. The WebSocket Protocol enables two-way communication between a client running untrusted code (in our case, the web interface) in a controlled environment to a remote host that has opted-in to communications from that code, such as our bridge program relaying messages between the CAN bus and the web interface [52].

# **Tools Employed**

# KiCad [18]:

KiCad is a software suite for electronic design automation. KiCad was used to help us create the circuit schematics and design the layouts for the PCBs for the Modular BMS. KiCad was also used to generate the Gerber files that were used to eventually print out the PCBs. William, Nripesh, and Dipesh had prior experience with using KiCad as a part of the Solar Car Team. Nikilesh and Phillip did not have prior experience with KiCad, and had to learn how to use KiCad while working on the Modular BMS.

# GitHub [19]:

GitHub is a code hosting platform for git version control. GitHub enabled our team to share software code for the Modular BMS across our team members. Every team member was already proficient with using GitHub.

# CADLAB [20]:

CADLAB is a visual version control platform for PCB design projects. Our team used CADLAB to collaborate and share PCB designs and circuit schematics for the Modular BMS. William, Nripesh, and Dipesh had prior experience with using CADLAB as a part of the Solar Car Team. Nikilesh and Phillip did not have prior experience with CADLAB, and had to learn how to use CADLAB while working on the Modular BMS.

Visual Studio Code Integrated Development Environment (VS Code IDE) [21]:

The VS Code IDE is a source code editor. Our team used the VS Code IDE to help write the code for our project. The VS Code IDE was also used as a wrapper to use PlatformIO features. Every team member was already proficient with using the VS Code IDE.

### PlatformIO [22]:

PlatformIO is an open source code editor that is an extension of VS Code. PlatformIO was used as the IDE to help develop software for the Modular BMS. PlatformIO was also used to help compile our software and the PlatformIO debugger was also used to debug problems with our software and with our PCBs. Our team did not have prior experience with using PlatformIO and had to familiarize ourselves with PlatformIO while completing the Modular BMS.

## Mbed OS [23]:

Mbed OS is an open-source embedded operating system. Mbed OS was used as the software framework to write code for the Modular BMS. Our team did not have prior experience with using Mbed OS and had to familiarize ourselves with Mbed OS while completing the Modular BMS.

# **Ethical, Social, and Economic Concerns**

# **Environmental Impact**

The environmental impact of the project will mainly concern the 18650 batteries used for testing the project. The lithium-ion batteries have a limited lifespan and consist of materials that require a large environmental impact to extract. Lithium itself has a high environmental cost, since the mining of lithium uses huge amounts of water and toxic chemicals to extract the material [24]. At the end of the battery lifespan, the batteries will be sent to a recycling facility to reduce the environmental impact [25].

# Sustainability

The project aims to improve the wider adoption of electric vehicles as a mode of transportation by creating a battery system that is easier to work with and develop for. This is enabled through modular system design, allowing for different battery pack configurations, as well as wider reusability for different electric vehicle applications. As a result, this will help reduce the amount of waste generated from the design of multiple unique battery systems for different applications, as the parts of the system can be reused. In addition, helping to drive adoption of electric vehicles will help reduce the overall carbon footprint from fossil fuels used in transportation.

# Health and Safety

The voltage produced by each individual 18650 cell will be approximately 0 - 5V. When put in series, the total voltage can be over 100V. As such, when working with high voltages, caution must be taken to avoid injury. Since the design is modular, the majority of testing will be

able to be performed with relatively low voltages in small configurations. However, when testing with larger configurations, precautions such as rubber gloves and other protective equipment can be used [26].

As the Modular BMS will be used to reduce costs and popularize electric vehicles, there are additional concerns that one must be aware of. After a car accident with an EV, for example, the lithium-ion battery that powers the EV is prone to exploding or catching on fire. The same safety precautions that are used in the lab such as insulated tools, are needed for first responders to handle EV accidents and prevent exposure to high voltages or currents. EV manufacturers need to design safety mechanisms such as additional shielding of the lithium-ion battery through an external aluminum plate and firewalls between battery modules [27]. These changes are needed to minimize the risks from using li-ion batteries and ensure the safety of their passengers when using the Modular BMS in an EV.

### Manufacturability

The system will be straightforward to manufacture, especially as pre-made weld-free battery holders will be used. The primary components to be manufactured are the PCBs and the housing for the main node. The housings can be 3D-printed, while the batteries to be purchased are standard 18650 cells and are easily purchasable.

### **Ethical Issues**

An ethical risk with the Modular BMS is that the rare earth metals in the electrical components that are used in assembling the Modular BMS such as the 18650 batteries are sourced from countries that lack strong labor laws and use child labor [28]. When sourcing the components for the Modular BMS, our team should aim to try to source parts from countries that uphold worker safety and do not use child labor if possible.

# **Intellectual Property Issues**

Previous BMS designs have been patented before such as a general BMS design that was patented by Ivan Loncarevic [29]. This BMS patent has the following as an independent claim: a central controlling microcontroller that is connected to a plurality of control circuits where each control circuit monitors and controls the charging of each battery cell. This BMS patent also has a dependent claim of having the BMS monitor the battery temperature and reduce the charging current if the temperature is above a specific threshold. In a patent filed by Hak Hon Chau for a fault tolerant modular battery management system, an independent claim for general BMS functionalities and a modular BMS design was filed [30]. In a similar patent filed by Joseph Mario Ambrosio and Konstantinos Sfakianos, an independent claim for a modular BMS design for use in EVs was filed [31]. Based on the claims made by these patents, the modular BMS that our team designed and built is not patentable due to the overlap with existing patents.

# **Detailed Technical Description of Project**

The goal of the project was to create a modular battery management system (BMS) for lithium-ion battery packs for electric vehicles. Our modular BMS would have a cell board for each battery cell that would monitor voltage and temperature. The cell boards would connect to a main BMS board which measures pack voltage and current, estimates pack health metrics and controls a fan to regulate temperature. Additionally, the main board would control relays to prevent the battery pack from overcharging and over discharging and send commands to the cell boards to perform passive cell balancing. Regulating temperature, current through the battery pack, and overall pack health ensures that the battery pack is used with maximum efficiency. The system is broken down into the following sections:

- 1. Hardware

- a. Main Board

- i. Schematics

- ii. PCB

- b. Cell Board

- i. Schematics

- ii. PCB

- c. Connected System

- 2. Software

- a. Pack Health Algorithm

- b. CAN specification

- c. PC Program

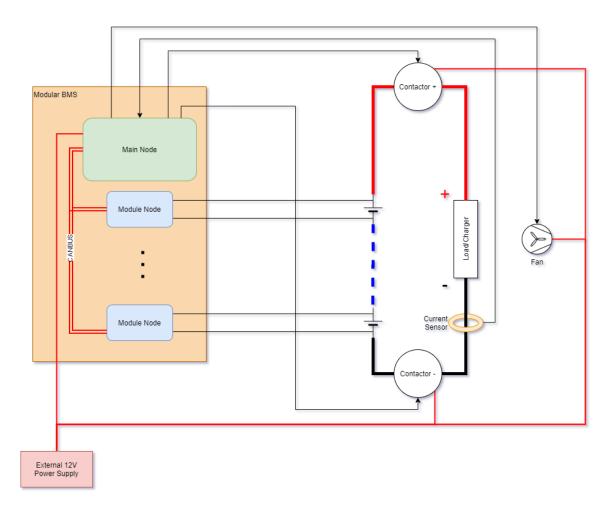

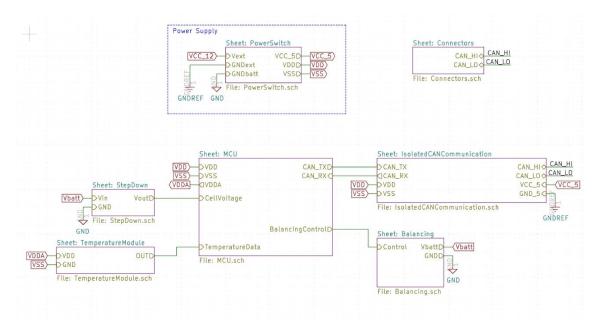

A block diagram of the system is shown in Figure 1. This shows that each module node (or cell node) is connected to a battery cell and communicates with the main node via a CAN bus. Additionally, the main node is connected to the pack current sensor, charging and discharging contactors, and a fan. All boards are powered using an external power supply.

Figure 1. Block Diagram of the Modular BMS

# Hardware

The hardware of this project consists of one main board and multiple cell boards. For our minimum viable product, we had two cell boards to show that the main board could control and communicate with multiple cell boards.

# Main Node

The main node is the main controlling unit of this system. The main node is in charge of powering the fan and triggering relays along with gathering battery pack data to report to a PC interface. The full scope of the main board is listed in the goals below:

- 1. Get cell temperatures and voltages from cell boards

- 2. Measure total pack voltage and pack current

- 3. Estimate pack health parameters: State of Charge (SOC) and State of Health(SOH)

- 4. Trigger relays to prevent battery from supplying high currents, overcharging, or over discharging

- 5. Power fan and set fan speed to regulate temperature

- 6. Send cell balancing commands to cell boards to equalize cell voltages via CAN

- 7. Send battery pack data to a PC program via CAN

The pack health parameters that the main board estimates are the State of Charge (SOC) and the State of Health (SOH) of each battery cell. The SOC of a battery cell is the ratio between the current releasable capacity and the rated capacity of the cell. The SOC is the percent charge you see for phone batteries. The SOH of the cell is the ratio between the maximum releasable capacity and the rated capacity of the cell [32].

In order to charge and discharge with maximum efficiency, cell balancing is needed. Cell balancing ensures that all cells are at the same state of charge, which lets all the cells get fully charged and fully discharged. If the cells are imbalanced, one cell will overcharge while another cell is still charging which hurts the battery cells [33].

# Schematic

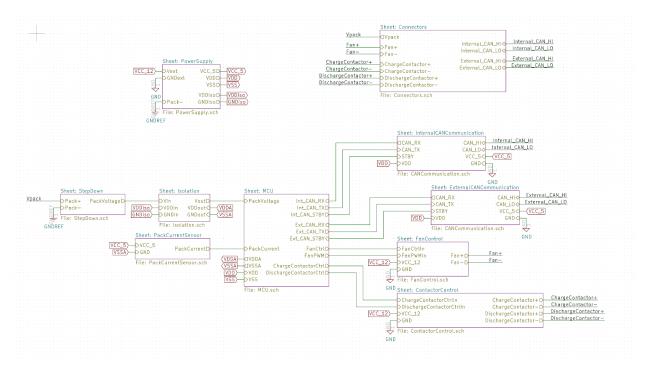

The schematic for the main node was designed in KiCAD shown in Figure 2. The schematic was broken down into many hierarchical blocks for ease of understanding.

Figure 2. Main Node Schematic

The main board is powered using a 12-volt supply which is then converted to a 5V supply and 3.3 V supply. The 5V and 3.3V supplies are used for the CAN transceiver and microcontroller respectively. The main node microcontroller interfaces with a pack current

sensor, a fan, and two contactors. One contactor is to control the charging of the pack and the other is to control the discharging of the pack. The microcontroller is also connected to two separate CAN buses. The internal CAN bus is for the main board to communicate with the cell boards of the BMS. The external CAN bus is for the main board to report pack data to a PC program. Finally, the microcontroller measures the pack voltage, but is isolated from the pack ground, as it is powered by the external supply and not the pack itself. Thus, an isolator is used between the microcontroller and the pack voltage input.

Figure 3. Main Node Power Supply Schematic

The power supply schematics of the main node is shown in Figure 3. Given a 12V of external voltage over Vext and GNDext, IC2 converts the external 12V to the internal 5V line, VCC\_5. The IC is set up with four capacitors and an inductor as shown in the datasheet [34]. IC3, a low-dropout regulator, regulates the 5V to the 3.3V line, VDD. The IC is set up with two bypass capacitors as shown in the datasheet [35]. Finally, an isolated 3.3V relative to the battery pack's ground is needed to measure the battery pack's voltage. An isolated 5V to 3.3V DC-DC converter, PS1, is used [36]. The DC-DC converter is set up with two bypass capacitors as specified in datasheets of similar components, as this datasheet did not specify bypass values. Test points (TP) are connected to the power supplies for debugging.

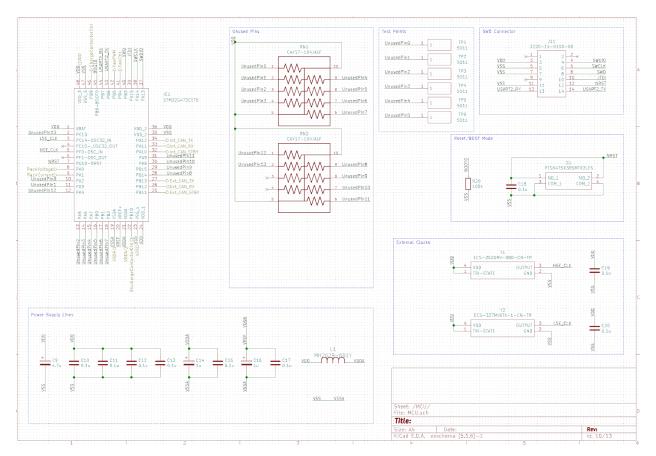

Figure 4. Main Node MCU Schematic

The MCU schematics of the main node are shown in Figure 4. The MCU was set up with bypass capacitors according to the datasheet [37]. A ferrite bead was used to connect the VDD (digital) and VDDA (analog) lines, as shown in the NUCLEO-G474RE development board schematics [38]. This effectively acts as a low-pass filter, so that high frequency noise is filtered out and thus any noise on the VDD line does not interfere with the VDDA line.

All unused pins were pulled up to VDD through resistor networks. Some unused pins were connected to test points in case they were needed for debugging.

The SWD connector was set up to connect to the STLINK-V3MINI, according to its user manual [39].

The reset button was set up similarly to the NUCLEO-G474RE development board, providing a connection to GND (VSS) on the NRST pin when pressed. Similarly, BOOT0 was pulled to GND.

External clocks (crystal oscillator chips) were added according to the respective datasheets [40], [41]. This was preferred over using crystals directly as shown in the NUCLEO-

G474RE development boards since there is less design work to be done this way (each needed a single bypass capacitor, according to the datasheets).

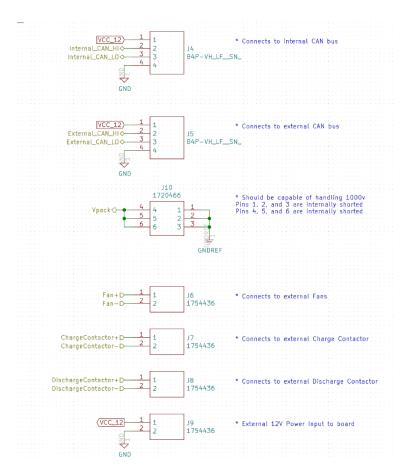

**Figure 5. Connectors Schematic**

As shown in Figure 1, the main node connects to two contactors and a fan. Figure 5 shows three connectors (J6, J7, J8) added onto the main board to connect the board to these peripherals. There are also two connectors (J4, J5) to connect to the CAN buses. Additionally, there are two connectors to connect to the external 12V supply (J9) and the battery pack (J10). The battery pack connector is much larger than the other connectors since it can accept up to 1000 V difference between the two input pins.

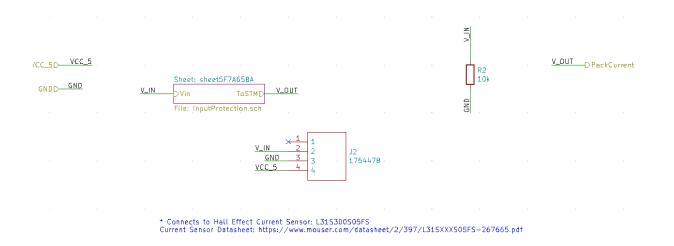

Figure 6. Current Sensor Schematic

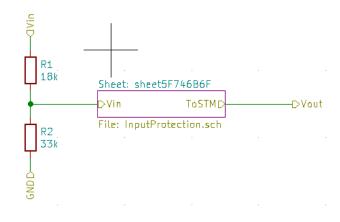

The main board also has a connector to the pack current sensor shown in Figure 6. The output of the current sensor has a pulldown resistor (R2) as specified by the datasheet [42] and goes through an input protection circuit shown in Figure 7.

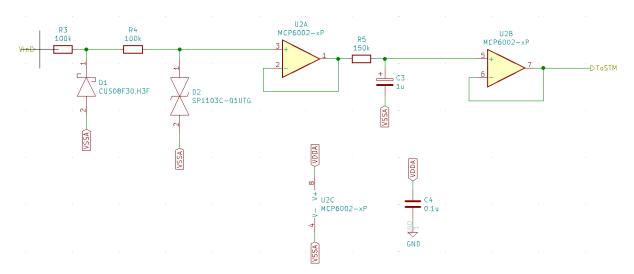

**Figure 7. Input Protection Schematic**

The input protection schematic shown in Figure 7 is meant to protect the inputs to the MCU from large voltage spikes that could arise due to signals traveling across long wires, and thus have a lot of inductance or capacitance associated with them. The design for this was based off of Digikey's Input Protection article [43] and modified slightly. Specifically, two unity gain buffers were added to ensure the signal going to the microcontroller's ADC inputs had no impedance associated with it. A single dual-package op amp was used for this, and a bypass capacitor was added according to the datasheet [44].

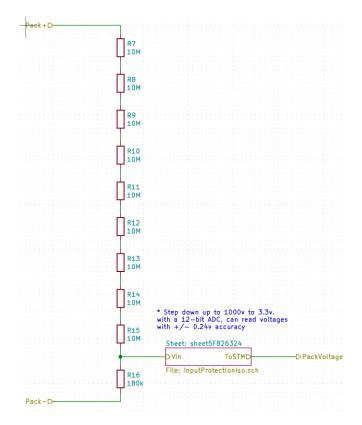

Figure 8. Main Board Step Down Voltage

To measure the voltage of the battery pack, the resistor voltage divider shown in Figure 8 was used. The voltage divider steps down the battery pack, with a maximum voltage of 1000V, to be within 3.3V which is the microcontroller's supply voltage. The output of the voltage divider is passed through the input protection circuit shown in Figure 8. The signal is then passed to the isolation circuit shown in Figure 9 below.

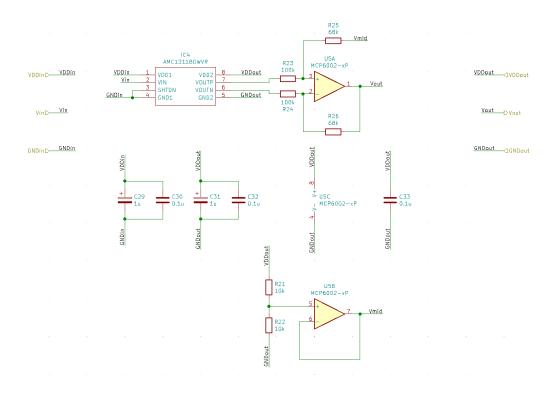

**Figure 9. Isolation Schematic**

The isolation circuitry shown in Figure 9 converts the stepped down voltage from being relative to the pack ground to the MCU's ground (the external supply ground). The isolator outputs a differential output, so a differential amplifier was used to convert that output to a single-ended output for the ADC to read. Because the pack voltage is expected to always remain positive, however, the Vmid voltage was reduced to 0V (GNDout) by removing R21 and shorting R22, and the differential amplifier gain was increased to increase the resolution of the pack voltage read by the ADC. Bypass capacitors for the op-amp and isolator were added according to their datasheets [45], [46].

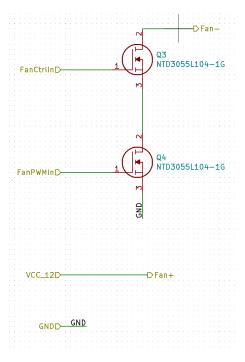

Figure 10. Fan Control Schematic

To control a 12V fan, the 12V external supply is connected to the positive end of the fan. The negative end of the fan is connected to the circuitry shown in Figure 10. The microcontroller has a control output that turns the fan on and off as well as a PWM output that controls the speed of the fan. These outputs are connected to MOSFETs in series that enable the main board to control the fan.

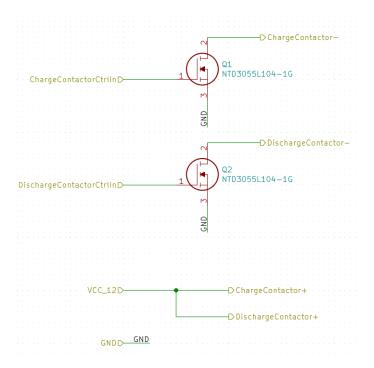

Figure 11. Contactor Control Schematic

Page 23 of 74

To control the contactors, the positive ends of the contactors are connected to 12V and the negative ends are connected to the circuitry shown in Figure 11. The microcontroller's control outputs are connected to the gate of the MOSFETs which allow the microcontroller to trigger the contactors.

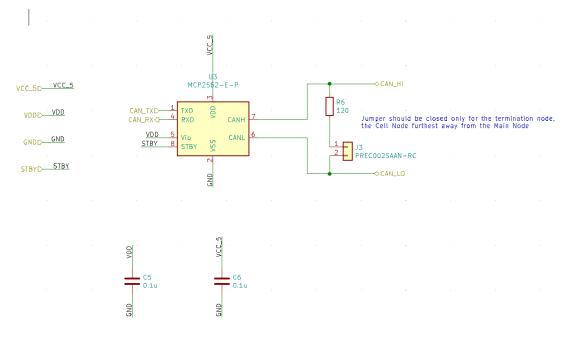

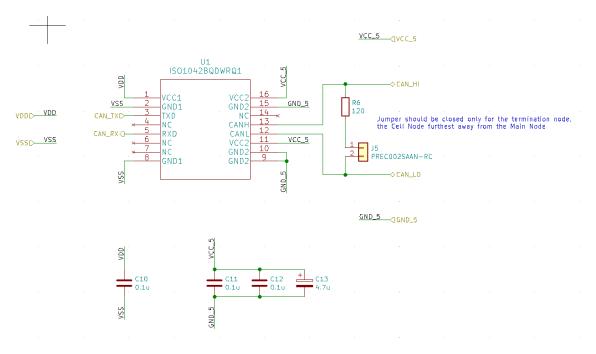

Figure 12. CAN Communication Schematic

The External and the Internal CAN communication blocks used the same sub-schematic for the CAN transceiver. The microcontroller connects to the transceivers via the TX, RX, and STBY pins, allowing the microcontroller to send and receive data as well as control the sleep mode of the transceivers via software. The 120  $\Omega$  termination resistor is connected to the CAN HI and CAN LO pins through a jumper. This jumper would only be shorted at the 2 endpoints of the CAN line. Thus, both the External and Internal CAN lines would have this jumper shorted for the main node, with a corresponding 120  $\Omega$  termination resistor at the other end of the External CAN line and only one cell node with a 120  $\Omega$  termination resistor shorted on the Internal CAN line. Bypass capacitors were added according to the datasheet [45].

### PCB

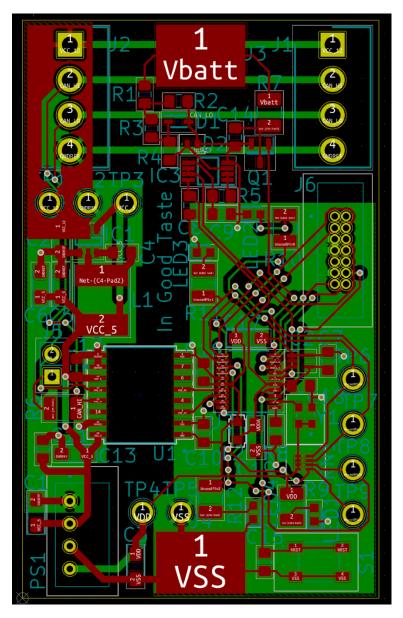

Figure 13. Main Node PCB

The PCB layout for the main node is shown in Figure 13, with the red traces showing copper top and the green traces showing copper bottom. Trace widths of 10 mils were used for signal wires and 30 mils for power lines and most 12 V lines. 30 mils was also used for the voltage divider stepping down the pack voltage.

The main node mostly used through hole components, as space was not an issue. This allowed us to reduce costs by allowing us to populate most of the components ourselves instead of 3W populating everything for us. This also allows for better power dissipation in the step-down circuitry for the pack voltage.

Two separate ground planes were used for the two isolated grounds, and a minimum distance of 60 mils were kept between them at all times to ensure 1000 V of isolation (according to the table provided in KiCad, based on IPC 2221). There was also no ground plane placed below the isolator chip, following the recommendations from the datasheet. The same minimum distance of 60 mils was kept between the pack's ground plane (the small one near the bottom of the board) and the pack's voltage input, as well as between each stage of the associated step-down voltage divider. For this reason, the pack's ground plane was not extended down to the bottom of the board, as that would violate the minimum distance requirement.

The power supply circuitry was placed at the top-left, and as close as possible to the input 12 V from the external supply. Three separate VCC planes were used for the power supplies: one for 12 V, one for 5 V, and one for 3.3 V. All of them were made as large as possible without interfering too much with other traces. This was to be able to dissipate more heat when more power is used on those lines, a good recommendation from the datasheets of the regulators.

When placing components for the layout, care was taken to place bypass capacitors as close as possible to the associated components. If layout recommendations were given in the component datasheets, those were followed as closely as was possible. Component groups were placed as close as possible to minimize the distances signal wires for active components had to travel. Low priority was given to components that were not actively used in the design, like test points and resistor networks for unused pins.

#### **Cell Node**

For every battery cell in the battery pack, a cell node is needed. The cell node reports cell voltage and temperature to the main node. The node also accepts cell balancing commands from the main node via CAN and performs passive cell balancing on the battery cell.

#### Schematic

The schematic for the cell node was also done in KiCad. The schematic is shown in Figure 14.

Figure 14. Cell Node Schematic

The cell node has temperature measurement circuitry, cell balancing circuitry, and similar step down, power, and CAN circuitry as the main node. The cell node is only connected to one CAN bus which is connected to the main node and all other cell nodes. The cell board is powered using a 12V external power supply which is converted to 5 volts for the CAN transceiver and 3.3 volts for the microcontroller. The passive cell balancing circuit is used to decrease the state of charge of the corresponding battery cell to equalize SOCs.

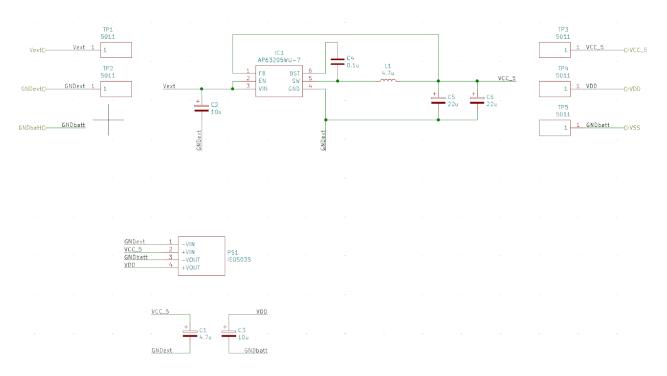

Figure 15. Cell Node Power Supply Schematic

The power supply schematics of the cell node are shown in Figure 15. Given 12V of external voltage over Vext and GNDext, IC1 converts the external 12V to the internal 5V line, VCC\_5. The IC is set up with four capacitors and an inductor as shown in the datasheet [34]. Finally, an isolated 3.3V relative to the battery cell's ground is needed to measure the battery cell's voltage. An isolated 5V to 3.3V DC converter, PS1, is used [36]. Two bypass capacitors are added according to the datasheet of other similar components, since this datasheet did not mention bypass capacitors. Test points (TP) are connected to the power supplies for debugging.

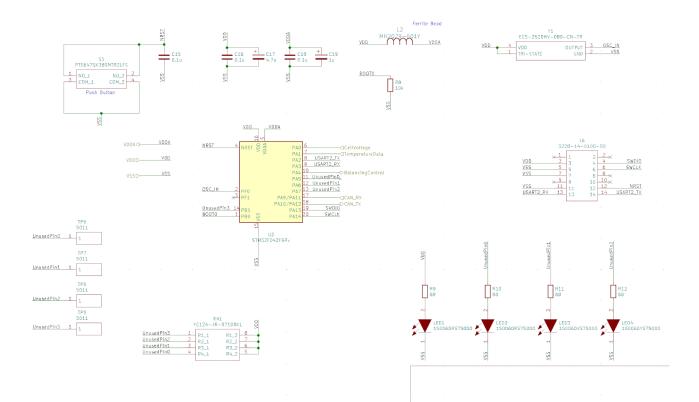

Figure 16. Cell Node MCU Schematic

The STM32F042F6P6 microcontroller was used for the cell board. Similar to the main node, the cell node's microcontroller is connected to a reset button (S1), an external clock, and a SWD connector to connect to our debugger. Additionally, the unused pins were connected to test points, pullup resistors, and LEDs for debugging. The microcontroller was set up with bypass capacitors according to the datasheet [47]. A ferrite bead was used to connect the VDD (digital) and VDDA (analog) lines, similar to the main node. This effectively acts as a low-pass filter, so that high frequency noise is filtered out and thus any noise on the VDD line does not interfere with the VDDA line.

Figure 17. Cell Node Connectors Schematics

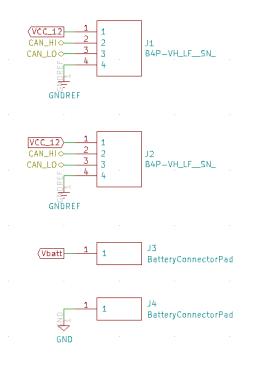

Each cell node is mounted onto its respective battery cell. Figure XX shows the connectors (J1, J2, J3, J4) that the cell board needs. J3 and J4 are to connect to the two ends of the battery (they are simply pads to solder nickel strips to), and J1 and J2 connect to the internal CAN bus, the same way the main node connects to the CAN bus.

Figure 18. Cell Node Voltage Divider

Similar to the main node, the cell node has a voltage divider to measure the voltage of its battery cell. The voltage divider shown in Figure XX is designed to step down a maximum voltage of 5V to be within 3.3V. The output of the divider is passed through the input protection circuit shown in Figure 7.

Figure 19. Temperature Module Schematic

The temperature module in Figure 19 measures the ambient temperature and scales its output voltage accordingly. The sensor can measure temperatures from -50 degrees Celsius to 150 degrees Celsius. A bypass capacitor is added to the circuit as recommended in the datasheet [48].

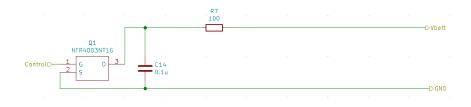

Figure 20. Cell Balancing Schematic

A passive cell balancing circuit, shown in Figure 20, is used to equalize different battery cells. When one battery cell has a higher voltage than the other batter cells, the cell board can send a control input to the MOSFET (Q1). This will cause the battery to supply more charge for current to run through the resistor (R7) which will decrease its voltage. Once the higher charged battery's voltage is decreased to be in line with the other cells, the control input can be set to low. Passive cell balancing is easy to implement, as the circuit in Figure 20 is simple. However, it is less efficient than other cell balancing methods [33].

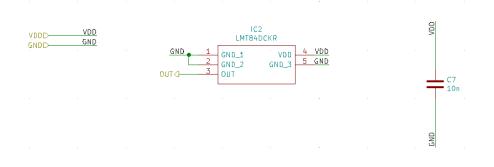

Figure 21. Isolated CAN Schematic

The CAN transceiver used in the cell node is different from the one used in the main node. This is because the cell node must use an isolated CAN transceiver, as the CAN HI and CAN LO lines are relative to the external supply's ground while the microcontroller is powered relative to the battery cell's ground. Thus, the isolated CAN transceiver is powered differently on two sides: on the microcontroller side, it is powered from the VDD line, the same 3.3 V line powering the MCU (relative to the battery cell's ground). On the other side, the transceiver is powered from VCC\_5, the 5 V line relative to the external supply's ground. This was stepped down from the 12 V line passed along to this cell node with the CAN HI and CAN LO lines (also relative to external supply's ground).

The isolated CAN transceiver did not have a STBY pin, unlike the main node's CAN transceivers, so the microcontroller cannot control the sleep mode of the transceiver. Bypass capacitors were added according to the datasheet [49].

PCB

Figure 22. Cell Board PCB

Figure 22 shows the PCB layout for the cell board. This board mostly contained SMD components to keep the board size small. One goal of this project was to have the cell board be small enough to clip onto the side of the battery cell. The dimensions of the cell board were 65mm by 40mm so that the cell board is the same height and width as two batteries. [50]. This allows us to clip the cell nodes onto the sides of the battery pack by alternating the side each adjacent cell's board is attached to. Cells are attached to the battery pack via the Vbatt and VSS pads that read the cell voltage. Nickel strips were soldered to the Vbatt and VSS pads and securely screwed down under the copper bus bars used in the Vruzed battery caps.

Similar to the main node, trace widths of 10 mils were used for signal wires and 30 mils for power lines and most 12 V lines.

Two separate ground planes were used for the two isolated grounds, and a minimum distance of 60 mils were kept between them at all times to ensure 1000 V of isolation (according to the table provided in KiCad, based on IPC 2221). There was also no ground plane placed below the isolator chip, following the recommendations from the datasheet.

The power supply circuitry was placed at the top-left, and as close as possible to the input 12 V from the external supply. Due to the limited space, only one VCC plane was used for the 12 V line; the 5 V and 3.3 V lines simply used 30 mil traces.

When placing components for the layout, care was taken to place bypass capacitors as close as possible to the associated components. If layout recommendations were given in the component datasheets, those were followed as closely as was possible. Component groups were placed as close as possible to minimize the distances signal wires for active components had to travel. Low priority was given to components that were not actively used in the design, like test points and resistor networks for unused pins.

## Software

For this project, software was written using the Mbed OS framework and uploaded to the boards using the PlatformIO IDE. Figures 23 and 24 below show the high-level software flow charts for the software on both the cell node and main node.

Figure 23. Cell Node Software Flow Chart

Figure 24. Main Node Software Flow Chart

The cell node software was originally planned to also perform cell health parameters, but as the microcontroller was much more severely constrained in memory usage than originally anticipated, that was moved to the main node, which has a much larger memory capacity. Thus, the cell node software only needs to measure the cell voltage and temperature and control cell balancing based on instructions received from the main node over CAN. The cell node also relays the measured cell voltage and temperature to the main node over CAN.

The main node will read pack voltage and pack current. When a CAN message comes from a cell board, the main node will read the cell node's temperature and cell voltage. Using this data, the main node will estimate pack health, control the contactors, fan, and send cell balancing commands. If the pack current is above a threshold current or the pack health algorithm (detailed in the next section) shows that a battery is fully charged or fully discharged, the main board will trigger a contactor. If the current is positive, it will trigger the discharging contactor and if the current is negative, it will trigger the charging contactor.

The fan logic is shown in Figure 25. If any cell temperature is above the temperature threshold (25  $^{\circ}$ C), the main board will turn on the fan. The speed of the fan is controlled by a PWM signal from the main board. The higher the temperature, the faster the fan will run.

Figure 25. Fan Software Logic

The cell balancing logic is shown in Figure 26. The main node collects voltage information from each cell node. Given the minimum cell node voltage, the main node sends a cell balancing command to cell nodes who have a voltage that is greater than the minimum voltage by a threshold (.01V). Once the voltages are equal, the cell balancing command will be deactivated.

Figure 26. Cell Balancing Logic

# Pack Health Algorithm

The battery pack health metrics that we wanted the BMS to estimate was state of charge (SOC) and state of health (SOH) of the battery pack. To do this, the BMS finds the SOC and SOH of each battery cell and reports the average metrics. The state of charge is the ratio of a

battery cell's releasable capacity to its maximum capacity expressed as a percentage using the following equation:

$$SOC = \frac{C_{releasable}}{C_{rated}} * 100\%$$

The SOC increases as a battery is charged and decreases as a battery is discharged. The state of health of a battery shows how new a battery is. The SOH is the ratio of the battery's maximum releasable capacity to the maximum capacity of the battery prior to any degradation, which is expressed as a percentage using the following equation:

$$SOH = \frac{C_{max}}{C_{rated}} * 100\%$$

For a new battery, the SOH starts at 100%. As the battery goes through charging and discharging, the battery degrades and the amount of charge that the battery can hold decreases. As the battery is used, SOH decreases.

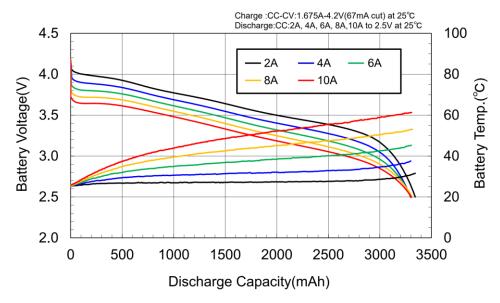

#### Voltage based SOC estimation

The Voltage method to determine the SOC of a battery involves using the reading of the battery voltage to obtain the equivalent SOC value using the known discharge curve (voltage vs. SOC) of the battery. The voltage vs SOC graph is shown in Figure XX. Our average discharging current was 3.5A, so we used the 4A curve on the graph. This method has some inaccuracies due to how the battery voltage is affected by temperature and discharge rate.

Figure 27. Voltage vs. SOC Graph for 18650 Batteries [51]

#### **Coulomb Counting SOC estimation**

The Coulomb Counting Method uses the current sensor to determine the remaining capacity. Assuming a battery starts with a SOC of 100%, we can integrate current over time to see how many Coulombs have entered and exited the battery, which results in the following equation:

$$SOC(t) = SOC(t_0) + \frac{1}{C_{rated}} \int_{t_0}^{t} I dt$$

When the battery is charging, the current will be positive and when the battery is giving power to a load, the current will be negative. There are downsides to this approach, however, as the accuracy of this method is dependent on the accuracy of the initial SOC estimation. This initial SOC estimation must also be re-calibrated regularly as the battery capacity decreases. Furthermore, the battery will always deliver less charge during discharge than was put into it during charging, making it difficult to get an accurate SOC estimate. This means that there would be accumulated errors in the SOC measurement. Measurement errors from the current sensor will also contribute to the accumulated errors in the SOC estimate.

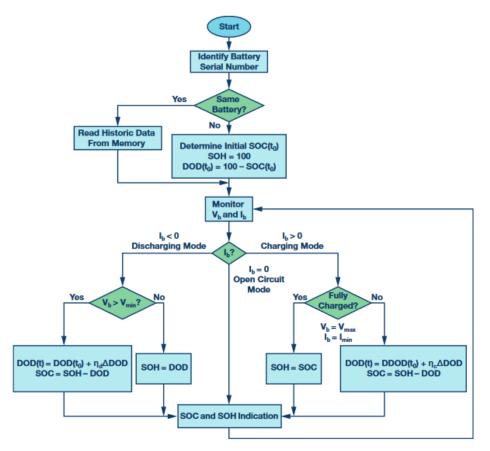

#### **Enhanced Coulomb Counting**

To address the drawbacks of the Coulomb Counting Method for SOC Estimation, several additional factors are introduced to obtain a more accurate estimate of the SOC for the battery.

When the battery is discharging, the depth of discharge (DOD) can be expressed as the percentage of the capacity that has been discharged relative to  $C_{rated}$ , where  $C_{released}$  is the amount discharged by the battery.

$$DOD = \frac{C_{released}}{C_{rated}} * 100\%$$

The difference in DOD over a period  $\tau$  can be found using the following equation while measuring the charging and discharging current.

$$\Delta DOD = -\frac{1}{C_{rated}} \int_{t_0}^{t_0 + \tau} I(t) \, dt \, * \, 100\%$$

This results in the following equation for DOD(t):

$$DOD(t) = DOD(t_0) + \Delta DOD$$

Using these values, the SOC for a battery can be estimated using the following equation:

$$SOC(t) = SOH(t) - DOD(t)$$

Initially, for a new unused battery, the SOH is assumed to be healthy and is equal to 100%. The SOH can then be recalibrated by accumulating the sum of the total charge put into the

battery after it is fully charged or by using the accumulated DOD value when the battery is exhausted. The battery is fully charged when the battery voltage reaches the upper limit voltage  $(V_{max})$  and the current declines to the lower limit (I<sub>min</sub>). The battery is fully discharged when the battery voltage is less than the lower limit (V<sub>min</sub>).

The Enhanced Coulomb Counting Method for SOC Estimation can be summarized in the following flow diagram:

Figure 28. Enhanced Coulomb Counting Flow Diagram

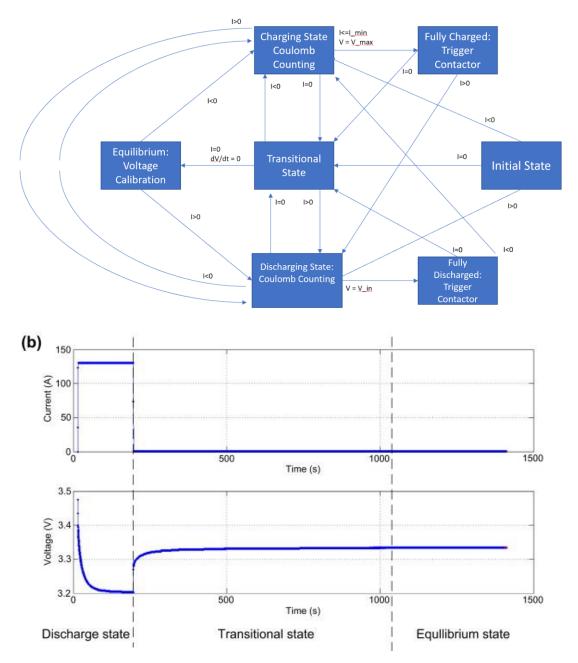

### **Combined Coulomb Counting and Voltage-based for SOC Estimation**

The cumulative error of the counting integrator from the Coulomb Counting method can be removed using a counter calibration based on the OCV characteristics while the battery is not in use. The current is otherwise integrated to get the relative charge in and out of the battery. A state diagram illustrating this approach is shown below:

Figure 29. State Diagram of Combined Coulomb Counting and Voltage-based for SOC Estimation

A change in the state diagram is detected by monitoring the voltage and current with the coulomb counting being used in almost all states besides "Equilibrium state" and "Fully Charged". In equilibrium state, the battery voltage is stable and the OCV voltage characteristic is used to calibrate the SOC. Another calibration is done when the cell is fully charged because this state is easily detectable during the constant-voltage charging mode. When the current reaches a minimal value known as end of charging current (EoCC), the charging process is complete and the battery is fully charged.

This method has a reported estimation error of less than 3% during full cell cycling. This SOC estimation error can, however, increase to more significant levels if a battery is used continuously and resting times between charge and discharge cycles are not long enough to reach voltage equilibrium and perform calibration.

### SOC Algorithm Decision

Enhanced Coulomb Counting seems to be the best option for SOC estimation because it does not need advanced battery information like the Kalman filter approach, and it is usually more accurate than voltage based SOC estimation. However, Coulomb Counting assumes that all batteries in series have the same SOC because they have the same current. This is false because each battery will be slightly different, and a BMS needs to understand these differences in SOC in order to perform cell balancing. Therefore, we decided that the SOC algorithm to use is the Combined Coulomb Counting and Voltage-based method for SOC estimation to get an estimate that uses current and voltage. This method was chosen because it would reduce the accumulated errors from using the Coulomb counting method as this method is relatively accurate in the short term, and the periodic recalibrations using the OCV would ensure that the error from the Coulomb counting method was implemented in software. This algorithm uses lots of readings from the current sensor, whose uncertainty is discussed in Appendix A.

### **CAN Specification**

CAN communication was used for the boards to communicate between each other (internal CAN bus) and for the main board to communicate with an external PC program (external CAN bus). Each CAN message had an 11-bit identifier and 8 bytes of data. The 11-bit identifier also represented the priority of the CAN message. In the internal CAN bus the 11-bit identifier is split into the upper 4 bits to show the message type and the lower 7 bits to show the board identifier. The board identifier is used to distinguish between cell boards sending the same type of message. The 7-bit board identifier allows for 128 nodes on the internal CAN bus (1 main node and up to 127 cell nodes). Floating point numbers are sent in the CAN bus by multiplying them by a constant and casting them as integers. The internal CAN specification is shown below:

- Internal Message 0, Main Board to Cell Board

- Bits 0 to 63: Balancing command for cell boards 0 63 (ordered sequentially)

- Internal Message 1, Main Board to Cell Board

- Bits 0 to 63: Balancing command for cell boards 64 127 (ordered sequentially)

- Internal Message 2, Cell Board to Main Board

- Bits 63 to 48: Cell Voltage (V, Divide integer by 10000 to get cell voltage float)

- Bit 47: Cell Temperature Sign Bit

- Bits 46 to 40: Cell Temperature (°C)

In the external CAN bus the 11-bit identifier is split into the upper 10 bits to show message type and the lowest 1 bit for the board identifier (main board or PC program). The external CAN specification is shown below:

- External Message 0, Main Board to PC Program

- Bits 63 to 56: Pack Average State of Charge (%, Divide integer by 2 to get float)

- Bits 55 to 48: Pack Average State of Health (%, Divide integer by 2 to get float)

- Bits 47 to 32: Pack Voltage (V, Divide integer by 100 to get float)

- Bit 31: Pack Current Sign Bit

- Bits 30 to 16: Pack Current (A, Divide integer by 100 to get float)

- Bit 15: Pack Highest Temperature Sign Bit

- Bits 14 to 8: Pack Highest Temperature (°C)

- Bit 7: Pack Average Temperature Sign Bit

- Bits 6 to 0: Pack Average Temperature (°C)

- External Message 1, Main Board to PC Program

- Bits 63 to 0: Cell Voltage for Device 0, 1, 2, and 3 (V, Divide integer by 10000 to get cell voltage float)

- External Message 2, Main Board to PC Program

- Bits 63 to 0: Cell Voltage for Device 4, 5, 6, and 7 (V, Divide integer by 10000 to get cell voltage float)

- ...

- External Message 32, Main Board to PC Program

- Bits 63 to 0: Cell Voltage for Device 124, 125, 126, and 127 (V, Divide integer by 10000 to get cell voltage float)

### **PC Program**

In order to view the status of the BMS, an external interface was needed. The design of the main node accommodated a second CAN bus interface to provide a way for the BMS to communicate with either a computer connected to the same CAN bus, or with another vehicle module when the BMS is deployed in a vehicle. For demonstration purposes and simplicity, the CAN specification was designed for the former case. To enable the status of the BMS to be viewed as easily as possible, there needed to be two main components, one that allowed for a GUI for receiving BMS data as well as sending commands to the BMS, and another that relayed messages to and from the GUI as CAN frames on a CAN bus interface, acting as a bridge. The interconnection between the two was decided to be WebSockets, as the protocol is programming-language agnostic and is supported by all major web browsers. WebSocket clients can be in any language, and the bridge acting as a WebSocket server also opens up the ability for remote connection to the bridge program.

### **CAN Bridge Program**

The bridge program was chosen to be written in the Rust programming language, as it is a type safe and memory-safe language that has performance on par with, and in some cases, faster than C. Along with the tokio library, Rust additionally provides powerful asynchronous and multithreaded programming constructs that allow for more performant programs and more efficient use of hardware resources.

The main structure of the program consists of two asynchronous background tasks and a single foreground task. The primary foreground task opens a socket to the CAN Bus interface and listens for CAN Frames. The first background task receives messages from this main foreground task using an inter-thread communication channel, specifically a multi-producer, single-consumer channel (MPSC). When the main foreground task receives a CAN Frame, it partially decodes a frame, encodes it into a JSON string, and then transmits it over the MPSC channel. When the first background task receives the encoded message, it relays it out over the open WebSocket. The second background task listens for incoming WebSocket messages and parses the message data as a command. While the original intention was for bi-directional bridge support, there was not enough time to implement both, so the CAN-to-WebSocket functionality was prioritized and finished.

### **GUI Program**