# CIRCUIT DESIGN AND CONFIGURATION FOR LOW POWER FPGAS

A Dissertation by Seyi Ayorinde 6 July 2016

Submitted to the graduate faculty of the Charles L. Brown Department of Electrical and Computer Engineering in partial fulfillment of the requirements for the Dissertation and subsequent Ph.D. in Electrical Engineering

> Approved By: John Lach, Committee Chair Scott Acton Steve Bowers Kevin Skadron Ben Calhoun

# Outline

| Α | bstract                                                                                                                                                                                                                                                                         | ii                                                   |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1 | Introduction         1.1       Motivation for Low-Power FPGAs - Ubiquitous Computing                                                                                                                                                                                            | 4<br>4<br>6<br>7<br>7                                |

| 2 | Background         2.1       General FPGA Architecture         2.2       Commercial Ultra-Low Power FPGAs         2.3       Academic Ultra-Low Power FPGAs                                                                                                                      | 9<br>9<br>10<br>12                                   |

| 3 | FPGA Generation and Configuration (FGC)3.1Motivation3.2FGC Overview3.3Prior Art3.4Running the FGC flow3.5Architectural Assumptions in FGC3.6FPGA Tile3.7FGC Directory Structure3.8File Descriptions3.9Proof-of-Concept Simulations3.10Limitations and Future Work3.11Conclusion | 18 $16$ $17$ $19$ $23$ $25$ $29$ $44$ $45$ $50$      |

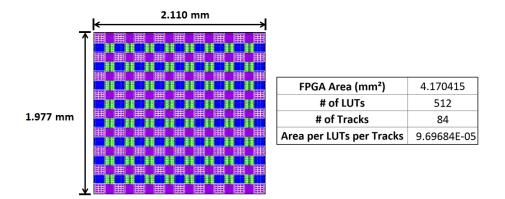

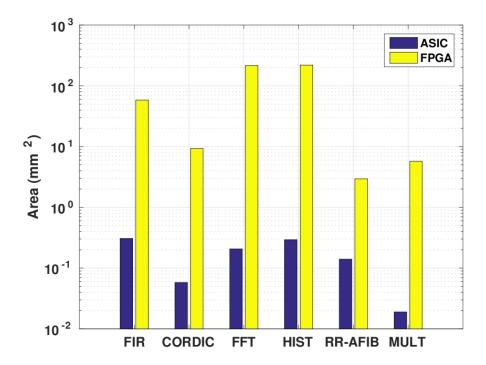

| 4 | Architecture Exploration4.1Motivation4.2Prior Art4.3Architectural Parameters for FPGAs4.4Commercial and Academic Low-Power Architectures4.5VTR Investigation4.6Conclusions4.7Future Work                                                                                        | <b>52</b><br>52<br>52<br>53<br>54<br>54<br>63<br>64  |

| 5 | Circuit Exploration5.1Motivation5.2Configurable Logic Block (CLB) Exploration5.3Configuration Bit Exploration5.4Sense Amplifier Exploration5.5Conclusions and Future Work                                                                                                       | 66<br>66<br>72<br>86<br>90                           |

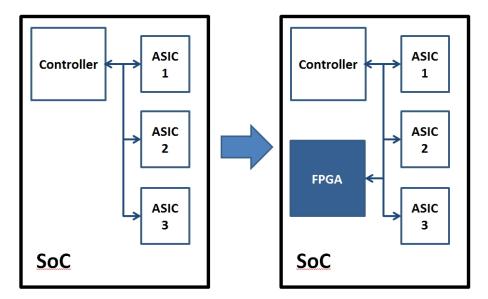

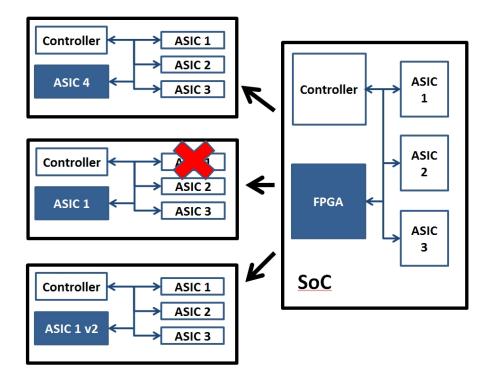

| 6 | Embedded FPGAs in SoCs6.1Motivation6.2Prior Art6.3ASIC Blocks on ULP SoCs6.4Mapping SoC functions to FPGA fabrics6.5Using purely CLB fabrics6.6Built-In Self Test Mechanisms for SoCs using FPGAs6.7Conclusions6.8Future Research Directions                                    | 92<br>92<br>93<br>94<br>94<br>98<br>99<br>106<br>107 |

| - | Conclusion         7.1       High Level Impact           | <b>110</b><br>111 |

|---|----------------------------------------------------------|-------------------|

|   | Publications         A.1 Pending Publication             | <b>114</b><br>114 |

| в | Glossary of Terms         B.1 Acronyms         B.2 Terms |                   |

# Abstract

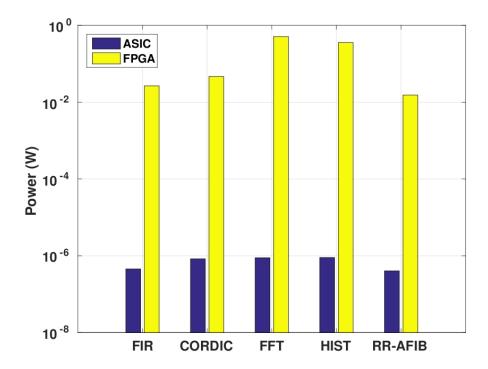

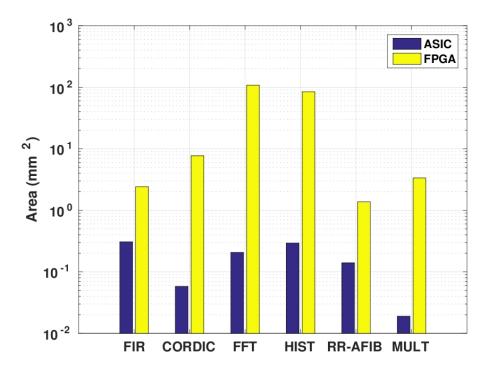

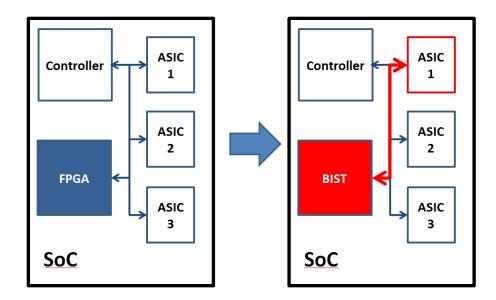

Today, society is moving towards a ubiquitous computing (UbiComp) environment, where sensors and other integrated circuits (ICs) are ever present in daily life, creating a smart environment for people to constantly monitor and react to their environments. For UbiComp to be fully realized, a host of requirements are necessary for the ICs deployed in this vast network. These requirements include low cost, low power consumption, flexibility, and adequate computation power. Current IC design methodologies do not quite meet all UbiComp requirements. Application Specific Integrated Circuits (ASICs) are low power and have the necessary computing power for UbiComp applications, but they are prohibitively inflexible. Ultra-Low Power (ULP) General Purpose Processors (GPPs) have the necessary flexibility, but are prohibitively high power (by multiple orders of magnitude). Field Programmable Gate Arrays (FPGAs) are another IC implementation that could potentially be used for UbiComp applications, because they bridge the gap between the high efficiency of the ASIC and the high flexibility of the GPP. However, FPGAs have historically been targeted for high performance applications, where performance (or speed) is the main metric. As a result, commercial FPGAs are too power hungry for ULP applications (like UbiComp). Relatively little research has been done to bring reconfigurable logic into the ULP application space. However, if FPGAs can be retargeted for ULP applications, then they will intrinsically bridge that same gap, this time between ULP ASICs and ULP GPPs, by providing energy efficiency than ULP GPPs, but also have the flexibility to update or re-target their applications (a necessary requirement for UbiComp) without the expensive, time-consuming respins that ULP ASICs require.

This dissertation explores the steps necessary to both build and configure Ultra-Low Power FPGAs. These steps include:

- 1. developing a toolflow that will not only allow researchers to quickly co-optimize FPGA fabrics for different circuit and architectural parameters, but also users in the future to quickly be able to generate FPGA fabrics with the necessary configurations for a given benchmark circuit

- 2. re-assessing FPGA architectural parameters to determine architectures most suitable for ULP operation for FPGAs as opposed to high-performance operation

- 3. revisiting circuit design of FPGA-building blocks and re-designing them for low power operation

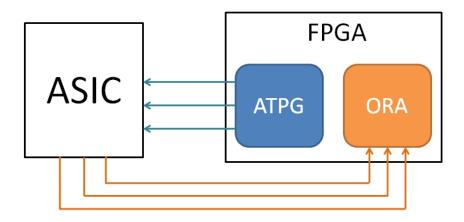

- 4. exploring the integration of the ULP FPGA fabric into a SoC designed for wireless sensing applications

# Acknowledgements

I would be remiss if I didn't first thank God, through my Lord and Savior Jesus Christ, for providing me with the countless opportunities that led to this accomplishment, a PhD in Electrical Engineering (WHAT!?). I've been quoting the words of Paul and Timothy from the bible since I could talk: "I can do all things through Christ who strengthens me (Phil. 4:13)." I'm happy to attest to that, and proclaim that PhD degrees definitely qualify!

I'm so incredibly blessed to have a strong support system in my life, which was integral in my completion of this degree. I can't thank all of the people in my life enough. I first want to thank my father. He has been an inspiration my whole life, especially academically. He has more degrees than you can shake a stick at (BS, MS, CE, MBA, PhD). But more importantly, he has high expectations for me and my only brother. In fact, right before I set of for college, he told me: "I don't care what you do, son. Just make sure you get a doctorate." No pressure, huh? But I'm happy to say that I think I made my father proud, and that's all a son can ask for. I love you, Dad, and thanks.

My mother is also incredibly supportive, but in a very different way. She's a constant source of support, never wavering in her love, and is incredibly selfless with her time and her energy. She's still working in my father's retirement, and she frequently volunteers to travel here from DC to visit, despite the fact that she had to wake up at 3 AM for work that same day. I love you, mommy, thank you so much for being there the way you have my ENTIRE life, but particularly as I completed this degree.

I would also like to thank my little brother, Tope, who has been my best friend for years, and has helped to push me in ways he probably doesn't even realize. I've come to learn that he loves me very much, and looks up to me as something to aspire to. I don't mean to say that in a boastful way. In fact, I think that would be true whether or not I managed to achieve some level of success or not; it's just the way our relationship works. But because he looks up to me, it provided an additional impetus for pursuing my doctorate degree. Since I also have him looking up to me, I knew I needed to be the best student, brother, son, and man that I could be, to make sure that he followed suit. He's currently working on his master's degree at Virginia Commonwealth University, and I couldn't be more proud of him. I love you, Top'.

About two years into my degree program, I met a girl by the name Elizabeth Baker. Long story short, she's now my girlfriend of almost 2 years, and I couldn't be happier about it! Straight up, my friends get so annoyed by us. But thanks for giving me some sanity while things were at their toughest. A perfect example came when I was testing the first FPGA test chip that I personally worked on. Nothing seemed to be working, and I complained to Lissie, saying "No matter what I do, these chips won't work!" She responded, without batting an eye, "Did you try putting Old Bay on it?" (Get it? Like potato chips?) In the moment, I was NOT amused, but Lissie has brought a joyous sense of levity to my life, and I love her very much for it. Baby I did it! Thanks for everything! I LOVE YOU!

My academic advisor, Prof. Ben Calhoun, is kind of a rock star at UVa. He brings in a ton of grant money, started his own company that is doing well, has an amazing family. 5 years ago I stepped into his office to make my pitch for working for him. In retrospect, I was probably a little too honest...I told him that I have absolutely no prior experience in electrical engineering or chip design. I told him that his works looks very interesting, and that I'm smart enough to pick it all up, and I promised I would do good work. For some reason, Ben thought that sounded like a good idea, which honestly still BLOWS MY MIND. But 5 years later, I think I made good on my promise. Ben, I appreciate you taking a chance on me, and I hope I did you proud. Thanks for your guidance, your high expectations, and your support in my pursuance of this degree. I couldn't have done it without you!

I definitely want to thank all of the people that have worked on the FPGA project in Ben's research group over the years. Dr. Joe Ryan, thanks for getting the project rolling and in a good direction. I especially want to thank He Qi, who has been a joy to work with. Not only did he treat me with the utmost respect (almost like I'm his boss, which I obviously am not), but he's also low-key HILARIOUS, and always has kind words to say. Keep up the hard work, He, and I'm excited to see where the FPGA project goes!

I'd like to also thank other members of the research group, both past and present. I'd especially like to thank Chris Lukas and Farah Yahya, who have given immense support over the last couple years in particular. From figuring out what a particular Cadence tool is trying to do to helping debug Verilog code, you guys have been patient and helpful, and I appreciate it! I'd like to thank past BenGroup members, particularly Dr. James Boley, Dr. Kyle Craig, Dr. Yousef Shakhsheer, and Dr. Alicia Klinefelter. Jim, way to be an athlete, thanks for being a good roommate and a good research colleague. Kyle, thanks for teaching me how to do top-level integration for a chip, and how to bowl over 100. Yousef, thanks for the Hulk Smash! button and the automated nerf rocket launcher. Oh, and the technical stuff too...Alicia, thanks for humanizing this research group from when I first got here. You're probably the biggest reason why I got comfortable in this research group, and I'll forever be indebted to you for that. Also thanks to all of the other BenGroup members (Divya, Harsh, Abhishek, Jacob, Ningxi, and Arijit) for the various ways that you've helped me along this journey. Best of luck!

Lastly, I want to thank the staff here at UVa. Often times, their work is overlooked because it isn't quite as technical in nature, but the fact of the matter is we as researchers can't do our technical work without having the space in which to conduct the research, and the materials to do the research, from physical research equipment to IT infrastructure and CAD tools. So with that I want to thank my work mother, Terry Tigner, for all that she's done for me and for this research group. Thanks, and I love you! I also want to thank Gary Li for keeping our servers up and running, and for putting up with our constant requests and dealing with them gracefully. I also want to thank Dan Fetko, Yadi Weaver, and David Durocher. Thanks for making this research work possible!

Actually, one more shout out. A big part of why I've pushed myself to this point is becaue the people closest to me are also doing big things. Two of my best friends from high school are finishing up their PhDs this summer: Gregg Tabot at University of Chicago in Computational Neuroscience, and Chris Gilmore at MIT in Aerospace Engineering. My best friend from college, Clint Smith, is currently pursuing his PhD in Education at Harvard. I'm in good company, and I couldn't be more greatful about. In the words of the wise Wiz Khalifa, "Hol' up hol' up, we dem boyz!!" Or as GOOD Music put it, "Ain't no body [messing] wit' my clique."

Thanks again to everybody in my life. I'm humbled, and excited for the future.

3

# 1 Introduction

# 1.1 Motivation for Low-Power FPGAs - Ubiquitous Computing

Today, in a world where people have immediate access to massive amounts of information, increased control and awareness of the surrounding environment is becoming more and more viable, and perhaps necessary. For this to occur, integrated circuits (ICs) need to be redesigned such that a large number of sensors can be deployed simultaeneously in different environments (wearable sensors, smart home sensors, infrastructure monitoring, etc.) and users can access the information provided by these sensors and respond accordingly. This landscape, known popularly as ubiquitous computing (UbiComp), is not far off. There are, however, certain restrictions in this application space that prevent UbiComp adoption on a large, commercial scale. These challenges are as follows:

- Ultra-Low Power and Energy Operation For UbiComp to occur, there will need to be a large number of ICs deployed in various environments (homes, wearable sensors, etc.). Constantly changing batteries for all of these devices, or connecting all of them to wires, becomes invasive and infeasible. Therefore, these sensors need to be very-low power, so as to maintain functionality with a small power budget, and also be low energy, so as to not drain power sources too quickly. This will minimize battery changes, allowing the sensors to spend extended periods of time functioning.

- Computational Flexibility With many sensors deployed in the field, constantly gathering information, removing them from their deployments can be problematic. Moreover, algorithms used for sensing applications are subject to change, either from discoveries of new methods, or from updated versions of the current approach. Additionally, these sensors are subject to different environments, and thus may need to perform slightly (or completely) different functions based on the environments. For all of these reasons, these sensors need to be designed with a level of flexibility, in order to meet all of the requirements of the environments they are sensing.

- Computational Power It's not enough for these sensors just to sense information. If the devices simply sent all information collected to a user, it would be highly inefficient, as the sensor would send more information than is necessary, and the information would likely not be discernible by the user. Ideally, all of the sensors in this UbiComp platform will be able to process some of the information it collects on the node itself, in order to give the information to whoever needs it in a way that is easy to understand and work with.

• Low Cost – As mentioned before, UbiComp would require thousands, millions, and potentially billions of sensing nodes to be deployed all at the same time. The cost of developing and fabricating these chips would be very high, and that cost goes up even further if these chips need to be re-designed and re-fabricated with each new or updated algorithm.

Unfortunately, current IC options cannot meet all of these requirements. Ultra-low power (ULP) Application Specific Integrated Circuits (ASICs) provide the most efficient computing platform, and can function at low power consumptions with high computing power. Unfortunately, they have little or no flexibility, so updating or changing the functionality of the ASIC would require a full re-design and re-fabrication. This inflexibility also contributes to higher costs for implementation. General purpose processors (GPPs) that are targeted for low power, like ULP microcontrollers (MCUs), like the MSP430 from Texas Instruments, boast low power operation high flexibility and computing power[15]. However, the power consumptions of these devices is still too high for certain applications within the UbiComp space.

A more viable option is a ULP system-on-chip (SoC), like the Body-area Sensor Node (BSN) described in [27]. This device leverages both MCU and ASIC blocks to get extremely low power consumptions (<20  $\mu$ W), allowing the node to run on harvested energy. Battery-less operation is *perfect* for UbiComp applications. Unfortunately, devices like this one still suffer from lack of flexibility. Although the node can perform many functions (ECG, EEG, aFib detection, etc.), it is limited to those functions, and needs to be re-fabricated and re-designed for any changes or updates. Field Programmable Gate Arrays (FPGAs) are reconfigurable ICs that, at nominal voltages, split the difference between ASICs and GPPs in terms of flexibility and efficiency. The reconfigurability of the devices makes them inherently more flexible than ASICs, as they can be reconfigured to any functionality that fits on the logical resources available. Because FPGAs are still hardware implementations of algorithms, they still consume less power and energy than GPPs for many applications. The flexibility of FPGAs is limited to the amount of logic resources on the FPGA. Both ASICs and GPPs have been retargeted for ULP operation, as discussed earlier. However, there are fewer options for ULP FPGAs. This is primarily due to the current market for FPGAs. Applications today that primarily use FPGAs include aerospace, defense, automotive, high-power consumer electronics (like digital cameras), and medical devices (ultrasound, endoscopes, etc.), among others[13]. For these applications, power and energy consumption are not as important as performance. Thus, the FPGA industry has been driven by a different set of metrics, and designs for FPGAs have progressed accordingly. That being said, there are FPGAs from companies like Microsemi and Lattice Semiconductor that boast extremely low power consumptions[6][29]. But again, those devices still consume 10s of mW in active mode, which is high for the UbiComp requirements. If sub-mW FPGAs were to be realized, they would provide an ideal solution for UbiComp applications; a power-efficient computing platform that is also flexible and powerful. This proposal argues that if the circuits and architectures of FPGAs are retargeted for ULP operation, FPGAs can fill the space needed to realize UbiComp pervasively.

## 1.2 Motivation for Configuration Scheme for Custom-FPGAs

In order to adequately test whether circuit and architecture optimizations are valid for minimizing power consumption in FPGAs, it will be important to test how incremental changes effect the FPGA circuit as a whole. To do this, we will need to build schematics of FPGAs with the different circuitlevel and architectural parameters, and configure them to perform different functions. This poses two major problems.

- Design Time FPGAs are large structures, which require the use of a large number of transistors. One single configurable logic block (CLBs) consisting of 9 4-input basic logic elements (BLEs) can have as many as 20,000+ transistors (including test structures like registers). Thus, building entire FPGAs, which include multiple CLBs and a global interconnect, is very time consuming. Multiply that by the different FPGAs required for a thorough design space exploration, and comparing FPGA parameters through SPICE-level simulations becomes virtually impossible by hand.

- Configuration for Custom-built FPGAs As it stands now, there is no commercially available way to configure a custom-built FPGA fabric. Commercial FPGA companies, like Xilinx and Altera, have their own compilers that work for mapping a configuration bit stream that can be loaded to their hardware to implement verilog code provided by the user. Unfortunately, this method will not work for custom-FPGAs, because the custom hardware (circuit designs and architectures) doesn't match the commercial tools. Configuration bit locations are different, so the configuration bit stream wouldn't configure the same configuration bits. Configuration mechanisms vary from FPGA to FPGA, so it's entirely possible that the configuration bit stream generated by the commercial tool would be completely invalid for the custom FPGA built. Moreover, the underlying architectures will vary for commercial FPGAs, meaning that algorithms will be partitioned to different amounts of logic and interconnect resources. For all of these reasons, using commercial configurations is impossible for custom

fabrics.

What is needed is a method of taking a set of circuit level and architectural parameters (which define your physical FPGA structure) and a function for the FPGA to implement, and generating from those a netlist ready for simulation.

#### **1.3** Thesis Statement

By re-targeting circuit elements and architecture parameters of reconfigurable fabrics for ultralow power operation, FPGAs can provide the adequate combination of efficiency, flexibility, and computing power to enable ubiquitous computing to become a reality. These fabrics could be deployed as stand-alone ICs, or be included in ultra-low power SoCs to increase their flexibility. In order to study FPGA circuits and architectures fully, the FGC toolflow is created to generate FPGA fabrics, and configure them with algorithms used in ULP applications, in order to see how they will function. The tool extends open source FPGA mapping tools (i.e. the Verilog-to-Routing (VTR) flow [26]) to generate configurations for FPGAs. These generated FPGAs are used to explore circuit-level and architectural parameters to find optimal solutions for ULP FPGAs to target ULP applications like UbiComp.

## 1.4 Goals

The overarching goal of this work is to explore and determine circuit designs and architectures to allow FPGA operation with extremely low power consumption (<1mW). The individual goals of the work are as follows:

- Develop a tool-flow enabling circuit-level and architectural co-optimization for FPGA fabrics

- Explore viable circuit designs for FPGA sub-circuits (logic blocks, interconnect structures, and configuration bits)

- Determine best practices for FPGA sub-circuit design

- Re-visit FPGA architectures to determine if there are better architectural parameters for ULP FPGAs

- Determine optimal FPGA architectures for different classes of ULP applications

- Leverage toolflow to create FPGA fabrics that perform tasks with ultra-low power and energy consumptions

• Use toolflow to help create embedded reconfigurable fabric to be used in ULP SoCs, illustrating the benefits that ULP FPGA fabrics can provide

# 2 Background

# 2.1 General FPGA Architecture

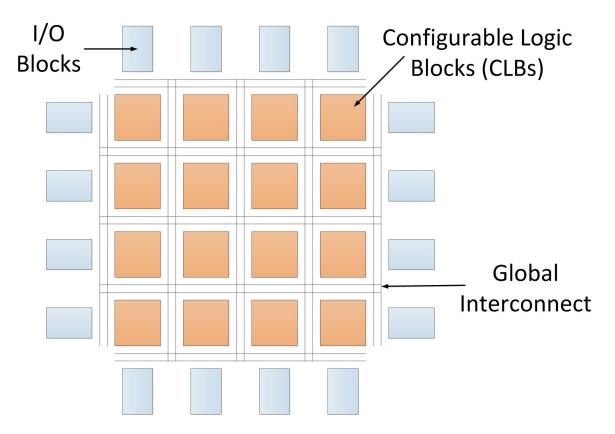

FPGAs are reconfigurable ICs that consist of a collection of distributed logic blocks whose inputs and outputs are connected to each other through a reconfigurable interconnect, filled with switches and buffers. Configuration bits (usually SRAM) are distributed through the FPGA and control the reconfigurable interconnect and the logic, and these configuration bits, if altered, can change the functionality of the logic blocks, the connections between different logic blocks, or both. The I/Os to the FPGA chip also include configuration bits that determine whether it will be an input or an output, allowing flexibility in the number of input and output pins the device has. A high-level illustration of the general FPGA architecture is shown in Figure 2.1.

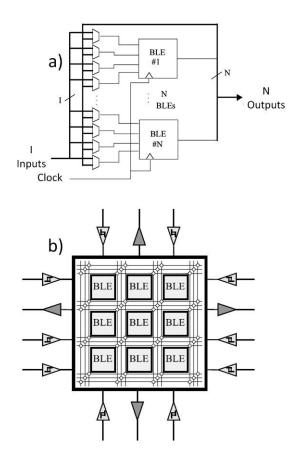

Each configurable logic block (CLB) consists of one or more Basic Logic Elements (BLEs). These

Figure 2.1: A 4x4 2D-mesh FPGA. Configurable Logic Blocks (CLBs) are distributed and connected to each other and input/output (I/O) blocks by a reprogrammable global interconnect.

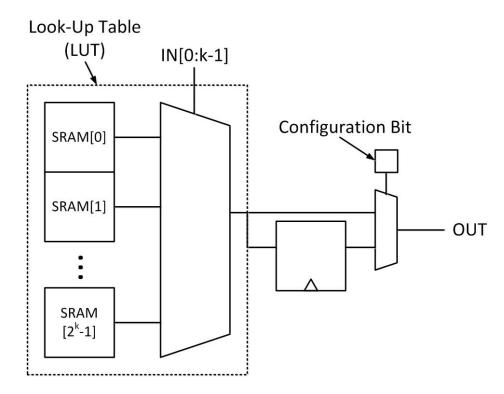

BLEs include a look-up table (LUT), a flip-flop (FF) and a multiplexer (mux). A k-input LUT is implemented by  $2^k$  SRAM configuration bits that hold the truth table values of any k-input Boolean function. Those bits are then fed into a  $2^k$ -to-1 mux, whose select signals are controlled

by the inputs of the BLE. The output of the LUT is then connected to both an additional output mux and the input of a FF, whose output is connected to the other input of the output mux. The output mux is controlled by a configuration bit, which determines if the BLE is purely combinational, or if it will utilize the FF to perform sequential logic. A detailed image of the BLE is shown in Figure 2.2. The global FPGA interconnect is generally organized as a 2-dimensional mesh structure

Figure 2.2: A basic logic element (BLE). One k-input look-up table (LUT) has  $2^k$  SRAM configuration bits that are connected to a  $2^k$ -to-1 multiplexer. The LUT is either configured to be combinational or sequential by a multiplexer and a configuration bit at the output.

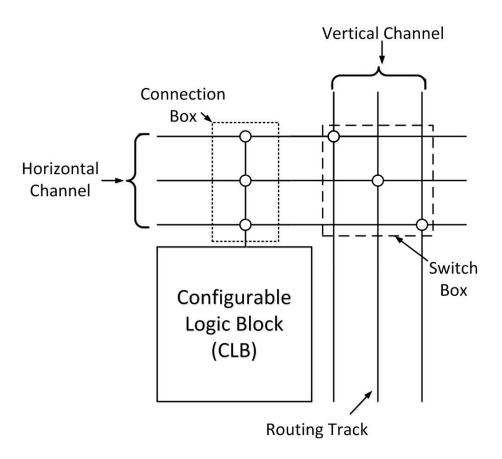

with horizontal and vertical wires. In 2D-mesh FPGAs, each individual wire is considered a "track," and the collection of adjacent tracks in a given direction are called "channels." Horizontal and vertical channels are connect to each other through switch boxes. Connection boxes connect the CLBs to the FPGA interconnect wires. Configuration bits control which tracks are connected to each other and to the CLB inputs and outputs. Figure 2.3 gives a detailed picture of interconnect resources and how they are connected.

## 2.2 Commercial Ultra-Low Power FPGAs

Most of the market share for FPGAs is shared by Xilinx (47%) and Altera (41%) as of 2012[31]. However, these companies do not make FPGAs with low power consumptions. These companies'

Figure 2.3: Programmable FPGA interconnect. Connection boxes connect signals from CLBs to individual routing tracks of horizontal and vertical routing channels. Switch boxes connect the channels to each other.

current consumption are consistantly in the mW-W range, which is too high for ULP applications. There are companies, however, who do make FPGAs with power consumptions in certain modes that are sub-mW, and their circuit designs and architectures are described in this section.

#### 2.2.1 Microsemi IGLOO nano

One of the competitors to Xilinx and Altera is Microsemi, a company that makes some of the lower power FPGAs on the market. Their devices use non-volatile FLASH configuration bits instead of the SRAM bits that most industry FPGAs use. By using these, they can get leakage currents for their devices as low as 2  $\mu$ W. The smallest logical element in the IGLOO nano, which is analogous to a BLE, is called a VersaTile, which is a 4-input block that can have one of three functions:

- 1. 3-input LUT

- 2. Latch with clear or set

#### 3. D flip-flop with clear or set

The IGLOO has no explicit clustering of their VersaTiles, but clusters are implicitly created by the routing structures in the FPGA. There are multiple levels of hierarchy in the interconnect of the IGLOO. First, there are Local-Line resources that connect every VersaTile with its eight nearest neighbors. Next, Long-Line resources span 1, 2, or 4 VersaTiles, in either the x or y direction. Lastly, there are Very-Long-Line resources that act as the global interconnect for the FPGA, which span 12 versatiles in the x-direction and 16 VersaTiles in the y-direction. Because of the Local-Line interconnects, we will consider the cluster in these FPGAs to be 9 VersaTiles [6].

#### 2.2.2 Lattice iCE40 Ultra

Lattice Semiconductor is a company who designs SRAM-based FPGAs for low-power operation. Their iCE40 device boasts typical standby currents of 71  $\mu$ A, with IP cores including embedded block RAMs, communication interfaces, and DSP blocks. The device clusters 8 4-input LUTs into each programmable logic block (PLB). Like other commercial FPGAs, their logic blocks have dedicated carry logic for more efficient arithmetic functionality. Their routing structure consists of three different segment lengths spanning 1, 4, and 12 PLBs [29].

# 2.3 Academic Ultra-Low Power FPGAs

While some commercial FPGAs (like the Microsemi IGLOO and the Lattice iCE40) have sub-mW operation, they only achieve this low power consumption in sleep mode. There have been academic ventures to design ultra-low power FPGA designs that consume low power actively. One example is introduced in [9], which features a low power FPGA that consumes as little as 40  $\mu$ W in the active mode. This FPGA uses 6T latches instead of SRAM bits that are used in commercial FPGAs. For interconnect resources (such as connection boxes and switch boxes), this FPGA uses buffered, unidirectional wires with buffered multiplexers at the switch points. Limitations to this FPGA design come mostly from the size of the device. This FPGA achieves record-low power consumption, but only has 4 configurable logic blocks. That severely limits the computation power of the device, and almost assuredly is not enough resources for many of the DSP algorithms needed for UbiComp.

Another low-power FPGA, proposed in [33], uses the Xilinx Stratix III architecture as its baseline. Thus, it also uses standard SRAM configuration bitcells and buffered unidirectional multiplexers for the interconnect routing as well. This FPGA included IP blocks like multipliers and block RAMs. The low-power optimizations employed in this FPGA include mid-oxide, high-VT transistors in the

| Table 1: FFGA architectures of commercial and academic low-power FFGAs |              |                                    |             |               |  |  |  |

|------------------------------------------------------------------------|--------------|------------------------------------|-------------|---------------|--|--|--|

| FPGA                                                                   | Size         | Power                              | Config. Bit | Frequency     |  |  |  |

|                                                                        | (#  of LUTs) | $(\mu W)$                          | Topology    | (MHz)         |  |  |  |

| Latice iCE40 <sup>1</sup>                                              | 384-7680     | Static: 21-250                     | SRAM        | 275           |  |  |  |

|                                                                        |              | Active: just $\downarrow 1k^{7,8}$ |             |               |  |  |  |

| Microsemi                                                              | 100-3000     | Static: 2                          | FLASH       | 160-250       |  |  |  |

| IGLOO nano <sup>1</sup>                                                |              | Active: $400^6$                    |             |               |  |  |  |

| Ryan et. al. $[28]^2$                                                  | 1134         | Static: $\sim 35^{3,4}$            | 5T-SRAM     | $\sim 33^{3}$ |  |  |  |

|                                                                        |              | Active: $\sim 12.5^{3,4}$          |             |               |  |  |  |

| Grossmann et.                                                          | 128          | Static: 8.9                        | 6T Latch    | 16.7          |  |  |  |

| al. $[9]^2$                                                            |              | Active: 34.6                       |             |               |  |  |  |

| Tuan et. al. $[33]^2$                                                  | 1500-15000   | Static: 46-460                     | SRAM        | $244^5$       |  |  |  |

|                                                                        |              | Active: 13k-130k                   |             |               |  |  |  |

Table 1: FPGA architectures of commercial and academic low-power FPGAs

$^{1}$  – Commercial ULP FPGAs

<sup>2</sup> – Academic ULP FPGAs

$^{3}$  – Estimated from plots in the paper

$^{4}$  – Simulation result for 780 LUTs

<sup>5</sup> – Reported approx. 27% reduction from Xilinx Spartan-3

<sup>6</sup> – Obtained from Microsemi Power Calculator worksheet

$^{7}$  – Mid-range iCE40 model

<sup>8</sup> – From news article in EE times: Ultra-low power FPGAs enable always-on sensor solutions for context-aware mobile apps

configuration bits. They also power-gate unused resources, and have a stand-by sleep mode. With these techniques, this FPGA consumes 13-130mW of active power and 46-460 W of sleep power for 1500-15000 logic cells (BLEs).

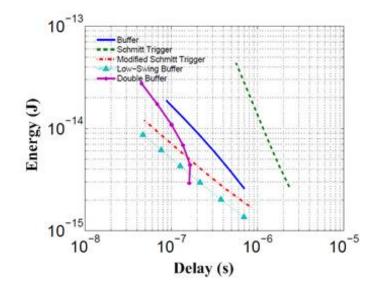

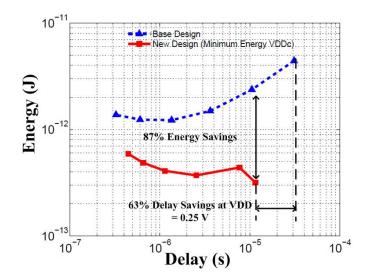

In [28], researchers also used SRAM bitcells for configuration, but used 5T cells as opposed to the standard 6T. This made the cells harder to write, but because the cells are generally in the hold state, using 5T configuration bits only requires extra effort during the configuration stage, in the form of boosted voltages for the writing circuitry. For the interconnect, this FPGA doesnt use buffers at all, but instead uses a purely pass-gate interconnect. To make up for the degraded swing across the interconnect, a modified-Schmitt Trigger sense amp is used at the inputs to the logic blocks in order to restore the signal to full swing. This interconnect leverages the low-swing that occurs throughout the interconnect to reduce power. Using these circuit design techniques, researchers were able to reduce area per LUT by almost 3x, delay at a constant energy by 14x, and energy at a constant delay by almost 5x.

Table 1 shows different low-power FPGAs and their architectures. Both the commercial and academic FPGAs cover a wide range of capacities. In terms of power consumption, only the academic have power consumptions that fall within the UbiComp speces (<1 mW). The different FPGAs use a variety of bitcell topologies, which inspires the bitcell exploration in chapter 5. It is also important to note that all of the frequencies in this table are much higher than necessary for UbiComp

applications, which range from 100s of kHz to MHz. That suggests that there is room for further reducing power for FPGAs at the expense of performance.

# **3** FPGA Generation and Configuration (FGC)

# 3.1 Motivation

There are many circuit and architectural knobs that need to be turned in order to design an FPGA that is optimized for ULP functionality. While testing each individual knob (such as switch topology) can provide interesting information, its also very important to see how these knob changes affect the functionality of the FPGA as a whole. FPGA modelling (like what is done in VTR) can provide some notion of how the full FPGA fabric behaves with different circuit-level and architectural parameters, but a more accurate representation of the circuit performance would be to conduct SPICE-level simulations of FPGA fabrics. To do this, it is necessary to build full FPGA schematics. employing the different circuit-level and architectural parameters to be tested, configuring them to perform some function, and simulating them. However, there are many challenges to conducting these FPGA-level simulations. First, we are exploring multiple knobs, creating potentially 1000s of different combinations for FPGA fabrics. Each one of those FPGAs is also a large IC, using 1000s of transistors. As a result, building the necessary FPGA schematics by hand becomes impossible, given time and monetary constraints. Secondly, in order to simulate these FPGAs, they need to be configured to perform certain tasks. Unfortunately, no tool is readily available for configuring custom-built FPGAs. Commercial FPGAs have their own compilers for configuration, but these software packages are specific to their own FPGA products, and will not work for our custom-built FPGA fabrics. In this chapter the FPGA Generation and Configuration (FGC) tool is introduced. This tool not only generates FPGA fabrics based on circuit-level and architectural parameters, but that can also create configurations for those FPGA schematics in order to conduct SPICE level simulations.

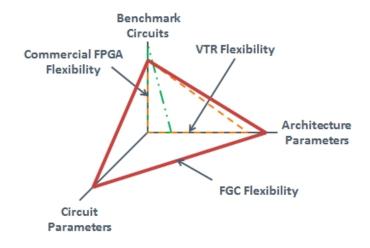

The design space of FPGA hardware design can be abstracted to 3 axes of flexibility: circuit parameters, architecture parameters, and benchmark circuit designs. Commercial FPGA companies, like Xilinx or Altera, allow for large flexibility in terms of the types of circuits that can be mapped to them, but are extremely limited otherwise. They provide only one alternative in terms of circuit parameters, and a small set of different architectures, ranging from smaller, low-end devices to large high performance devices. The VTR tool [26] is slightly limited in the types of benchmarks it can map (due to the inflexibility of the included CAD tools to Verilog syntax), but has a large range of architectural flexibility, meaning it can handle a large design space in architectural parameters. Our proposed tool-flow will cover a much larger portion of the possible design space, and be able to cover both architectural and circuit-level knobs while also leveraging a variety of benchmark circuit algorithms. Figure 3.1 gives a graphical representation of the design space and how other tool-flows fit into it.

Figure 3.1: Graphical representation of FPGA hardware design space. Proposed tool-flow will address all three portions of the design space to move beyond other tools capabilities.

# 3.2 FGC Overview

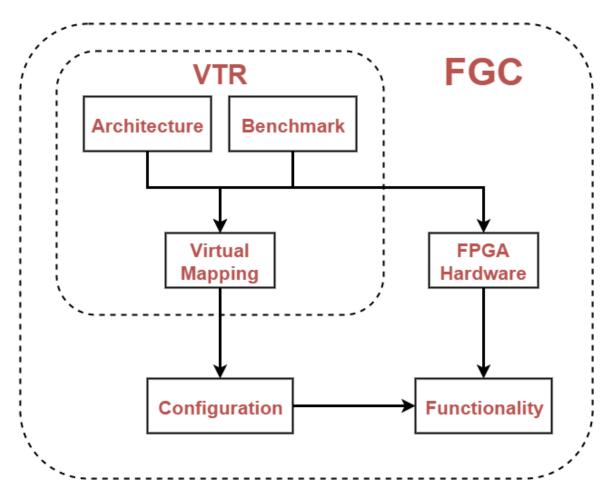

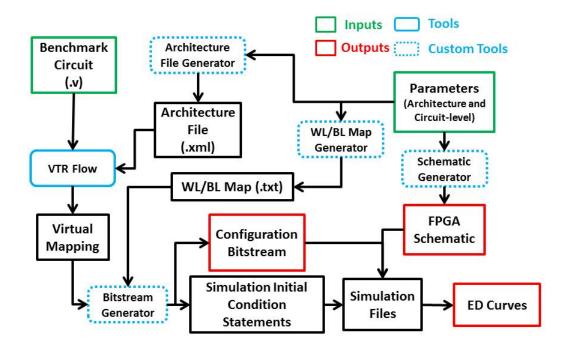

The FPGA Generation and Configuration (FGC) tool-flow, which I created, allows users to quickly generate full-FPGA schematics, configure them to perform any Verilog-based function, and prepare simulations to be run by the user to observe metrics of interest. It does so by extending the VTR toolflow [26], as illustrated in Figure 3.2. This tool-flow leverages the VTR toolset to configure an FPGA with the architecture of our choosing, Cadence SKILL scripts to build schematics, and perl code to edit and generate scripts and text files, and control the different tools used. The FGC flow primarily targets researchers looking to build custom-FPGA fabrics, and allows them to explore new circuit- and architecture-level design choices, and see the effects of these changes at an FPGA-system level. This tool is also useful for designers making systems-on-chip (SoCs) looking to potentially include FPGA fabrics. Additionally, the FGC tool requires minimal user input, allowing a user who is not an expert in FPGAs to still use the tool-flow. Figure 3.3 is a flow-chart describing the FGC toolflow.

Figure 3.2: High-level picture of the FGC flow. The capabilities of the VTR flow [26] are extended to include generated FPGA schematics and simulation results for given benchmark circuits.

# 3.3 Prior Art

Various methods for generating configurations for custom-built FPGAs exist, but with varying limitations. In [30], researchers develop a bitstream generator, called DAGGER, as part of their larger research effort to create a custom FPGA. DAGGER focuses on creating bitstreams for their specific FPGA architecture and includes additional functionality, such as partial reconfigurability, bitstream compression and encryption. [30] also highlights the many other bitstream generators/editors ([10],[23],[11],[25]), but all of these tools target Xilinx FPGAs specifically. The FGC tool described in this dissertation has different goals, and is instead designed for allowing design space exploration across many different architectures and circuit-level designs.

In [17], researchers at University of Toronto extend the VTR toolflow to include physical synthesis and place and route using commercial synthesis tools (i.e. Cadence, Synopsys, etc). The flow also generates bitstream configurations for the synthesized FPGA. This provides a path toward SPICE-

Figure 3.3: Flow-chart of the FGC flow. The inputs are a parameter file explaining the target FPGA circuitry, and a benchmark Verilog circuit describing the target FPGA functionality. The flow creates a full FPGA schematic and configuration files representing the functionality, and can be used to generate simulation results.

level simulations for FPGA fabrics that at least span the flexibility of the VTR tool. The FGC tool developed for this dissertation takes this level of flexibility a step further, and includes circuit-level parameters (like transistor sizing, additional circuit topologies, etc.) that are not included in the VTR tool. Additionally, the tool provides initial condition statements for simulation as well as bitstream, giving the user direct control over individual configuration bits, to quickly assess functionality without needing to simulate configuration, which can take prohibitively long. These configuration generation schemes above have the following drawbacks, which are addressed by this new FGC flow that I have developed.

• **Bitstream configuation only** – Both DAGGER and the VTR extension simply create configuration bitstreams. Thus, to simulate FPGA functionality, the user must also simulate the configuration each time. This can take prohibitively long for larger FPGAs, and will greatly increase design space exploration time regardless of size.

- Lack of flexibility Both of these approaches have limits in the amount of the design space that can be explored. The DAGGER flow is made specifically for the AMDREL FPGA, and only works with FPGA fabrics with similar architectural and circuit-level parametes. The VTR extension has increased flexibility, but is limited to the level of flexibility of the VTR tool, which is primarily flexible with respect to architectural parameters (LUT size, CLB clustering, channel width, etc.)

- Incomplete flow In order to efficiently explore the design space, one needs to vary multiple parameters, including circuit-level parameters, architectures, circuit functionalities, and operating conditions, and simulate across this large design space. In order to do this, FPGA fabrics need to be generated, configured, and simulated. The DAGGER tool and the VTR extension include one piece (configuration) of the puzzle.

The proposed FGC tool achieves all three goals. It completes the loop, going from design parameters and ending with simulations of FPGA fabrics. The configuration includes initial condition statements, allowing users to simulate FPGAs without having to also simulate configuration. This tool is the most flexible FPGA-generation or configuration tool to date, allowing for different circuit-level and architectural parameters, operating conditions, target Verilog circuits, and simulation options.

# 3.4 Running the FGC flow

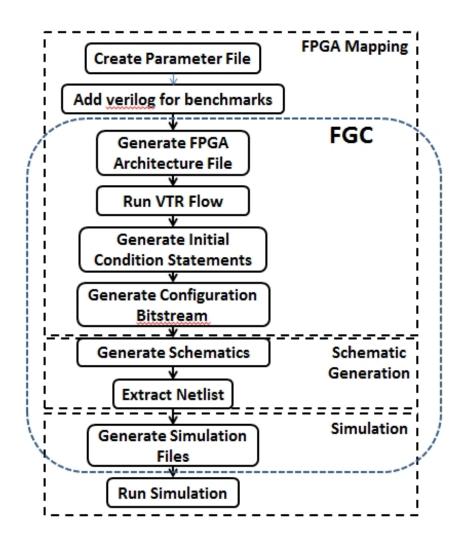

Figure 3.4 outlines the steps to perform in order to run the flow. The flow is divided into 3 sections: mapping, schematic generation, and simulation. First, the user sets up the toolflow by creating a parameter file, which is the main input for the toolflow. This file provides descriptions of both architectural and circuit-level parameters for the target FPGA to be generated. Next, the user places verilog code for the benchmark(s) to be mapped to the target FPGA within the FGC file structure in the correct directory. After placing the verilog files, the first portion of the toolflow can commence, which generates the necessary files for FPGA configuration, which can be either initial condition statements for the configuration bits, or a configuration bitstream which can be used either in a chip-level simulation, or for hardware configuration. Once these files are generated, the user then creates the schematics by setting up a library in the proper schematic environment, running a SKILL script to generate all of the FPGA schematics, and extracting the netlist of the full FPGA circuit. Following the schematic generation steps, the user can then run the second portion of the toolflow, which uses the mapping of the FPGA as well as the netlist to generate a set of simulation files, and kick off a simulation to observe metrics such as delay and energy. In the

Figure 3.4: Steps for running the toolflow. The toolflow is divided into 3 sections: FPGA mapping, schematic generation, and simulation. File names and directory locations are also provided.

following sub-section, I give a more detailed, step-by-step tutorial for running the FGC Flow.

#### 3.4.1 Step-by-Step FGC Flow

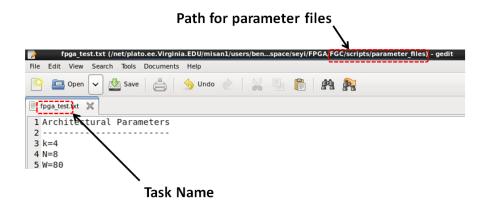

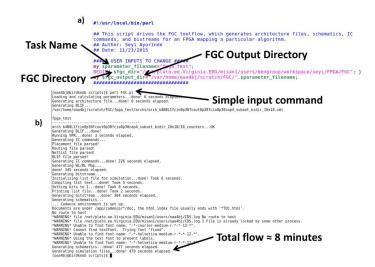

Step 1: Create Parameter File The first step for the toolflow is generating the input parameter file, titled <task name>.txt, where <task\_name> will be the name that will organize all of the outputs of the flow. A template parameter file is included with the flow, and copying the template, renaming it, and changing the values of the parameters ensures that all of the necessary parameters are set. Figure 3.5 illustrates the parameter file opened in a text editor.

Figure 3.5: Excerpt from an example parameter file. The **task name** (used to organize the outputs) and the file location are highlighted.

**Step 2:** Add Verilog Circuits to FGC Flow Before running the flow, the user needs to add Verilog descriptions of the circuits that are to be mapped to the generated FPGA for testing. These Verilog files are to be placed into the FGC/vpr\_files/verilog/<task name> directory, which needs to be created as well. Multiple Verilog files can be added, and the FGC tool supports multiple configurations in one run. The tool will generate multiple outputs, one for each circuit to implement.

Step 3: Edit and Run FGC Flow Now that the parameter file and Verilog circuits are in place, the user can kick off the toolflow. First, the driver script for the flow (FGC.pl) should be opened and edited. Only the top 3 lines of the script need to be changed. The **\$parameter\_filename** variable should match the task name in steps 1 and 2. **\$fgc** is the location of the FGC flow, and **\$fgc\_output\_dir** is the location for all of the outputs to be generated (called FGC\_OUT\_DIR from now on). Figure 3.6a shows the script and the lines of code to edit. Once the script is properly edited, the script can be executed with the following command in the terminal:

## perl FGC.pl

The script performs the following functions:

- 1. Runs the VTR flow to generate a virtual mapping of the FPGA

- 2. Generates initial condition (IC) commands for configuring FPGAs to perform target Verilog functions

- 3. Generates configuration bitstreams for true FPGA configuration of target Verilog functions

- 4. Generates full FPGA schematics

- 5. Generates simulation files (including netlists, stimuli, and driver scripts) for analysis of FPGA behavior

Figure 3.6 shows the terminal output after running the FGC flow. In this example, a 10x10 FPGA is generated, and configured with 10 4-bit counters. The total runtime for the flow is approximately 8 minutes, not including simulation time.

**Step 4: Edit Stimulus** Upon completion of the FGC flow, simulation files will be available for simulation, located in the **FGC\_OUT\_DIR/simulation\_files** directory. A sub-directory exists for each target circuit that is mapped. For the simulations to be functional, the user must change the stimulus in order to see the functionality. The default stimuli are piece-wise linear (PWL) inputs for each input signal specified in the Verilog for the target functionality. The onus is on the user to set up the stimulus such that the critical path of the FPGA is exercised in the simulation. The simulation driver script (**sim.sp** for HSPICE and HSIM, **sim.scs** for Spectre or UltraSim) in the simulation file directory shows the input and output signals of the critical path, and uses those signals to calculate delay. It is up to the user to use that information to set up the stimulus properly.

Step 5: Run Simulation Once the stimulus is edited, simulations can be run using the generated files. To run the simulation, navigate to the FGC\_OUT\_DIR/simulation\_files/<simulator>/

<circuit> directory and run the following command:

#### bash run\_sim.sh

Simulation data is saved to the FGC\_OUT\_DIR/sim\_results/<circuit> directory, and delay and energy calculations are saved into <circuit>.mt file in the FGC\_OUT\_DIR/simulation\_files/ <simulator>/<circuit>/<voltage> directory.

Figure 3.6: a) FGC.pl driver script, with task name, FGC directory, and FGC output directory highlighted. b) Single FGC run for 10x10 FPGA. Schematic, initial condition, bitstream, and simulation file generation all together takes about 8 minutes.

# 3.5 Architectural Assumptions in FGC

There are a set of assumptions that I have made in designing this FPGA-synthesis toolflow.

#### 3.5.1 Inputs to CLBs

The number of inputs to the CLB is a variable that has been well studied. In this dissertation, I use the equation derived in [2], namely that

$$I = k\left(\frac{N+1}{2}\right)$$

where I is the number of inputs to the CLB, k is the number of inputs to an LUT, and N is the number of BLEs in the CLB.

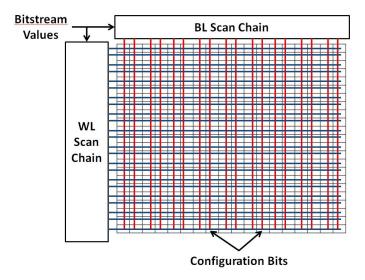

#### 3.5.2 Word-line (WL) and Bit-line (BL) configuration

In this toolflow, the FPGA is assumed have its configuration bits (CBits) arranged through a network of horizontal word-lines (WLs) and vertical bit-lines (BLs), similar to an SRAM. WLs control access to CBits, and BLs control the value written into the CBits. Figure 3.7 illustrates the configuration mechanism. The tool does not yet support single bitstream configuration topologies, where each configuration bit is part of a large scan chain that can be scanned in through one port. Future work will include expanding the FGC flow to support additional FPGA configuration topologies.

Figure 3.7: Dual scan-chain configuration for FPGAs. Bitstreams are generated for both the WL and the BL scan chains, such that each configuration bit (CBit) is written with the proper values. WLs control access, and BLs control values to be written into the CBits.

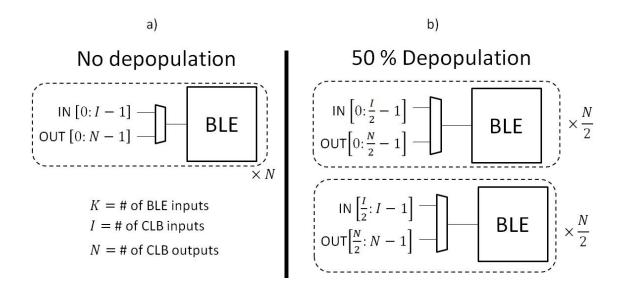

#### 3.5.3 Depopulation Implementation

Multiplexer Depopulation (as discussed in [20]), refers to accessing less than 100% of the possible inputs for basic logic element (BLE) inputs. Without depopulation, multiplexers for BLE inputs can select from all of the inputs and outputs of the larger configurable logic block (CLB), which includes one or more (N) BLEs. With depopulation, the muxes have a percentage of the total signals to choose from. The FGC flow implements depopulation by accessing the proper proportion of inputs and outputs. An example is shown in figure 3.8. When the depopulation is 50%, the BLE input connects to half of the inputs, and half of the outputs. Complete connectivity to the BLE is achieved over multiple inputs, unless the depopulation is less than  $\frac{1}{K}$ , where K is the number of inputs to the BLE. The first  $N \times [depopulation]$  BLEs connect to the first subset of the signals, the second set of BLEs to the second subset of signals, etc. For example, if the depopulation is  $\frac{1}{3}$  and N = 9, then BLEs 1-3 connect to the first third of the inputs and the first third of the outputs, BLEs 4-6 connect to the second third of inputs and outputs, and BLEs 7-9 connect to the rest.

Figure 3.8: Example of BLE input multiplexers with a) 0% and b) 50% depopulation.

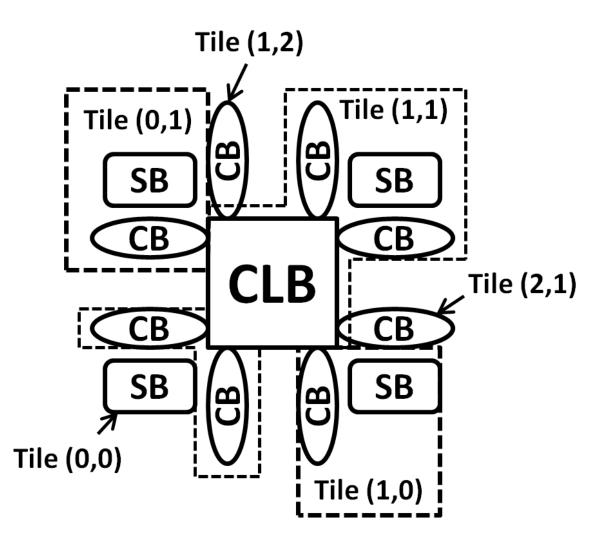

# 3.6 FPGA Tile

In this tool-flow, FPGA resources are organized into "tiles," which include a single CLB, all of the connection boxes attributed to that CLB, and the switch box in the top-right hand corner. Tile coordinates go from (0,0) to ([fpga width+1],[fpga height+1]). Tiles on the edges lack CLBs and include fewer connection boxes. Tiles on the right and top edges also have switch boxes removed, as the neighboring tile has the necessary switch box. The different blocks are labeled in Figure 3.9.

#### 3.7 FGC Directory Structure

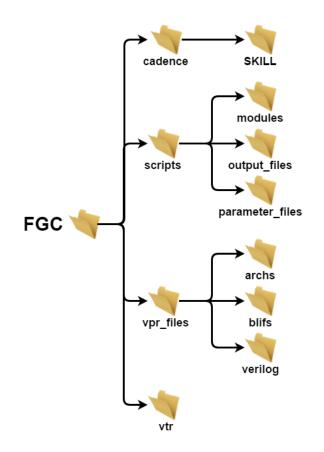

In this section, I explain the different directories within the FGC toolset, illustrated in Figure 3.10. The directory structure is very important, and needs to be maintained in order to guarantee tool functionality. There are a set of directories and files that are also generated by the tool, and the directory structure of these output files is also explained in this section. More information about the individual files in each directory can be found in the next section, entitled File Descriptions. The main FGC directory (**FGC**) has four directories inside:

- The **cadence** directory is the assumed launch location for Cadence Virtuoso, which will be used to generate the schematics for the FPGA. Because the schematic generation files are written in SKILL, Cadence Virtuoso is required for running them.

- The scripts directory houses the driver scripts for the FGC flow, as well as the modules which hold the sub-routines for generating all of the necessary files, and parsing all of the intermediate

Figure 3.9: CLB tile organization, illustrated in a 1x1 FPGA. CLB Tiles include CLBs, connection boxes, and a single switch box. Left and bottom edge tiles include connection boxes and switch boxes. Right and Top edge tiles include only connection boxes. The tile in the bottom left corner (tile 0,0) has only a switch box.

files. The user executes the FGC flow in this directory.

- The **vpr\_files** directory includes template architecture files for potential FPGAs, BLIF (Berkeley Logic Interchange Format) files, and Verilog code for potential benchmark circuits.

- The vtr directory is the open-source Verilog-To-Routing (VTR) mapping tool developed by University of Toronto. The FGC flow extends this tool to allow for schematic-level FPGA generation and configuration. The VTR flow can also be run stand-alone, as it was originally intended.

Figure 3.10: Directory structure for the FGC toolset. 'vtr' houses the Verilog-To-Routing (VTR) open-source tool. Most of the custom code resides in 'scripts'. Code to generate FPGA schematics is in the 'SKILL' directory

## 3.7.1 FGC Outputs Directory Structure

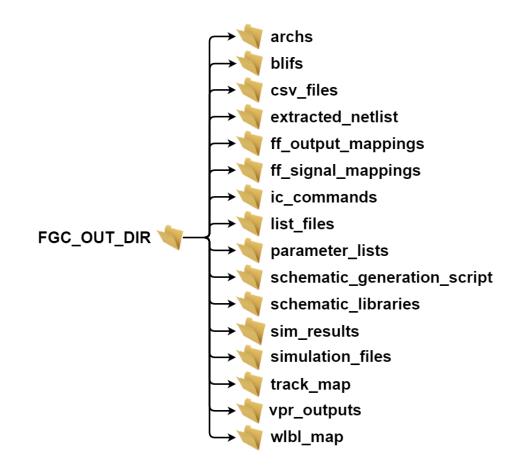

Once the FGC flow is completed, a set of output directories and files are generated. All of these outputs are generated in the FGC output directory (**\$FGC\_OUT\_DIR**). The location of that directory is specified by the user in the FGC driver script. The output directory structure is illustrated in Figure 3.11. The contents of the individual files will be discussed in greater detail in the File Descriptions section.

The following list describes each directory in the  $FGC_OUT_DIR$  directory:

- The **archs** directory is the location of the generated VPR architecture file, which provides descriptions of the target FPGA hardware used to map algorithms to a virtual FPGA through the VTR flow.

- The activity factors directory houses the activity factor file generated by the ACE tool, which is part of the power estimation flow (VersaPower) in VTR.

- The **blifs** directory is the location of the generated Berkeley Logic Interface Format (BLIF) file, which describes the logic of the target benchmark circuits to be mapped using the VTR flow.

- The **extracted\_netlist** directory is where the schematic for the full FPGA should be extracted after it is generated, allowing for successful simulation.

- The csv\_files directory holds a comma-separated value file that represents the bitstream for configuring the target FPGA. This file is generally used for the physical testing, as many pattern generators support CSV inputs.

- The **ff\_output\_mappings** holds the mapping between flip-flop names and verilog output signal names. The VTR outputs describe the FPGA output signals by the name given to the flip-flop that drives that signal. This directory is only generated for the mapping of sequential circuits.

- The **ff\_signal\_mappings** directory holds the mapping between the flip-flop name and the schematic net that refers to the Q-node of that flip flop. This allows for the delay calculations to choose the proper nodes in the schematics. This directory is only generated for the mapping of sequential circuits.

- The ic\_commands directory holds the initial condition statements generated by the toolflow for the FPGA schematics, in order to properly perform the target benchmark circuit functionality.

- The list\_files directory holds a representation of the stimulus file for streaming in the configuration bits. This is list file is used to generate other versions, including a comma-separated value (CSV) file (used by many pattern generators to generate stimulus for a chip) and a piece-wise linear (PWL) file (used for simulation).

- The **parameter\_lists** directory includes an updated version of the initial parameter list input to the toolflow, which includes calculated parameters as well. A full description of the additional parameters will be shown later in the document.

- The schematic\_generation\_script directory includes a copy of the SKILL code that is generated to create the FPGA schematic.

- The **schematic\_libraries** directory is where the Cadence library to hold the FPGA schematics should be.

- The **simulation\_files** directory is the location of the generated files (netlist, stimulus, etc) used for running simulations of the full-FPGA fabric.

- The **sim\_results** directory is the waveform data for the simulation is generated as the simulation of the generated FPGA schematic progresses.

- The track\_map directory holds the list of tracks that each FPGA I/O (both chip-level and logic-block-level) connect to. This is important for ensuring matching connectivity between the mapping that comes from the VTR flow and the schematics for the FPGA that are being generated by the SKILL code.

- The **vpr\_outputs** directory is the final location of the files that are generated by the VTR flow. More information on each of those files will be given in the File Descriptions section of the document.

- The wlbl\_map directory holds the generated WL/BL map file, which tells the WL and BL location of each configuration bit in the generated FPGA schematic.

# 3.8 File Descriptions

#### 3.8.1 Parameter file (<task name>.txt)

The main input for the toolflow is a parameter text file, which is located in the *\$fgc/scripts/parameter\_files* directory. This file includes the following information:

- 1. architectural and circuit-level parameters for the target FPGA

- 2. options for running virtual place and route (VPR)

- 3. simulation options

Architectural Parameters The architectural parameters are as follows:

- k number of inputs to each look-up table (LUT) in the target FPGA.

- **N** number of basic logic elements (BLEs) clustered inside each configurable logic block (CLB) in the target FPGA.

- W channel width, or the number of routing tracks in each routing channel. If left as *VPR*, VPR will determine the number of routing channels.

Figure 3.11: Directory structure for the generated FGC outputs. These outputs are the intermediate files for the toolflow, and provide visibility for debugging purposes. All of the directories are generated by the toolflow.

- L segment length, or the number of CLBs each routing segment spans.

- fc channel fanout, or the percentage of tracks in each routing channel that each pin connects to. The parameter file calls for 3 different channel fanout values: one for the input pins of logic blocks, one for the output pins, and one for the I/Os of the FPGA.

- I/O capacity number of physical ports at each X-Y location for an I/O block. If I/O capacity is equal to *n* each I/O block in the FPGA will have *n* inputs and *n* outputs.

- **FPGA width and height** overall dimensions of the target FPGA, in terms of number of CLBs. If left as *VPR*, VPR will determine the dimensions for the FPGA.

- CLB width and height dimension of the CLB, in terms of number of BLEs.

- **Track directionality** sets the tracks to be either uni-directional (signals can only pass in one direction) or bi-directional (signals can pass in both directions).

- Logical Equivalence sets the logical equivalence of the inputs to logic blocks in the FPGA. A value of *true* means that the inputs are interchangeable, and are therefore logically equivalent. A value of *false* means the inputs to the logic blocks are not interchangeable.

- Depopulation (multiplexer-based CLBs only) sets the amount of depopulation in the input multiplexers of each BLE. Values range from 0 to 1.0. Depopulation of 0.33 means that each BLE input multiplexer connects to 0.66 of the possible signals (inputs and outputs) of a CLB.

- W\_clb (mini-FPGA CLBs only) sets the channel width of the intra-CLB routing in a mini-FPGA CLB.

Circuit-level Parameters The circuit-level parameters are as follows:

- **clb\_type** sets the type of intra-CLB connectivity. At this point, the supported options are *mux* and *minifpga*.

- clb\_powergate chooses whether or not CLBs in the FPGA are power-gated.  $\theta$  omits power gates, and 1 includes them.

- clb\_powergate\_size sets the size of the power gates, measured in minimum transistor widths (e.g. clb\_powergate\_size=300 means the power gate is 300× the minimum width for the technology).

- **sbox\_type** sets the switch box topology of the switch box. At this point, the supported switch box topologies are *subset*, *wilton*, and the custom *folded\_subset*, designed here at UVa.

- **sbox\_powergate** chooses whether or not switch boxes in the FPGA are power-gated.  $\theta$  omits power gates, and 1 includes them.

- **sbox\_powergate\_size** sets the size of the power gates, measured in minimum transistor widths.

- **spoint\_wls** sets the number of word-lines (WLs) for the switch points that make up the switch boxes in the global interconnect of the FPGA.

- **spoint\_bls** sets the number of bit-lines (BLs) for the switch points that make up the switch boxes in the global interconnect of the FPGA.

- **lut\_switch** sets the switch topology for the switches inside the look-up table (LUT). This includes the transistors in the *k-1* multiplexer, as well as the output multiplexer that chooses between combinational and sequential functionality. Switch options supported by FGC are *pg* for pass gates, *tx* for transmission gates, and *tristate* for tri-state buffers.

- **ble\_switch** sets the switch topology for the switches inside the basic logic element (BLE). In multiplexer-based CLBs, this option controls the switches in the input multiplexers, which route the inputs and outputs of the larger configurable logic block (CLB) to the individual BLEs. In mini-FPGA style CLBs, this option also determines the switch topology in the intra-CLB interconnet, namely switch boxes and connection boxes. Switch options supported by FGC are *pg* for pass gates, *tx* for transmission gates, and *tristate* for tri-state buffers.

- **fpga\_switch** sets the switch topology for the switches in the global interconnect of the FPGA. More specifically, this option controls the switches in the switch boxes and connection boxes. Switch options supported by FGC are *pg* for pass gates, *tx* for transmission gates, and *tristate* for tri-state buffers.

- **ble\_switch\_size and fpga\_switch\_size** sets the width of the transistors in the switches in the interconnect of the BLE and FPGA, respectively. Width is measured in minimum-widths of the technology.

- cbox\_wls\_vert sets the number of word lines (WLs) for connection boxes connecting to the vertical channels in the FPGA. The number of bit lines (BLs) needed for these connection boxes is determined by the channel width (W) and the channel fanout for that pin (fc).

- cbox\_bls\_horz sets the number of bit lines (BLs) for connection boxes connecting to the horizontal channels in the FPGA. The number of WLs needed for these connection boxes is determined by the channel width (W) and the channel fanout for that pin (fc).

- cbox\_vert\_spacing and cbox\_horz\_spacing sets the number of WLs or BLs between adjacent connection boxes. In building FPGA layouts, it became apparent that additional space was needed for the connection box, such that another connection box could not fit on the adjacent WL or BL.

- mux\_type sets the multiplexer topology. The options thus far are *full*, *two\_level*, and *flat*.

- **mux\_buffering** determines how much buffering for the multiplexers. The options supported by FGC are *none*, *single\_buffer*, and *full*.

#### **VPR Options** The VPR options are as follows:

- graphics\_display controls whether the VPR graphics come up when VPR is running. The options are either on or off

- exit\_temp controls the exit temperature (i.e. the number of iterations) of the temperature annealing algorithm used for the placement of logic blocks through the VPR. A lower number results in more iterations, and the default value in VPR is 0.01. I found that certain, smaller benchmark circuits would not map to large FPGAs with limited routing resources, because all of the I/Os and logic blocks would be packed together in a corner, and most of the routing resources wouldn't be used. By raising this exit temperature, you can ensure that the blocks are more spread out through the FPGA, resulting in sub-optimal placement, but successful routing.

- **power\_analysis** determines whether or not the power estimation flow (VersaPower) is used in the VTR mapping. This flow provides an estimation of power consumption, but only works for sequential circuits.

**Simulation Options** The simulation options are as follows:

- **benchmarks** list of the verilog circuit implementations to map onto the target FPGA, separated by spaces

- benchmark\_types list of the types of circuits listed above, either combinational or sequential. This list must be the same size as the list of benchmark circuits.

- **simulator** chooses the simulator to create the schematics for. Supported simulators include *spectre*, *ultrasim*, *hspice*, and *hsim*.

- scan\_chains chooses whether or not scan\_chains for configuration are to be included in the FPGA schematic

- models\_path points to the transistor-level models file that will be used in the simulations

- design\_path points to the location of the design file that will be used in the simulations

- corner design corner to simulate in. Supported options are tt, ff, ss, fs, and sf.

- **save\_select\_signals** determines whether or not to save specific individual nets.  $\theta$  saves all of the voltages and currents, and 1 saves only the inputs, outputs, and supply voltage currents.

- vdd supply voltage of the FPGA fabric. Multiple VDDs can be listed, and the simulation will run for each voltage

- vddc configuration bit supply voltage. A separate voltage supply is used for the interconnect circuitry in the FPGA to observe the effects of changing that voltage on overall system performance and efficiency. Multiple VDDc's can be used, but the number of VDDcs must match the number of VDDs. If the goal is to simulate a single VDD with multiple VDDc's, then the VDD list is the single VDD three times

- simulation\_time the length of time for the transient FPGA simulation

- frequency Frequency of clock signal (used for sequential FPGA circuit implementations

- $\bullet \ step\_size$  sets the transient simulation step size

- buffer\_size Option for size of the bitstream stimuli. Because FPGA bitstream stimuli tend to be large, this option specifies the maximum size (# of lines) of any bitstream file, and will break the bitstream stimulus into multiple files, each with a maximum size of the specified buffer size.

- stimulus\_type Chooses the format of the stimulus. standard creates a simple stimulus that must be edited by the user in order to have proper functionality. binary\_count exercises all of the possible input combinations, each for equal fractions of the total simulation time.

- simulation\_type (UltraSim only) sets the type of simulation for UltraSim. The supported options are digital fast (*df*), mixed-signal (*ms*), and Spectre (*s*).

- simulation\_speed (UltraSim only) sets the simulation speed for UltraSim. Increased speed results in decreased accuracy in the simulation. Speed ranges in integer values from 1-8.

- probe\_depth (UltraSim only) determines how many levels of hierarchy deep to save voltage data when running the simulation. The default value is just the top-level.

- probe\_current (UltraSim only) determines whether or not current data is saved. The number of levels of hierarchy that are saved match the *probe\_depth* command. θ does not save the current data, and 1 does.

- hsim\_speed sets the simulation speed for HSIM. Increased speed results in decreased accuracy in the simulation. Speed ranges in integer values from 0-8.

#### 3.8.2 Driver Script (FGC.pl)

This script is the main driver for the toolflow, and is located in the FGC/scripts directory. This script runs the proper sub-routines, which are dispersed among a set of perl modules that are located in the FGC/scripts/modules directory.

At the beginning of the file, there are (only) three variables that need to be changed:

- 1. **\$parameter\_filename** the name of the parameter file. It will be used by the script to find your parameter file and also create the output directories in the proper place.

- 2. **\$fgc\_dir** The full path to the main FGC directory. All of the subroutines use this directory as a reference.

- 3. **\$fgc\_output\_dir** The full path to the output FGC directory. All of the subroutines use this directory as a reference.

Sub-routines in the FGC.pl script FGC.pl runs the following sub-routines (which will be describes in more detail in later portions of this section):

- do\_params converts the parameter file into a data structure for future use in the toolflow

- **do\_arch** generates an architecture file (.xml) using the architectural and circuit-level parameters given in parameter file. This architecture file is one of the inputs to the VTR open-source toolflow that is leveraged by this FGC flow.

- map\_fpga runs the VTR toolflow in order to generate a virtual mapping of the FPGA, which will then be used to generate initial condition commands and configuration bitstreams. Instead of running the full flow end-to-end, we run from up until the final place and route step (VPR), but then run VPR separately, allowing access to additional VPR options.

- do\_ics parses the outputs of the VTR flow to generate IC commands for the coming FPGA schematics. These IC commands ensure proper circuit functionality in the FPGA schematic during simulation.

- **do\_wlbl\_map** generates mapping of configuration bit locations in the generated FPGA, used for generating configuration bitstreams.

- **do\_bitstreams** creates the configuration bitstreams for scan chains used for simulation and silicon verification of the FPGA.

- **do\_schematics** generates the necessary SKILL code for creating the FPGA schematics. The actual schematic generation takes place outside of the script, and must be done by the user in the circuit design environment (i.e. Cadence).

- do\_sims which generates the necessary simulation files for the generated FPGA schematic performing the given benchmark(s). The simulation also calculates delay and energy for each benchmark as well.

## 3.8.3 Modules

The Perl modules described below are the meat of my personal contribution to this FGC toolflow. All of these scripts were written by me, to allow for the generation of IC commands, bitstreams, and schematics to save on the extreme effort required to do all of these things by hand for each differing benchmark and parameter.

Setting Parameters (param\_control.pm) This Perl module takes the parameters from the parameter file the user creates, and puts them into a data structure (hash) that can then be used by the other Perl modules. After creating the hash, the module calculates other important parameters than can be derived from the given parameters, and includes these new parameters in the hash also. The list of parameters that need to be set in the parameters file is the smallest set of parameters than can be used to fully describe the FPGA. The parameters that are calculated are:

- I number of inputs for each CLB.

- **cbox\_w** number of channels each connection box connects to. There are three seperate connection box widths, for inputs, outputs, and I/O connections.

- mux\_depth (mux-based CLBs only) number of levels for the input multiplexers in a multiplexer-based CLB.

- **ble\_wls and ble\_bls** number of word lines (WLs) and bit lines (BLs) that span each BLE in the target FPGA.

- clb\_wls and clb\_bls number of WLs and BLs that span each CLB in the target FPGA.

- **sbox\_wls and sbox\_bls** number of WLs and BLs that span each switch box in the target FPGA.

- **fpga\_tile\_wls and fpga\_tile\_bls** number of WLs and BLs that span each FPGA tile. The description of the FPGA tile is in the Architectural Assumptions section.

- fpga\_wls and fpga\_bls number of WLs and BLs that span the entire FPGA.

The entire list of parameters, both given and calculated, can be observed by the user in the  $FGC_OUT_DIR/parameter_lists$  directory.

Architecture Generation (gen\_arch.pm) This module takes architectural parameters from the parameter hash that has been generated, and creates an architecture file to be used in the VPR flow. The general architecture file format can be found in the VTR documentation. The output architecture file is printed to the  $FGC_OUT_DIR/archs$  directory.

**Running the VTR Flow (virtual\_mapping.pm)** This module runs the VTR flow, which virtually maps the target benchmark circuit(s) to the target FPGA. Both the architectural parameters for the FPGA and the benchmark circuits are described in the parameter file that was the main input to the FGC flow. The VTR tool takes Verilog code and converts it to Berkeley Logic Interchange Format (BLIF), then maps that BLIF onto an FPGA using the Virtual Place and Route (VPR) tool. In the FGC flow, VTR is stopped after the BLIF file is generated. Then, VPR is run on its own, outside of the larger VTR flow. Running VPR stand-alone gives the user access to more options, and gives the FGC tool more control in the FPGA mapping. The outputs from VPR are a set of files that describe a theoretical FPGA that is configured to perform the given function(s). While there are many outputs generated by the VTR flow, the files that are important for the FGC flow are described briefly below:

- Routing graph (rr\_graph.echo) This file enumerates every node in the FPGA. The FGC flow uses this file to determine how the connection boxes in the FPGA connect to the tracks. When the channel fanout (fc) is less than 1, the connection boxes skip over some of the tracks. Moreover, each different connection box connects to different tracks. Thus, it is important to map which tracks are connected to by each connection box in the FPGA.

- Netlist file (<benchmark>.net) This file describes the connectivity of all of the blocks in the FPGA. The FGC tool-flow uses this file to determine intra-CLB connectivity.

- **BLIF file** (**<benchmark>.blif**) This file represents the logic in each LUT of the FPGA. This tool-flow takes the logic, which is represented in the Berkeley Logic Interchange Format

(BLIF), and converts it into a binary representation, to be configured in the LUTs of the FPGA.

- Placement File (<benchmark>.place) This file gives the relative X-Y locations of all of the logic, IP, and IO blocks mapped by the VTR tool. This tool-flow uses this file to keep track of all of the different configuration bits, as they are organized by the location of their FPGA-tile location.

- Routing File (<benchmark>.route) This file describes which pins of different blocks are connected to each other through the global interconnect of the FPGA. The tool-flow uses this file to determine what values to set each configuration bit in the global interconnect.

The VPR outputs are written to the  $FGC_OUT_DIR/vpr_outputs$  directory. The routing graph is the same for each benchmark, and the other VPR outputs are separated into sub-directories based on benchmark.

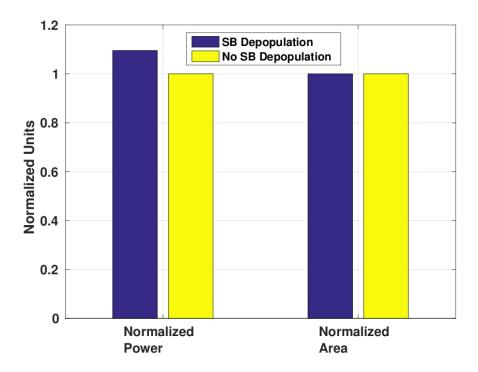

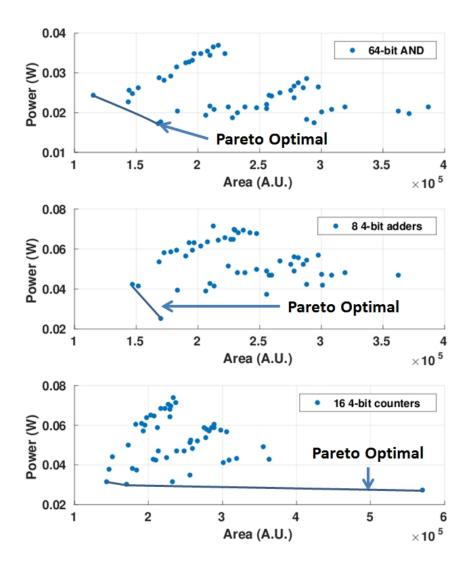

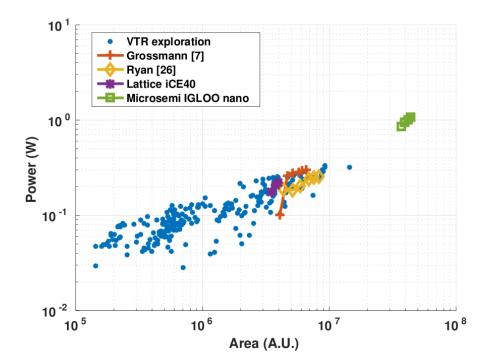

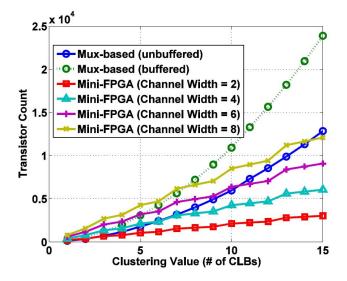

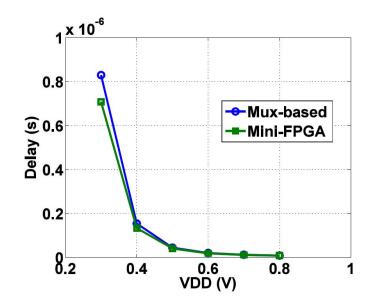

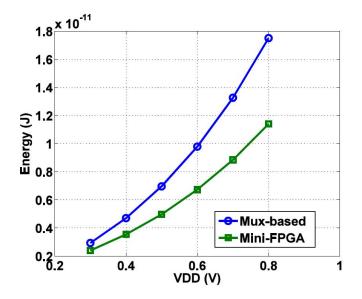

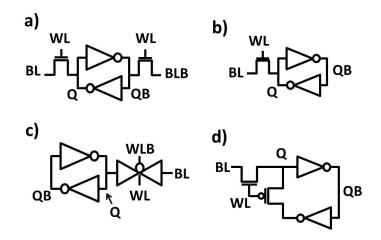

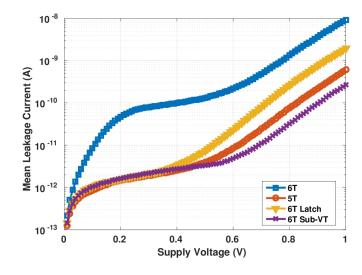

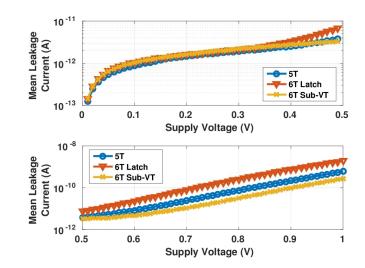

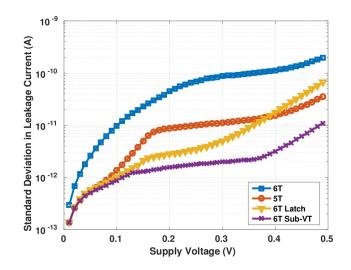

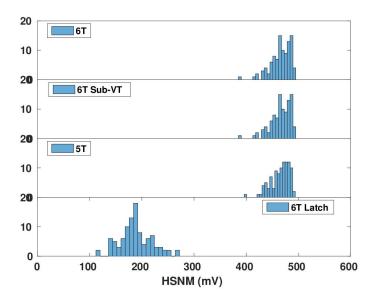

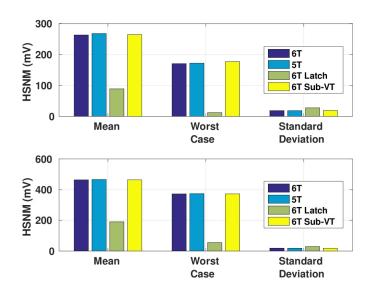

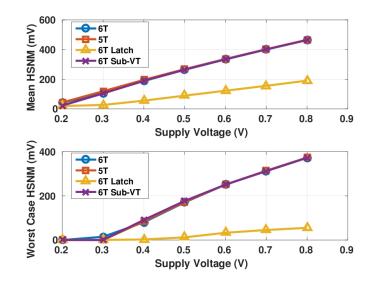

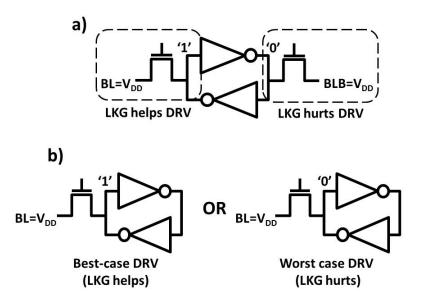

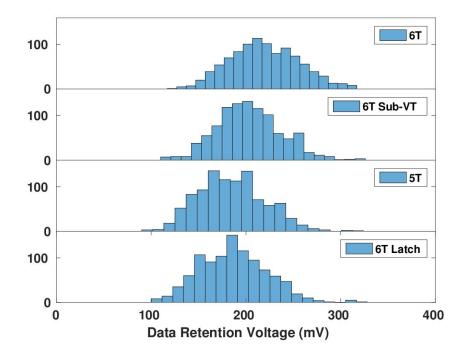

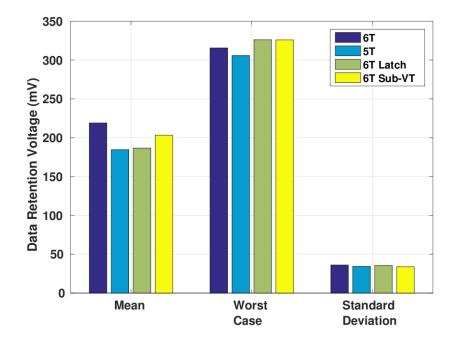

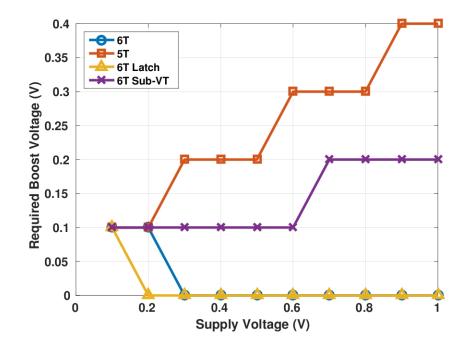

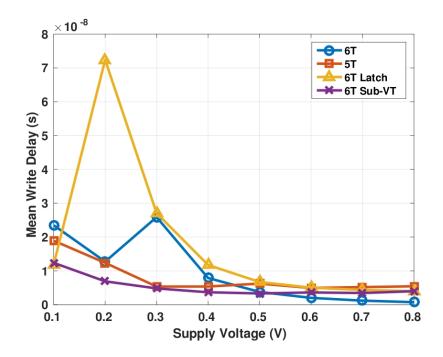

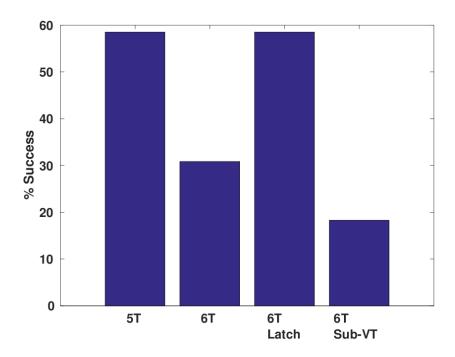

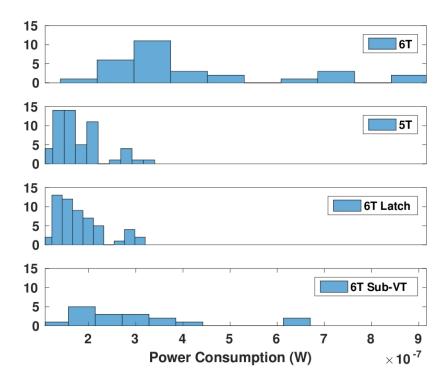

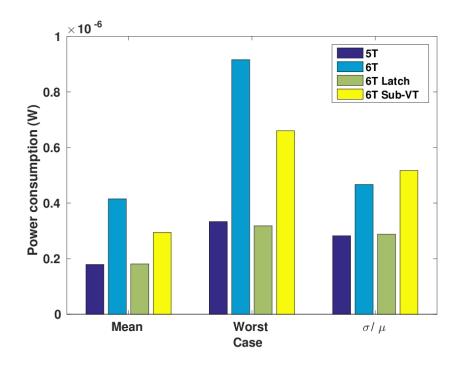

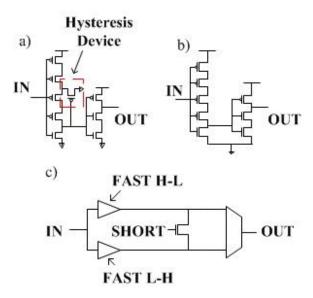

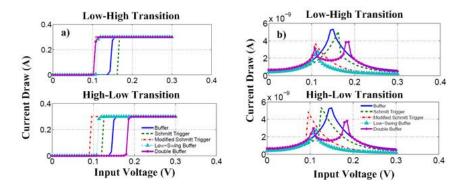

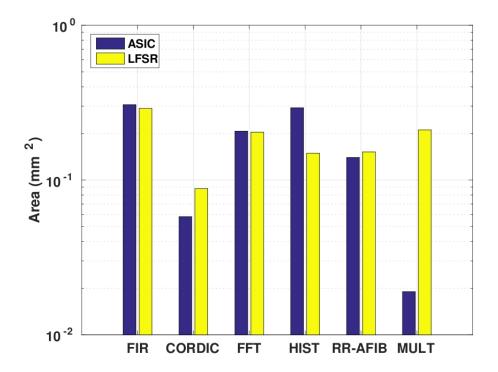

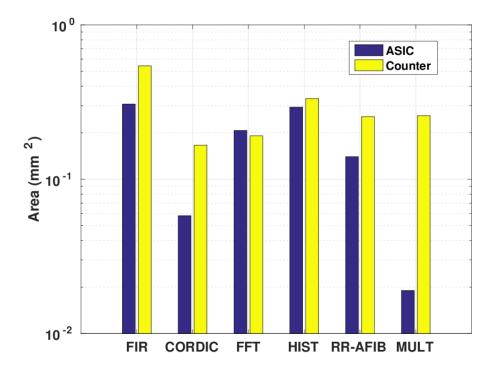

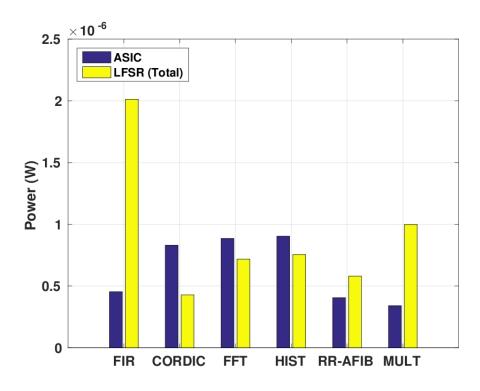

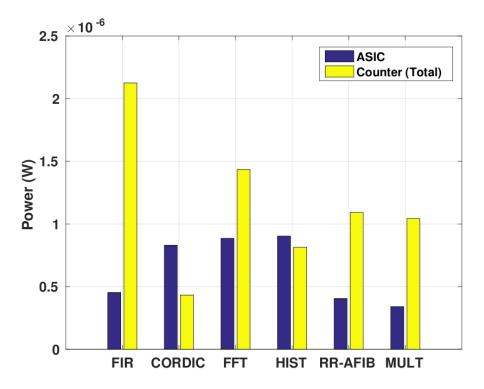

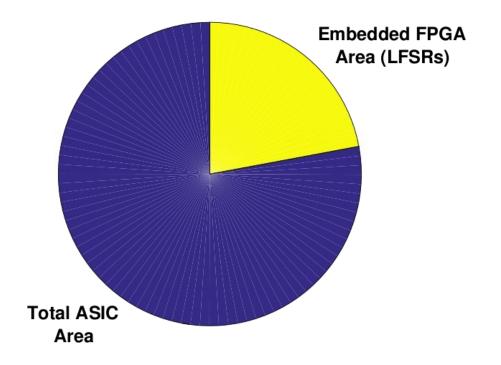

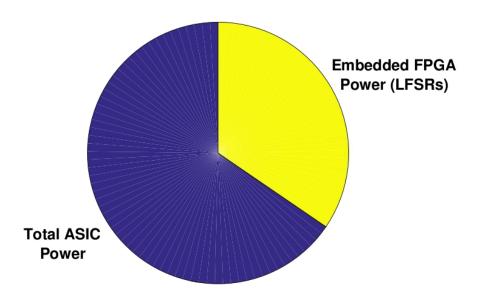

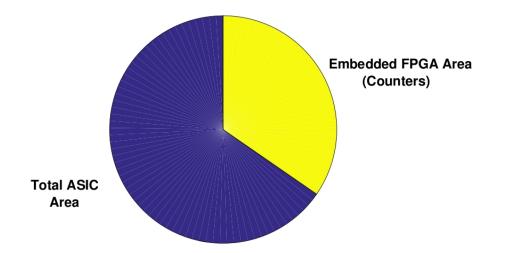

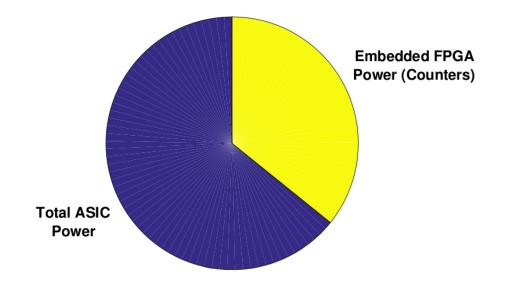

Generating Initial Conditions (gen\_ics.pm) Once the VTR generates the virtual mapping of the FPGA, a set of scripts parse these files and create initial conditions for a simulation of the FPGA. These initial conditions set the values of each configuration bit throughout the entire FPGA fabric. The syntax of each initial condition needs to match the naming conventions of the schematics that will be generated in the future. Additionally, every configuration bit must be set in order to guarantee proper functionality, as bits that are not explicitly set could cause short circuits between used and unused resources. The script first creates all of the possible initial conditions for the FPGA and sets them all to a known default state. For configuration bits controlling access to routing resources or storage elements, such as connection box switches or LUT data, the default value is a logical 0. For configuration bits that the floating nodes down to  $V_{SS}$ , such as those that the down the inputs to LUTs, the default value is a logical 1. Power gates, if included, also use a default value of 1, as we decided to use PMOS headers for our power gates. After the initial conditions statements are initialized, the tool parses the VPR output files and creates IC commands based on the contents of the files. If the created IC command matches one of the commands in the full list, the value of the bit is changed from 'off' to 'on.' The completed list of initial commands shows up in the  $FGC_OUT_DIR/ic_commands/<berlinewiselenchmark>/<simulator>/<clb type>/ic_commands_fpga.scs$ file. <br/>