# Fabrication, Characterization, and Application of Heterogeneously Integrated GaAs Schottky Diodes

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science

University of Virginia

in partial fulfillment of the requirements for the degree

Doctor of Philosophy

by

Souheil Nadri

May 2019

## **APPROVAL SHEET**

This Dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

This Dissertation has been read and approved by the examining committee:

Advisor: Robert M. Weikle II

Committee Member: N. Scott Barker

Committee Member: Richard Bradley

Committee Member: Patrick Hopkins

Committee Member: Arthur Lichtenberger

Committee Member: \_\_\_\_\_

Accepted for the School of Engineering and Applied Science:

OB

Craig H. Benson, School of Engineering and Applied Science

May 2019

# Abstract

Gallium arsenide Schottky diodes remain the predominant device technology for implementing sources, detectors, and heterodyne-based components for instruments operating from 100 GHz to more than 4 THz. Developments in submillimeter-wave diode technology have been aimed at improving fabrication yields, lowering device parasitics which degrade the electrical performance, and improving thermal management. In this process, the geometry and implementation of GaAs diodes have evolved from a stand alone "whisker" contact device to a planar Schottky diode integrated with various passive circuit components. In 2015, Alijabbari developed an initial process for integrating quasi-vertical gallium arsenide Schottky diodes on silicon substrates. Using this process, a 40-160 GHz frequency multiplier source was implemented, exhibiting high frequency translation efficiency (29%) and large output power (70 mW). However, the fabrication process suffered from low to modest yields. The focus of this thesis is to improve the fabrication process and assess the electrical and thermal characteristics of quasi-vertical GaAs diode heterogeneously integrated on Si. The improved process eliminates thermal fabrication steps, including ohmic contact annealing and high-temperature wafer bonding, which lead to wafer fracture and delamination. After that, a new method for extracting diode parasitics based on measurements of passive open and short circuited structures, fabricated on the same wafer as the diodes, is presented. Furthermore, the thermal behavior of the quasi-vertical diodes is investigated for the first time using a thermo-reflectance measurement technique. Finally, the robustness of the new fabrication process is further assessed through the implementation of a WR-5 (140-220 GHz) guasi-optical diode array.

# Acknowledgment

This work would not be possible without the support of: Alex Arsenovic, Matthew Bauwens, Joseph Beatrice, Andreas Beling, Berhanu Bulcha, Nick Buonamico, Amy Clobes, Mike Cyberey, Edward Douglas, Beth Eastwood, Dan Fetko, Brian Foley, John Gaskins, Ben Gonzalez, Rob Hardman, Sami Hawasli, Jeffrey Hesler, Acar Isin, Alex Lobo, Jesse Morgan, Jae Park, Rebecca Percy, Theodore Reck, Adrian Savovici, Gerhard Schoenthal, Jeff Schuch, Yang Shen, Jay Sheth, Mike Stogoski, Bassem Tossoun, Jie Wang, Yadi Weaver, Keith Williams, Mona Zebarjadi, Chunhu Zhang, and Jian Zhang.

I would like to thank the Virginia Cavaliers basketball team for winning the NCAA national championship a few days before my defense. Go Hoos!

I would like to thank my "partner in crime" Linli Xie for countless hours spent processing diodes, as well as my other FIR lab mates: Finbar Curtin, Mike Eller, Scott Hinton, Hussain Humadi, Vinay Iyer, Masoud Jafari, Chris Moore, Austin Raymer, Noah Sauber, and Dustin Widmann.

A special thanks to the Microwave Theory and Techniques Society (MTT-S) for awarding me the 2017 MTT-S Graduate Fellowship, which assisted me in completing the work presented in Chapter 4. I would also like to thank Virginia Diodes Inc. for their support and help with test equipement.

I would like to express my gratitude to my advisor Bobby Weikle for his support; I have learned so much under his guidance. I would also like to thank the members of my committee: Scott Barker, Richard Bradley, Patrick Hopkins, and Arthur Lichtenberger for their assistance and mentorship.

Finally, I want to thank my friends and family for their incredible support. Specifically, I would like to thank my father Ahmed Nadri, my mother Amina El Bouaaichi, my brother Chihab Nadri, and Tati Khadija for allowing me to study so far away from home (Morocco) and supporting me financially and emotionally. Last but not least, I would like to thank my beautiful and lovely wife Amanda for all her support, care, love, and dedication – even at times of hardship.

# Contents

| 1        | $\mathbf{Intr}$ | oduction                                                   | <b>21</b> |

|----------|-----------------|------------------------------------------------------------|-----------|

|          | 1.1             | Terahertz Applications                                     | 21        |

|          | 1.2             | Device Technologies for Accessing the THz Spectrum         | 23        |

|          | 1.3             | THz Schottky Diodes: Operation, Geometry, and Challenges . | 25        |

|          |                 | 1.3.1 Operation                                            | 25        |

|          |                 | 1.3.2 Schottky Diode History                               | 27        |

|          |                 | 1.3.3 Improving Process Robustness: The Rise of the Planar |           |

|          |                 | Diode                                                      | 28        |

|          | 1.4             | Heterogeneous Integration of THz Diodes and Quasi-Vertical |           |

|          |                 | Geometry                                                   | 32        |

|          |                 | 1.4.1 Heterogeneous Integration on Quartz                  | 32        |

|          |                 | 1.4.2 Quasi-Vertical Diodes                                | 33        |

|          |                 | 1.4.3 Heterogeneously Integrated Quasi-Vertical Diodes     | 34        |

|          | 1.5             | Thesis Outline                                             | 35        |

| <b>2</b> | Pro             | cess Development for Heterogeneously-Integrated Quasi-     |           |

|          | Ver             | tical Schottky Diodes                                      | 37        |

|          | 2.1             | Prior Implementation                                       | 38        |

|          | 2.2             | Ohmic Contact                                              | 42        |

|          |                 | 2.2.1 Background                                           | 42        |

|          |                 | 2.2.2 Annealed Contact                                     | 43        |

|          |                 | 2.2.3 Adding InGaAs Cap Layers                             | 45        |

|          | 2.3             | Epitaxy Transfer and Bonding                               | 49        |

|          | 2.4             | New Process Flow                                           | 53        |

|          | 2.5             | DC Characterization                                        | 57        |

|          | 2.6             | Application: Integrated Quadrupler                         | 58        |

|   |               | 2.6.1 Overview of Circuit Architecture and Design                                         | 59 |

|---|---------------|-------------------------------------------------------------------------------------------|----|

|   |               | 2.6.2 Fabrication Process                                                                 | 59 |

| 3 | $\mathbf{RF}$ | Characterization of Quasi-Vertical Diodes                                                 | 66 |

|   | 3.1           | Scattering-Parameter Measurement                                                          | 67 |

|   | 3.2           | Extraction of Diode Parasitic Elements                                                    | 70 |

|   |               | 3.2.1 Diode Geometry                                                                      | 71 |

|   |               | 3.2.2 Calibration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 72 |

|   |               | 3.2.3 Diode Test Structures                                                               | 73 |

|   |               | 3.2.4 Measurement and Analysis                                                            | 74 |

|   |               | 3.2.5 Summary                                                                             | 78 |

|   | 3.3           | Characterization of Integrated Quad                                                       | 79 |

| 4 | The           | rmal Characterization of Terahertz Quasi-Vertical Diodes                                  |    |

|   | Het           | erogeneously Integrated on Silicon 8                                                      | 83 |

|   | 4.1           | Quasi-Vertical Geometry                                                                   | 84 |

|   | 4.2           | Prior Work                                                                                | 86 |

|   | 4.3           | Thermal Device Model                                                                      | 88 |

|   |               | 4.3.1 Thermal Equivalent Circuit Model                                                    | 88 |

|   |               | 4.3.2 Finite Element Model                                                                | 91 |

|   | 4.4           | Thermo-Reflectance Technique                                                              | 93 |

|   | 4.5           | Electrical Transient Method                                                               | 99 |

|   | 4.6           | Discussion                                                                                | 03 |

|   | 4.7           | Application: Full Quadrupler Simulation                                                   | 05 |

|   |               | 4.7.1 Material Parameter Extraction using Time-Domain Thermo-                             | -  |

|   |               | $Reflectance  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $            | 05 |

|   |               | 4.7.2 Simulation Results                                                                  | 07 |

| 5 | WF            | -5 (140-220 GHz) Quasi-Optical QVD Diode Array 10                                         | )9 |

|   | 5.1           | Prior Work                                                                                | 10 |

|   | 5.2           | Design                                                                                    | 13 |

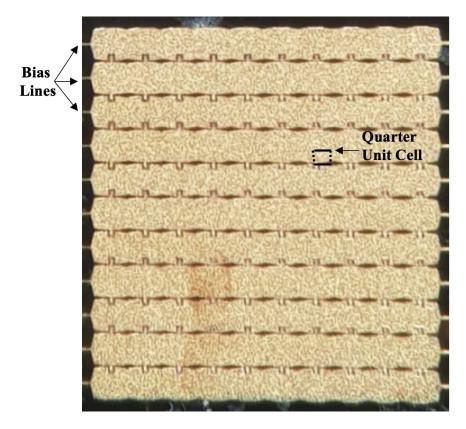

|   |               | 5.2.1 Unit Cell Layout                                                                    | 13 |

|   |               | 5.2.2 Equivalent Circuit Model                                                            | 14 |

|   |               | 5.2.3 HFSS Simulation Setup                                                               | 18 |

|   |               | 5.2.4 Simulation Results                                                                  | 20 |

|              | 5.3  | Array Processing                                                   | 121     |

|--------------|------|--------------------------------------------------------------------|---------|

|              |      | 5.3.1 QVD Diode Fabrication with Backside SOI Process $\therefore$ | 122     |

|              |      | 5.3.2 QVD Diode Fabrication with Backside Silicon Bosch            |         |

|              |      | Process                                                            | 127     |

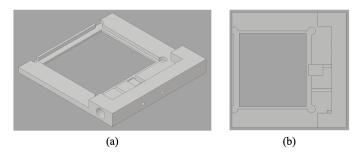

|              | 5.4  | Fixture Design for Membrane Diode Arrays                           | 132     |

|              |      | 5.4.1 Sapphire Holder                                              | 132     |

|              |      | 5.4.2 Quartz Holder                                                | 134     |

|              | 5.5  | Robustness Assessment                                              | 136     |

|              | 5.6  | Array DC Characterization                                          | 139     |

|              | 5.7  | RF Characterization                                                | 141     |

|              |      | 5.7.1 Quasi-Optical Setup                                          | 141     |

|              |      | 5.7.2 3D Printed Holder                                            | 141     |

|              |      | 5.7.3 Calibration                                                  | 143     |

|              |      | 5.7.4 Setup Verification                                           | 144     |

|              |      | 5.7.5 Diode Array Characterization                                 | 145     |

|              | 5.8  | Conclusion                                                         | 146     |

| 6            | Con  | clusion & Future Work                                              | 149     |

| U            | 6.1  | Future Work                                                        | 150     |

|              | 0.1  |                                                                    | 100     |

| $\mathbf{A}$ | On-  | Wafer Diode Fabrication                                            | 169     |

| Б            | Ъ    |                                                                    | -1 17 4 |

| В            | Bac  | kside Process for Quadrupler/Array                                 | 174     |

| $\mathbf{C}$ | EM   | F Calculation                                                      | 176     |

|              |      |                                                                    |         |

| D            | From | ntside Diode Array Fabrication                                     | 180     |

| $\mathbf{E}$ | Bac  | kside Lithography for Bosch Process                                | 186     |

|              | Dat  | kside hitilography for Dosch i rocess                              | 100     |

| $\mathbf{F}$ | Arr  | ay Holder Fabrication                                              | 187     |

| $\mathbf{G}$ | VO   | Array                                                              | 191     |

|              | _    | Introduction                                                       | 191     |

|              | G.2  | VO <sub>2</sub>                                                    | 193     |

|              |      | G.2.1 Background                                                   | 193     |

|              |      | G.2.2 Fabrication                                                  | 193     |

| G.3 | Architecture                                                                              | 194 |

|-----|-------------------------------------------------------------------------------------------|-----|

| G.4 | Measurements                                                                              | 195 |

|     | G.4.1 Aparatus                                                                            | 195 |

|     | G.4.2 Calibration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 196 |

| G.5 | Beam Size                                                                                 | 199 |

| G.6 | Results                                                                                   | 199 |

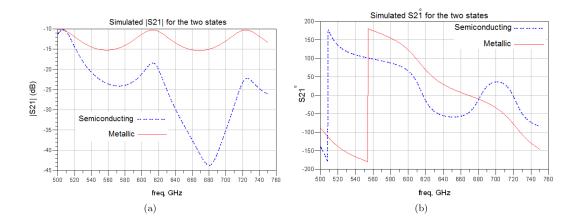

| G.7 | S21 Simulation                                                                            | 201 |

| G.8 | Optically Induced Switching                                                               | 202 |

| G.9 | Conclusion                                                                                | 203 |

# List of Figures

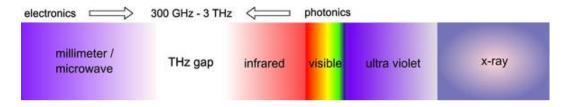

| 1.1 | Frequency spectrum.                                                          | 21 |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | VDI frequency extension modules shown for size comparison to                 |    |

|     | a typical VNA.                                                               | 25 |

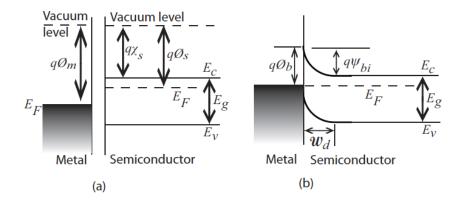

| 1.3 | Energy-band diagram of a metal-semiconductor system: (a)                     |    |

|     | prior contact; (b) ideal contact. $E_F$ is the Fermi energy, $E_g$           |    |

|     | is the semiconductor bandgap energy, $E_C$ is the bottom edge of             |    |

|     | the conductance band, $\mathbf{E}_V$ is the top edge of the valence band,    |    |

|     | $\phi_s$ is the semiconductor work function, and $\psi_{bi}$ is the built-in |    |

|     | potential (from $[17]$ )                                                     | 26 |

| 1.4 | A galena cat's-whisker detector, an early radio wave detector                |    |

|     | used in crystal radio receivers from about $1905$ to the $1940s$             |    |

|     | (from $[19]$ )                                                               | 28 |

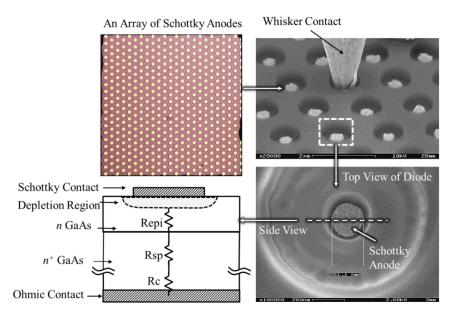

| 1.5 | Whisker contacted Schottky diode (from [24])                                 | 28 |

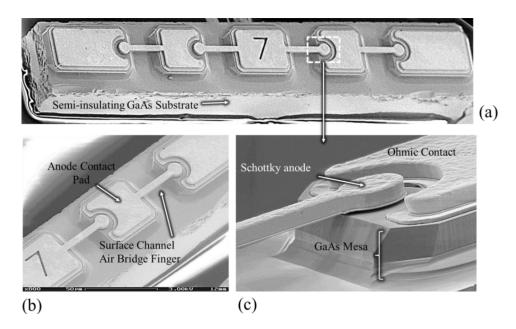

| 1.6 | (a) Planar diode chip with 4 anodes (b) Close-up on the surface              |    |

|     | channel air bridge finger aimed at reducing the device parasitics            |    |

|     | (c) Close-up on the Schottky and ohmic contact                               | 29 |

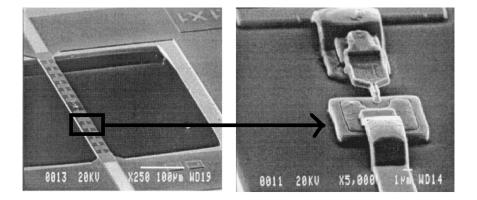

| 1.7 | SEM micrographs of completed membrane and frame with 2.5-                    |    |

|     | THz Schottky diode and RF low-pass filter structure. Frame                   |    |

|     | dimensions are 1 mm x 1.4 mm 50 $\mu m$ thick. Membrane is 36                |    |

|     | $\mu m \ge 600 \ \mu m \ 3 \ \mu m$ thick (from [21])                        | 30 |

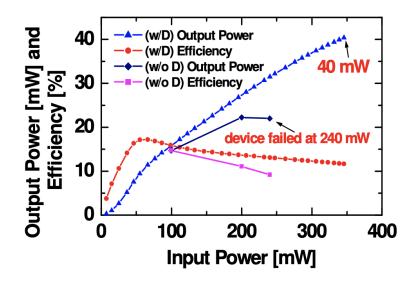

| 1.8 | Output power and efficiency versus input power measured at                   |    |

|     | $240~\mathrm{GHz}$ for triplers operated at room temperature both with       |    |

|     | and without diamond heat-spreaders (from $[25]$ )                            | 31 |

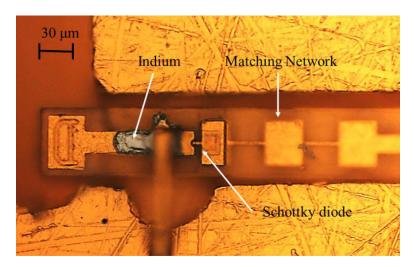

| 1.9  | 1.6 THz integrated varactor side band generator circuit fabri-                                     |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | cated by Virginia Diodes, Inc. and assembled by Alijabbari                                         |    |

|      | (from [24]).                                                                                       | 33 |

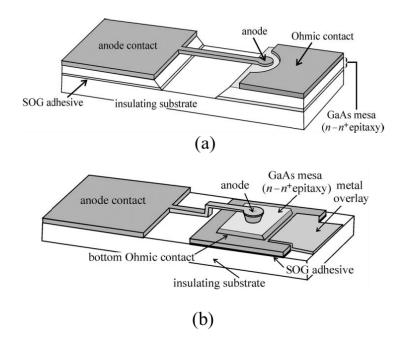

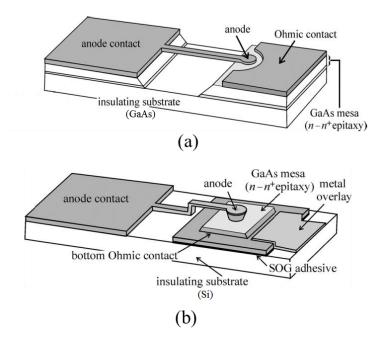

| 1.10 | Diagrams showing the geometry of (a) a laterally-oriented pla-                                     |    |

|      | nar diode and (b) a quasi-vertical diode integrated into a planar                                  |    |

|      | circuit. $\ldots$ | 34 |

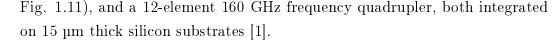

| 1.11 | Image of frequency doubler mounted in a waveguide housing                                          |    |

|      | based on integrating quasi-vertical diodes on 15 $\mu m$ silicon                                   | 35 |

| 1.12 | Summary of the various THz diode technologies reported in the                                      |    |

|      | literature (from $[33]$ )                                                                          | 36 |

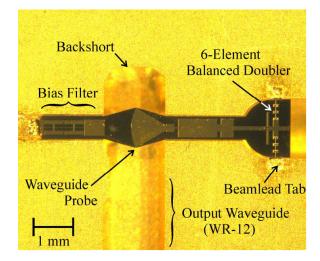

| 2.1  | Outline of the quasi-vertical diode fabrication process: (a) GaAs                                  |    |

|      | epitaxy; (b) wafer bonding to silicon substrate; (c) mesa etch;                                    |    |

|      | and (d) final anode and cathode contact formation. Note the                                        |    |

|      | epitaxial layers shown in the figure are not to scale. (From [24])                                 | 38 |

| 2.2  | Microscope image showing a Ge/Pd/Au/Ti ohmic contact, an-                                          |    |

|      | nealed correctly. The surface is smooth (less than 100 nm),                                        |    |

|      | making it compatible with the subsequent bonding steps. $\ldots$                                   | 39 |

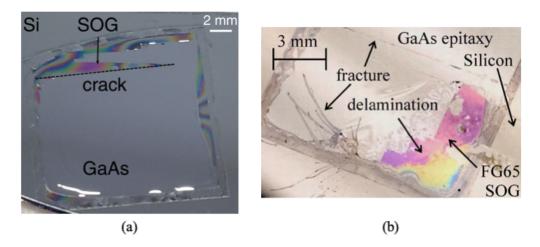

| 2.3  | Microscope images showing the GaAs active device epitaxy af-                                       |    |

|      | ter bonding and thinning. The surface suffers from cracks and                                      |    |

|      | delamination of the GaAs epitaxy.                                                                  | 41 |

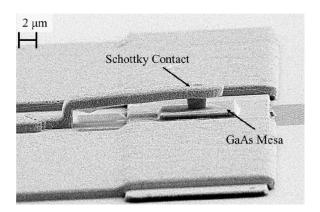

| 2.4  | SEM image of a completed GaAs QVD Schottky diode het-                                              |    |

|      | erogeneously integrated on Si using the process developed by                                       |    |

|      | Alijabbari                                                                                         | 41 |

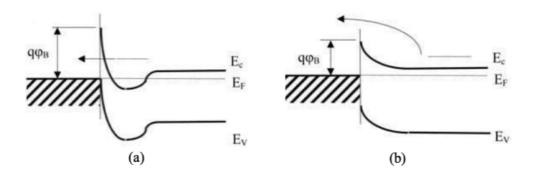

| 2.5  | Band diagram of a metal/n-GaAs ohmic interface using: (a)                                          |    |

|      | tunneling achieved through a high level of doping $(b)$ thermionic                                 |    |

|      | field emission through barrier height lowering (From $[36]$ )                                      | 43 |

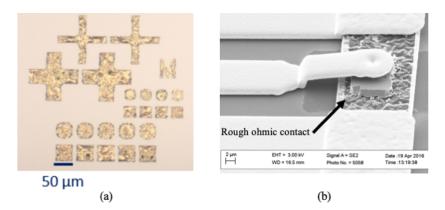

| 2.6  | Rough surface ( $> 100$ nm) of ohmic pads features fabricated                                      |    |

|      | using a Ni-based alloy shown in: (a) a microscope image of                                         |    |

|      | alignment markers, and (b) SEM image of a completed diode                                          |    |

|      | using the Ni-metallization.                                                                        | 44 |

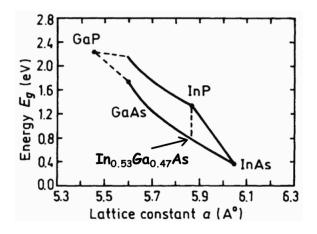

| 2.7  | Energy gap versus lattice constant for InGaAs. The band gap                                        |    |

|      | decreases with In content. Note that $In_{0.53}Ga_{0.47}As$ is lattice                             |    |

|      | matched to InP (From $[43]$ )                                                                      | 45 |

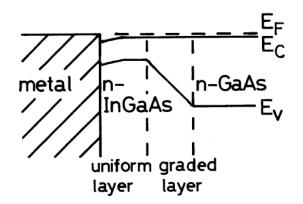

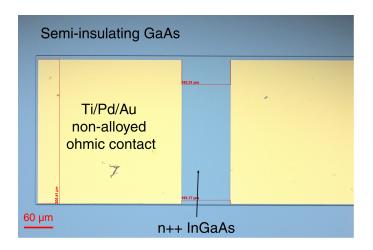

| 2.8  | Band diagram for metal-InGaAs ohmic contact interface (From [37]).                      | 46 |

|------|-----------------------------------------------------------------------------------------|----|

| 2.9  | Diagram illustrating the TLM method: (a) top view of the wafer, (b) side-view.          | 47 |

| 9.10 |                                                                                         | 41 |

| 2.10 | Microscope image showing two rectangular pads on a mesa used<br>in the TLM measurement. | 48 |

| 2.11 | TLM plot showing the resistance for different adjacent pad sep-                         |    |

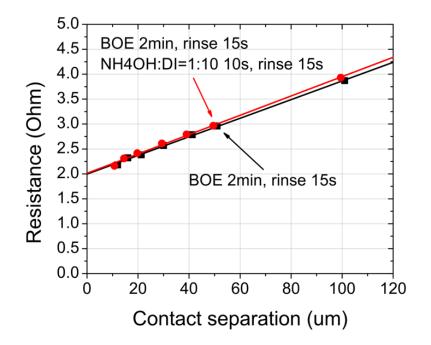

|      | arations. Two surface preparations are investigated.                                    | 49 |

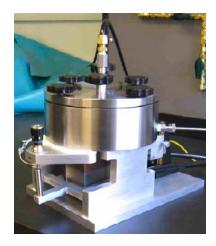

|      | Bonding press used in this work $[24]$ .                                                | 51 |

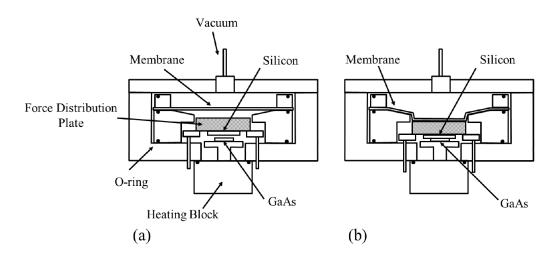

| 2.13 | (a) cross section view of the membrane press before bonding                             |    |

|      | GaAs to SOI, (b) view of the press during bonding                                       | 51 |

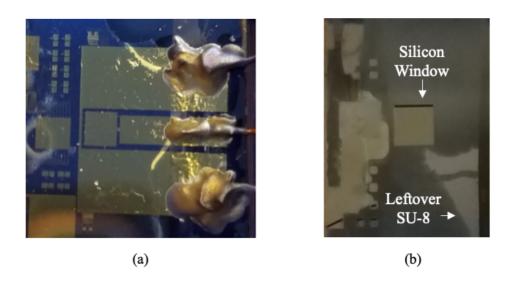

| 2.14 | Lack of adhesion of SU-8 to highly doped InGaAs resulting in                            |    |

|      | peeling of the device layers                                                            | 52 |

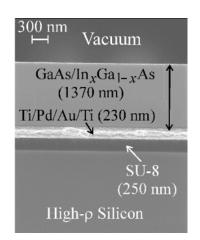

| 2.15 | Side view cross-sectional SEM view of the gallium epitaxial de-                         |    |

|      | vice layers on silicon, after bonding and handle layer removal.                         |    |

|      | The bonding interface is uniform and lacks voids                                        | 53 |

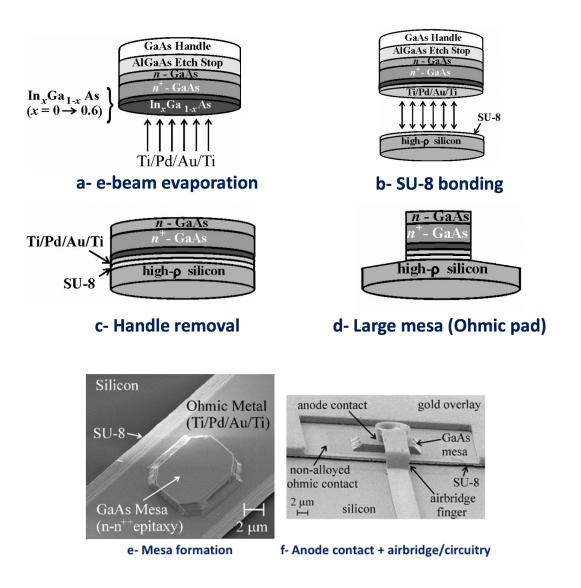

| 2.16 | New fabrication process flow (a) e-beam evaporation of the                              |    |

|      | ohmic metal stack, (b) bonding of the diode epitaxy on silicon                          |    |

|      | using SU-8, (c) GaAs handle layer removal, (d) diode ohmic                              |    |

|      | mesa area definition, (e) final device mesa definition, (f) SEM                         |    |

|      | of the quasi-vertical diode profile (diameter = $3 \mu m$ ) showing                     |    |

|      | the device mesa, underlying ohmic contact, and anode contact                            |    |

|      | airbridge.                                                                              | 54 |

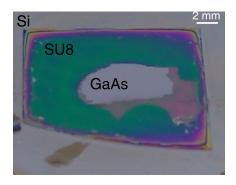

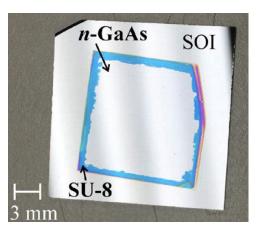

| 2.17 | GaAs epitaxy bonded to SOI (thinned to $\sim 1 \ \mu m$ )                               | 55 |

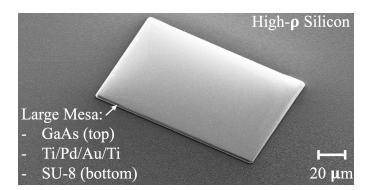

| 2.18 | SEM image of a large mesa. The exposed layers are the GaAs                              |    |

|      | device layers. The Ti/Pd/Au/Ti ohmic contact, which is bonded                           |    |

|      | to silicon using SU-8, lies underneath the GaAs layers                                  | 56 |

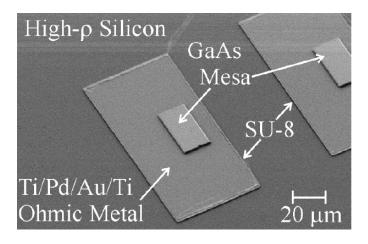

| 2.19 | SEM image of two GaAs mesas on ohmic metal bonded to high-p                             |    |

|      | silicon carrier.                                                                        | 56 |

| 2.20 |                                                                                         | 57 |

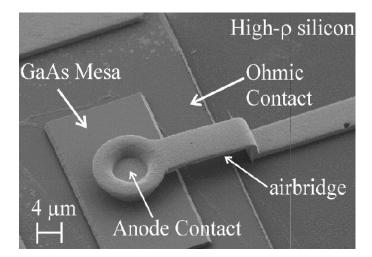

| 2.21 | Measured current-voltage characteristic of a quasi-vertical diode                       |    |

|      | with 3 µm diameter anode (dots), current-voltage characteristic                         |    |

|      | of the contact pads without diode (dotted) and fitted current-                          |    |

|      | voltage curve from the diode equation (solid).                                          | 58 |

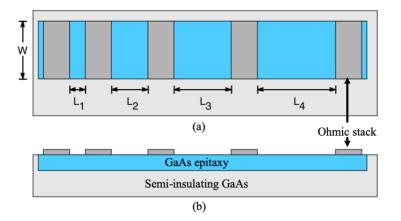

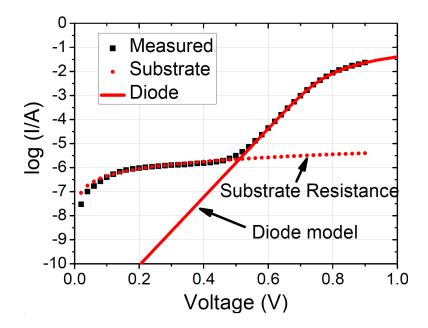

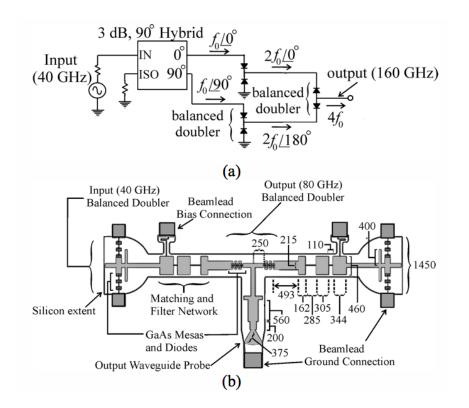

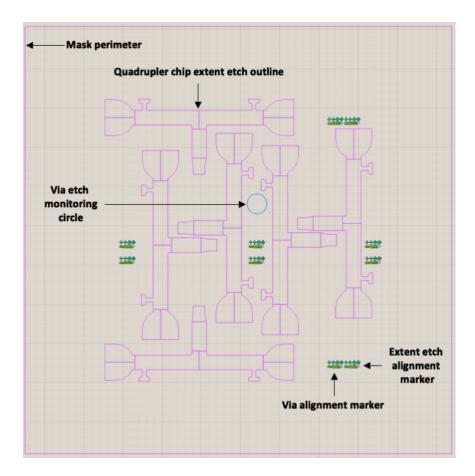

| 2.22 | (a) Quadrupler circuit architecture and (b) layout of the inte-   |    |

|------|-------------------------------------------------------------------|----|

|      | grated quadrupler chip. The quadrature hybrid is implemented      |    |

|      | off-chip (in waveguide) and all dimensions noted are in $\mu m.$  | 60 |

| 2.23 | Simplified CAD drawing for the via and extent mask steps.         | 62 |

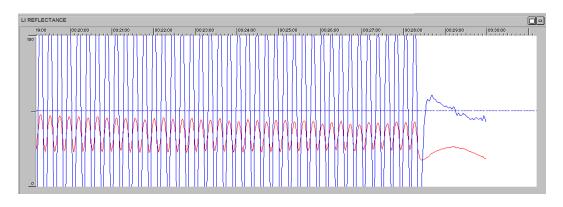

| 2.24 | Screenshot showing the end point detection curves for the silicon |    |

|      | etch step in the Oxford tool.                                     | 63 |

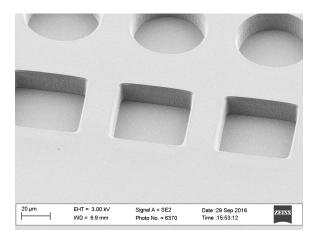

| 2.25 | Scanning electron micrograph of the extent etch alignment mark-   |    |

|      | ers, defined during the via etch step                             | 63 |

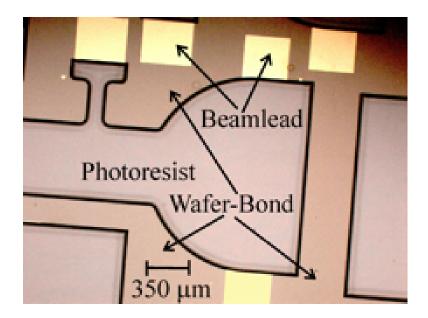

| 2.26 | Backside lithography used to define the chip geometry             | 65 |

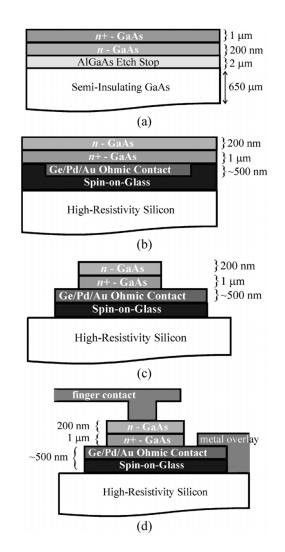

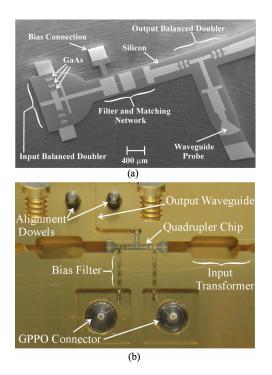

| 2.27 | (a) SEM image of the completed quadrupler chip. (b) The           |    |

|      | quadrupler chip mounted to its waveguide housing. The quadra-     |    |

|      | ture hybrid is not shown                                          | 65 |

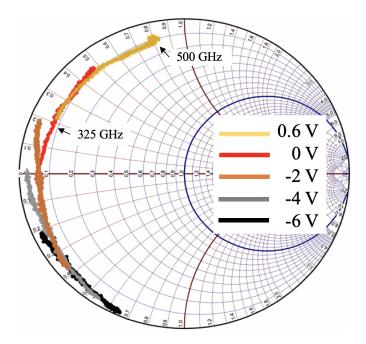

| 3.1  | WR-2.2 on wafer measurement results: S11 vs voltage from $325$    |    |

|      | GHz to 500 GHz                                                    | 67 |

| 3.2  | WR-2.2 on wafer measurement results: S11 vs voltage at $425$      |    |

|      | GHz                                                               | 68 |

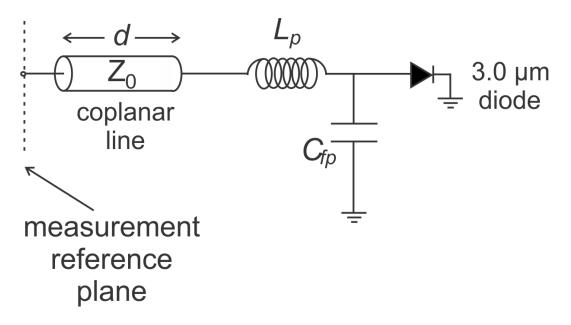

| 3.3  | Equivalent circuit model used to de-embed the diode junction      |    |

|      | capacitance and series resistance from the measured S-parameter   |    |

|      | data                                                              | 69 |

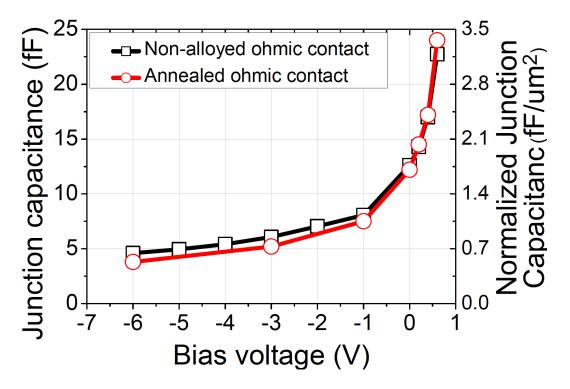

| 3.4  | WR-2.2 on wafer measurement results: Extracted junction ca-       |    |

|      | pacitance.                                                        | 69 |

| 3.5  | WR-2.2 on wafer measurement results: Extracted series resis-      |    |

|      | tance                                                             | 70 |

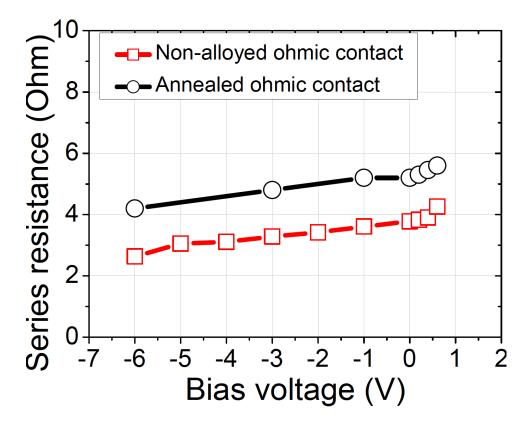

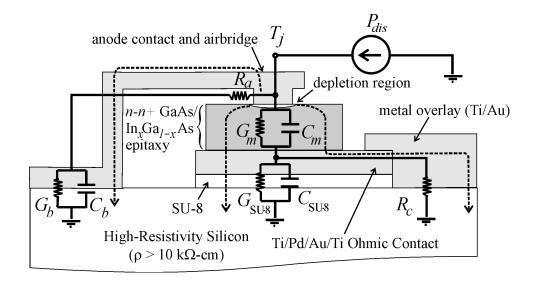

| 3.6  | (a) Scanning electron micrograph of a quasi-vertical Schottky     |    |

|      | diode with coplanar feed for S-parameter measurement. (b)         |    |

|      | Diagram showing the diode geometry superimposed on the con-       |    |

|      | ventional circuit model used to represent the device parasitics.  | 72 |

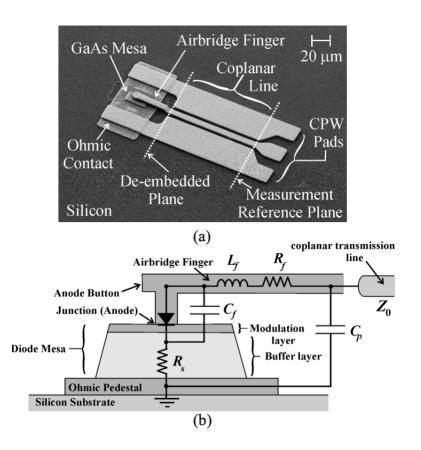

| 3.7  | Measured S-parameters of the on-wafer calibration standards       |    |

|      | from 325 to 500 GHz. (a) reflection coefficient of the reflect    |    |

|      | standards (open and short) (b) transmission coefficient of the    |    |

|      | through and line.                                                 | 73 |

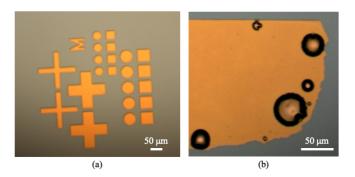

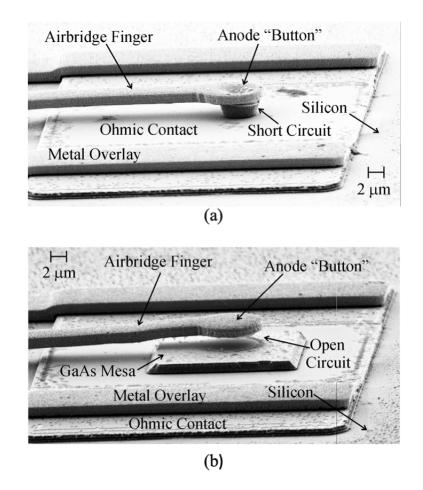

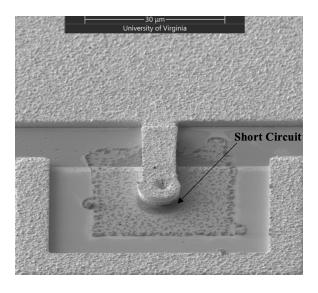

| 3.8  | Scanning electron micrograph images of passive structures used      |    |

|------|---------------------------------------------------------------------|----|

|      | to characterize the diode's parasitic environment. (a) Short-       |    |

|      | circuited termination with finger directly contacting the ohmic     |    |

|      | pedestal, and (b) open-circuited diode structure with anode         |    |

|      | "button" suspended over the mesa and ohmic contact. $\ldots$ .      | 74 |

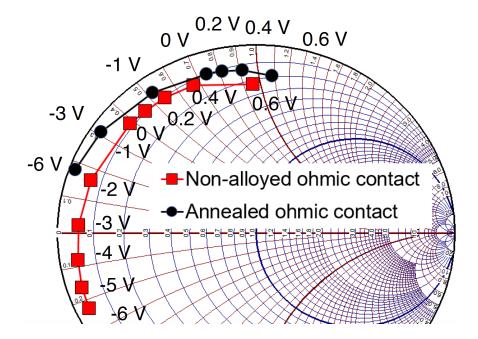

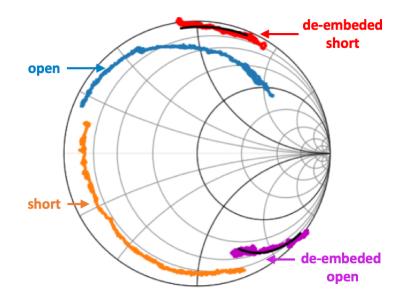

| 3.9  | Measured reflection coefficients of the short-circuited and open-   |    |

|      | circuited diode structures. Data is presented at both the mea-      |    |

|      | surement reference plane and the de-embedded plane shown in         |    |

|      | Fig. 3.5(a). The response of the circuit models are shown for       |    |

|      | comparison (as solid lines)                                         | 75 |

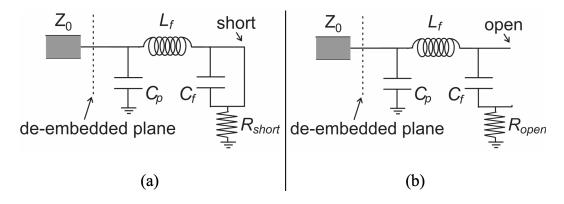

| 3.10 | Equivalent circuit representations of (a) the short-circuited and   |    |

|      | (b) open-circuited diode structures shown in Fig. 3.6               | 76 |

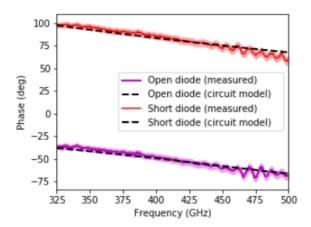

| 3.11 | Phase of the de-embedded S-parameters for the short-circuited       |    |

|      | (top) and open (bottom) diode structures, with minimum and          |    |

|      | maximum confidence bounds that quantify the uncertainty as-         |    |

|      | sociated with skating of the wafer probe. The response of the       |    |

|      | circuit models are shown as dashed lines, for comparison            | 78 |

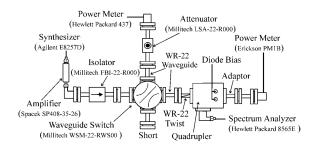

| 3.12 | Diagram of the quadrupler measurement setup [1]. $\ldots$ .         | 79 |

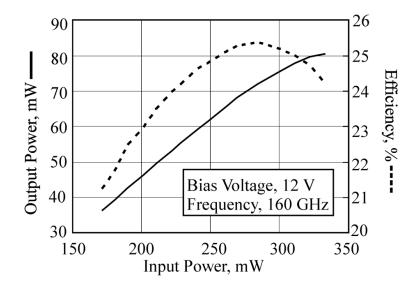

| 3.13 | Quadrupler output power and efficiency vs. input power              | 80 |

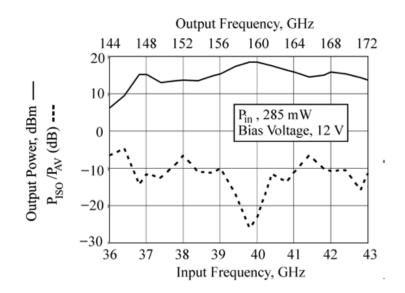

| 3.14 | Output power and power measured at the isolation port, nor-         |    |

|      | malized to available power. vs. frequency.                          | 81 |

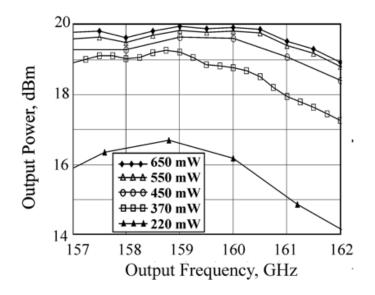

| 3.15 | Power output vs frequency for different input power levels          | 81 |

| 4.1  | Diagrams showing the geometry of (a) a laterally-oriented pla-      |    |

|      | nar diode and (b) a quasi-vertical diode integrated into a planar   |    |

|      | circuit.                                                            | 85 |

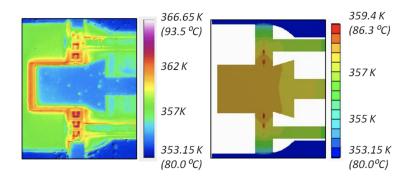

| 4.2  | Measured and simulated temperature distribution of the multi-       |    |

|      | plier chip from $[67]$                                              | 86 |

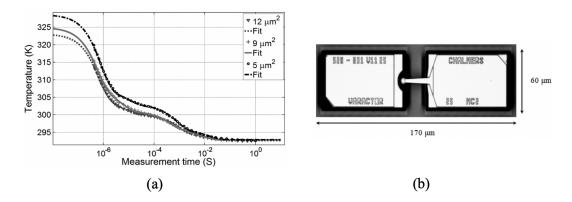

| 4.3  | (a) Thermal response plots of different anode size planar diodes    |    |

|      | obtained using the electrical transient method, (b) Microscope      |    |

|      | photograph of a 9 $\mu$ m <sup>2</sup> diode under test (from [71]) | 87 |

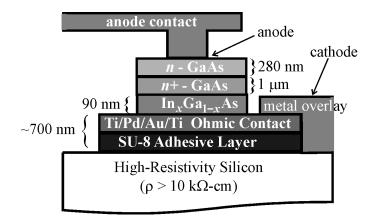

| 4.4  | Diagram of the diode cross-section and epitaxy. The semi-                              |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | insulating handle and AlGaAs etch stop layers are removed in                           |     |

|      | the fabrication process and are not shown. Note the device                             |     |

|      | layers are not shown to scale.                                                         | 88  |

| 4.5  | Diagram of the quasi-vertical diode geometry showing the paths                         |     |

|      | (dashed lines) for heat flow from the anode to the thermal                             |     |

|      | ground (silicon substrate) and simplified thermal equivalent cir-                      |     |

|      | cuit model.                                                                            | 89  |

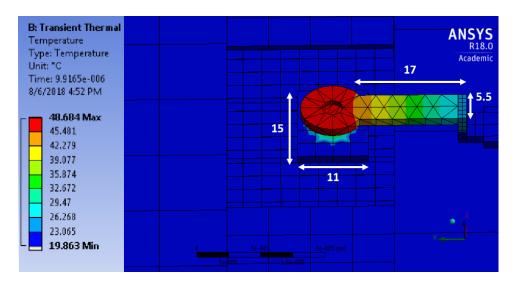

| 4.6  | 3-D finite element model of the quasi-vertical Schottky diode.                         |     |

|      | Dimensions given in the figure have units of $\mu m.$                                  | 91  |

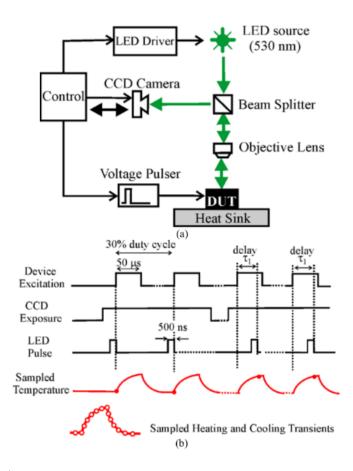

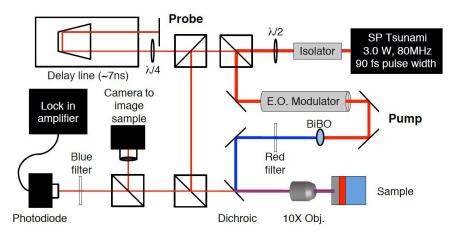

| 4.7  | (a) Experimental setup for thermo-reflectance characterization                         |     |

|      | of the diode. (b) Time diagram for acquisition of the diode                            |     |

|      | heating and cooling transients                                                         | 94  |

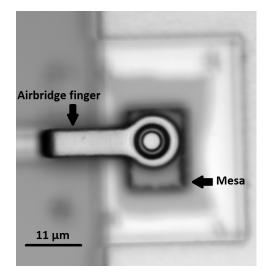

| 4.8  | Optical image of the 5.5 $\mu m$ diameter diode from above. $~$                        | 95  |

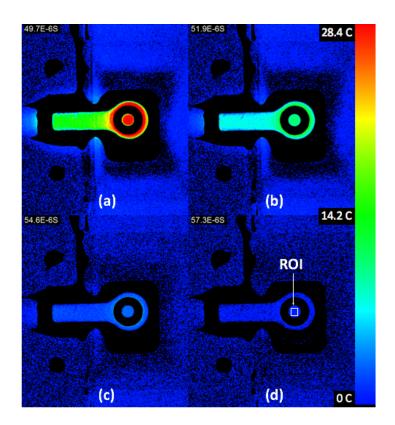

| 4.9  | Thermal maps of diode D1 obtained at times (a) 49.7, (b) 51.9,                         |     |

|      | (c) 54.6 and (d) 57.3 $\mu s$ after removal of the heating excitation                  |     |

|      | using thermo- reflectance measurements. Note the temperature                           |     |

|      | scale is indicated on the right. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 96  |

| 4.10 | (a) Measured and fitted heating and cooling transients of a 5.5                        |     |

|      | $\mu m$ diameter diode. The fitted curves utilize a single time con-                   |     |

|      | stant of 2 $\mu s.$ (b) Measured cooling transient of this diode com-                  |     |

|      | pared to the modeled transient using ANSYS Mechanical finite                           |     |

|      | element solver (dashed curve)                                                          | 97  |

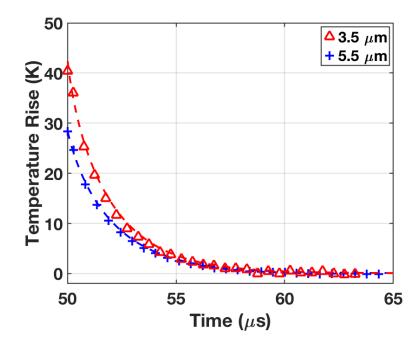

| 4.11 | Measured cooling transients of a 5.5 $\mu m$ diameter diode and 3.5                    |     |

|      | $\ensuremath{\mu\mathrm{m}}$ diameter diode. The ANSYS curves are shown as dashed      |     |

|      | lines                                                                                  | 99  |

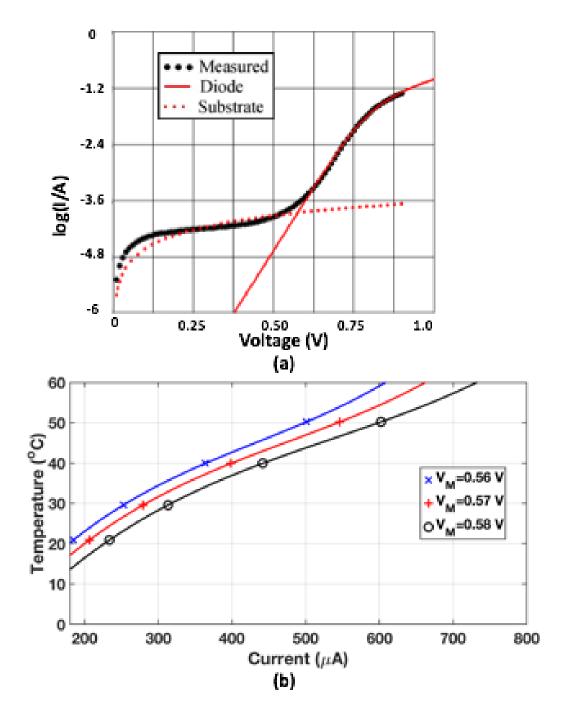

| 4.12 | (a) Measured and fitted current-voltage relation for a 5.5 $\mu m$                     |     |

|      | diameter quasi-vertical diode. (b) Measured diode temperature-                         |     |

|      | current calibration curves for three different sensing voltages,                       |     |

|      | $V_M$                                                                                  | 101 |

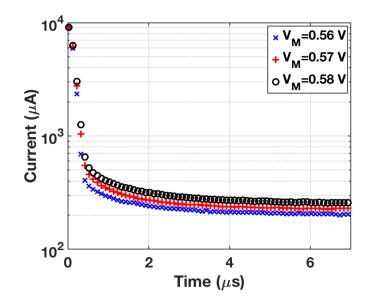

| 4.13 | Measured transient current curves for a 5.5 $\mu$ m diameter diode.                    |     |

|      | The device was first held at $0.75$ V for 50 µs. Then at $t = 0$ s in                  |     |

|      | this figure, the voltage was switched to three bias points: 0.56                       |     |

|      | V, 0.57 V, 0.58 V                                                                      | 102 |

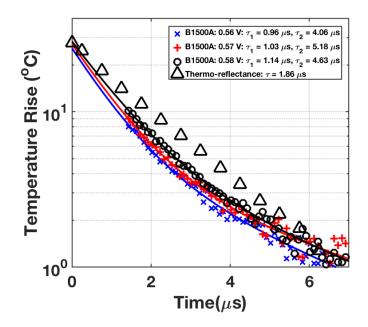

| 4.14 | Measured and fitted thermal cooling transients for a 5.5 µm di-                |     |

|------|--------------------------------------------------------------------------------|-----|

|      | ameter quasi-vertical diode using electrical transient measure-                |     |

|      | ments. Results obtained from thermo-reflectance measurements                   |     |

|      | (triangles) of the same diode are shown for comparison. Devi-                  |     |

|      | ation of electrical transient data from a straight line indicates              |     |

|      | the necessity of two time constants.                                           | 102 |

| 4.15 | TDTR measurement setup.                                                        | 106 |

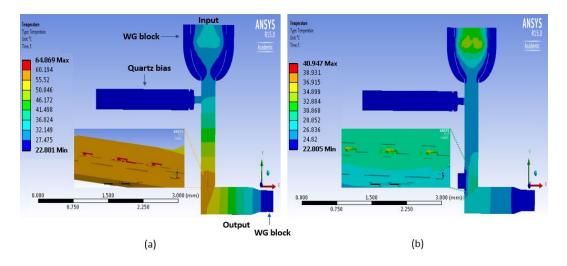

| 4.16 | Steady-state temperature distribution of: (a) Original quadru-                 |     |

|      | pler design, (b) Modified design with an extra beam lead                       | 108 |

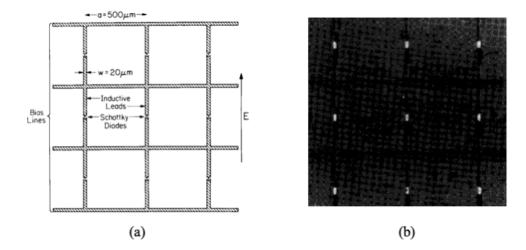

| 5.1  | (a) Diagram and (b) micrograph of a section of a 94 GHz                        |     |

|      | monolithic GaAs diode grid with 1600 Schottky-barrier varactor $% \mathcal{A}$ |     |

|      | diodes developed by W.W. Lam (1988) [94]                                       | 111 |

| 5.2  | 36-Element varistor mode SBG array on quartz developed by                      |     |

|      | D. Kurtz [89]                                                                  | 112 |

| 5.3  | 100-Element planar varactor diode SBG array on GaAs devel-                     |     |

|      | oped by Hawasli [23]                                                           | 112 |

| 5.4  | Geometry of the array unit cell                                                | 113 |

| 5.5  | Photograph of the full 100-element varactor diode array based                  |     |

|      | on QVD                                                                         | 114 |

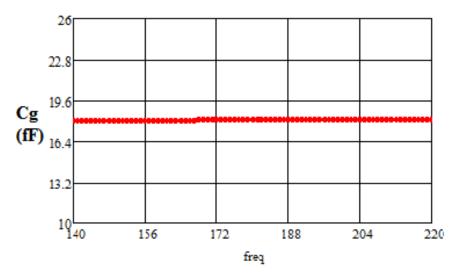

| 5.6  | Gap capacitance versus frequency (140 GHz - 220 GHz) com-                      |     |

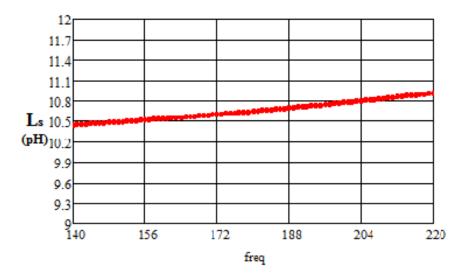

|      | puted using Equation $(5.1)$                                                   | 115 |

| 5.7  | Metal strip inductance versus frequency (140 GHz - 220 GHz)                    |     |

|      | computed using Equation (5.2). $\ldots$ $\ldots$ $\ldots$ $\ldots$             | 116 |

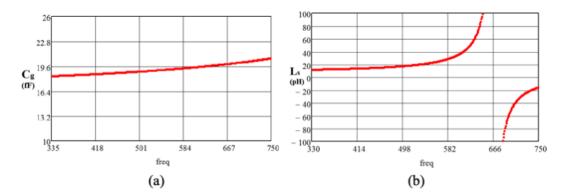

| 5.8  | (a) Slot gap capacitance computed using Equation $(5.1)$ and $(b)$             |     |

|      | Metal strip inductance computed using Equations $(5.2)$ versus                 |     |

|      | frequency (335 GHz - 750 GHz)                                                  | 117 |

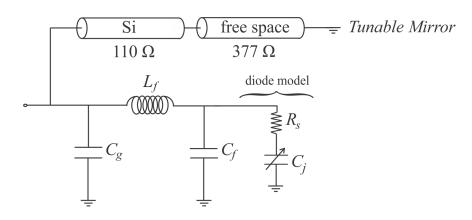

| 5.9  | Equivalent circuit model for a unit cell                                       | 118 |

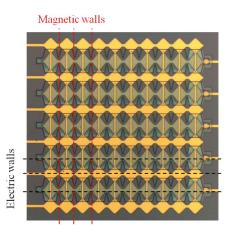

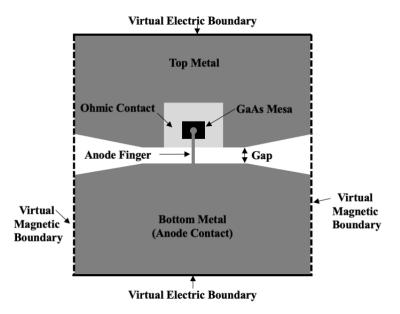

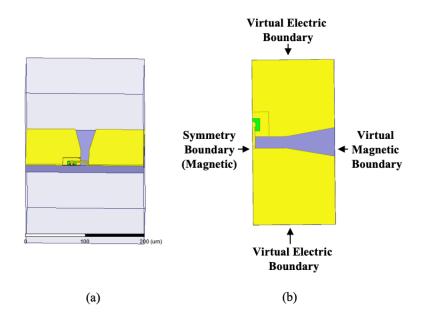

| 5.10 | HFSS simulation setup (a) unit cell geometry (b) boundary con-                 |     |

|      | ditions                                                                        | 118 |

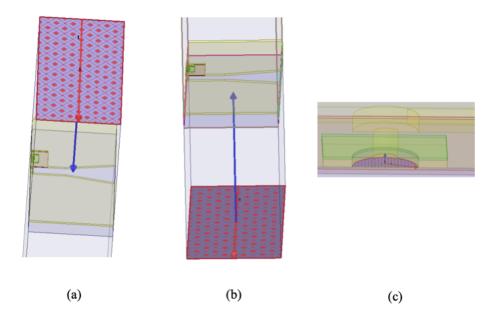

| 5.11 | HFSS port excitation setup for (a) port 1 (free-space), (b) port               |     |

|      | 2 (free-space), and (c) port 3 (diode port). $\ldots$ $\ldots$                 | 119 |

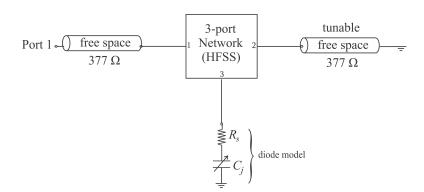

| 5.12 | ADS simulation setup showing the 3-port S-parameter network                   |     |

|------|-------------------------------------------------------------------------------|-----|

|      | obtained using HFSS. Free-space transmission lines are con-                   |     |

|      | nected to port 1 and port 2 of the HFSS network. Port 3 is                    |     |

|      | connected to the diode model.                                                 | 120 |

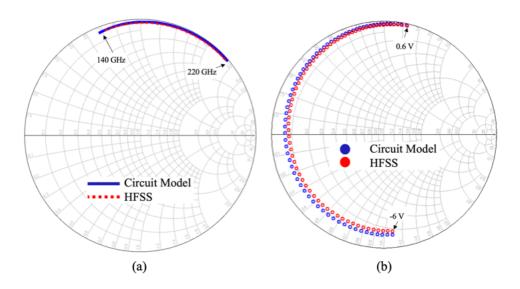

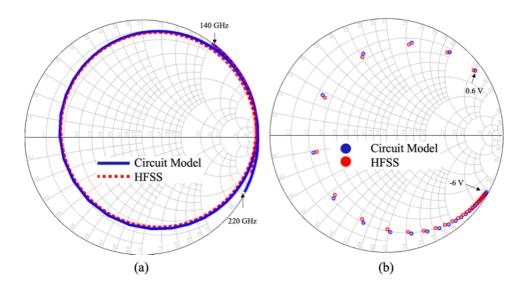

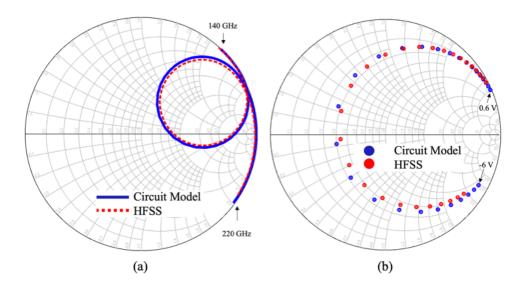

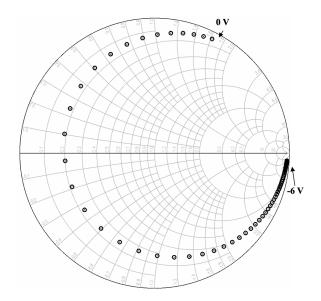

| 5.13 | HFSS simulation reflection coefficient results (plotted on Smith              |     |

|      | charts) for 4 $\mu$ m diameter QVD diode unit cell array: (a) zero-           |     |

|      | bias data versus frequency from 140-220 GHz, (b) data at 158                  |     |

|      | GHz vs bias from -6 V to 0.6 V.                                               | 121 |

| 5.14 | HFSS simulation reflection coefficient results (plotted on Smith              |     |

|      | charts) for 2.4 µm diameter QVD diode unit cell array: (a) zero-              |     |

|      | bias data versus frequency from 140-220 GHz, (b) data at 158                  |     |

|      | GHz vs bias from -6 V to 0.6 V.                                               | 122 |

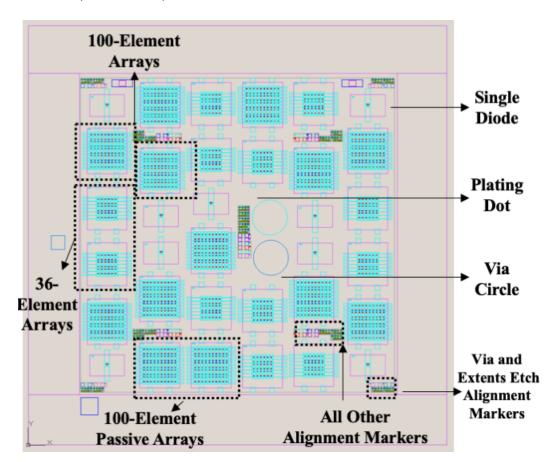

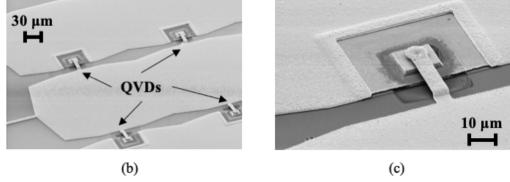

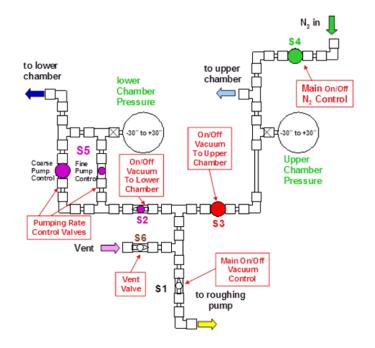

| 5.15 | CAD drawing for the mask used to fabricate QVD membrane                       |     |

|      | arrays.                                                                       | 123 |

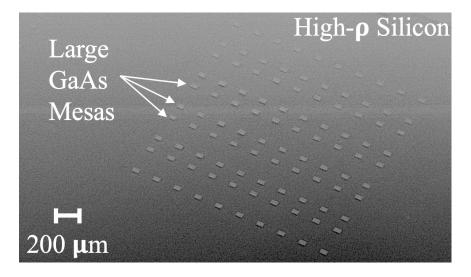

| 5.16 | $\operatorname{SEM}$ image of a 100-element array's large mesas . The exposed |     |

|      | layers are the GaAs device layers. The $\rm Ti/Pd/Au/Ti$ ohmic                |     |

|      | contact, which is bonded to silicon using SU-8, lies underneath               |     |

|      | the GaAs layers.                                                              | 125 |

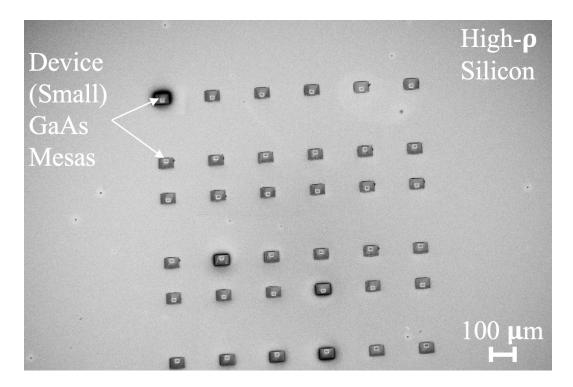

| 5.17 | SEM image of GaAs device mesas on ohmic metal bonded to                       |     |

|      | high- $\rho$ silicon carrier                                                  | 126 |

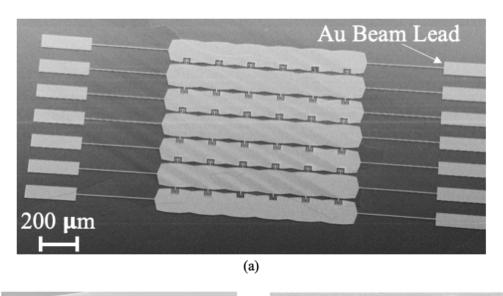

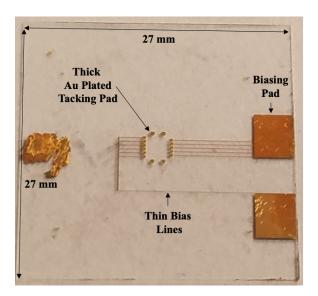

| 5.18 | ${ m SEM}$ image of completed 36-element diode array (a) entire array         |     |

|      | showing the beam leads connected to each row, (b) zoom-view                   |     |

|      | into 4 diode elements, (c) close look at a single element from                |     |

|      | the diode array.                                                              | 127 |

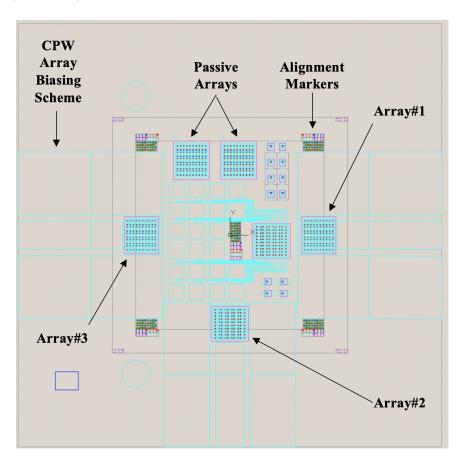

| 5.19 | CAD drawing for the mask used to fabricate QVD Bosch arrays.                  | 128 |

| 5.20 | SEM image of a completed Bosch array (frontside). The anode                   |     |

|      | terminal rows of the array are connected to the center conductor              |     |

|      | of a CPW line. The cathode terminal rows of the array are                     |     |

|      | connected to the outer grounds. All 100 diodes are connected                  |     |

|      | in parallel.                                                                  | 130 |

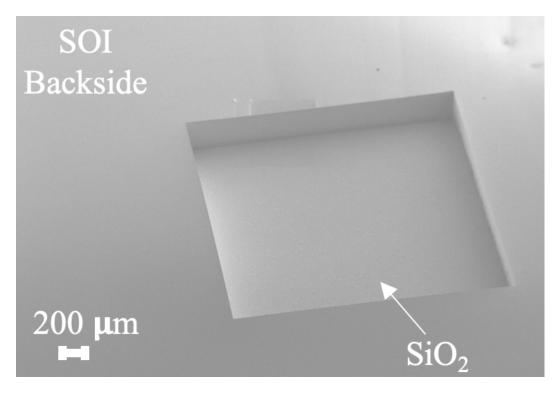

| 5.21 | SEM image of the backside of the SOI wafer after deep silicon                 |     |

|      | etching of a window.                                                          | 131 |

| 5.22 | Photograph of a completed Bosch array (a) top view, (b) bottom                |     |

|      | view                                                                          | 132 |

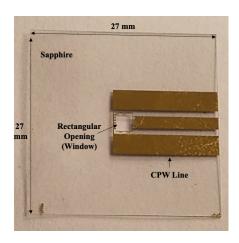

| 5.23 | Photograph image of the sapphire holder                                                               | 133 |

|------|-------------------------------------------------------------------------------------------------------|-----|

| 5.24 | Photograph image of a 100-element diode array mounted on the                                          |     |

|      | sapphire holder                                                                                       | 133 |

| 5.25 | Photograph image of the quartz holder                                                                 | 134 |

| 5.26 | Photograph image of a 36-element diode array mounted on the                                           |     |

|      | quartz holder                                                                                         | 135 |

| 5.27 | HFSS simulation reflection coefficient results (plotted on Smith                                      |     |

|      | charts) for 4.0 $\mu m$ diameter QVD diode unit cell array which                                      |     |

|      | incorporates the quartz substrate: (a) zero-bias data versus fre-                                     |     |

|      | quency from 140-220 GHz, (b) data at 158 GHz vs bias from -6 $$                                       |     |

|      | V to 0.6 V. $\ldots$ | 136 |

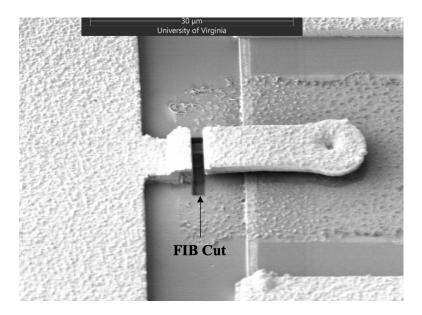

| 5.28 | SEM image of a short-circuited diode array element                                                    | 137 |

| 5.29 | SEM image of a gallium FIB cut on a shorted QVD. $\ldots$ .                                           | 138 |

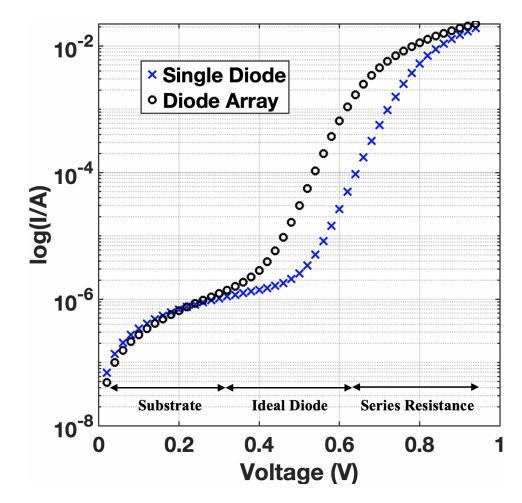

| 5.30 | Measured current-voltage characteristic of: a 36-element quasi-                                       |     |

|      | vertical diode array with 2.4 $\mu m$ diameter anode (black circle)                                   |     |

|      | and a single 2.4 $\mu m$ diameter anode diode (blue X)                                                | 140 |

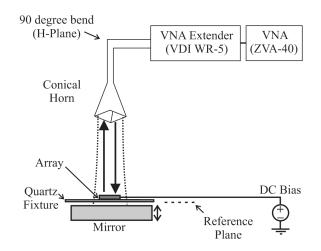

| 5.31 | Diagram of the experimental setup used to characterize the                                            |     |

|      | quasi-vertical diode array. A Chanzon high power LED chip                                             |     |

|      | and a Quarton laser module (VLM-650-01 LPA) are used to                                               |     |

|      | align the setup                                                                                       | 141 |

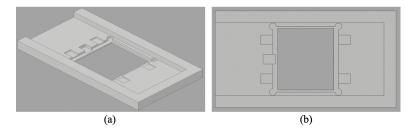

| 5.32 | CAD drawing of the 3D printed array holder designed to be                                             |     |

|      | mounted on a lens holder: (a) tilted view, (b) top view                                               | 142 |

| 5.33 | CAD drawing of the alternative 3D printed array holder design:                                        |     |

|      | (a) tilted view, (b) top view. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                    | 142 |

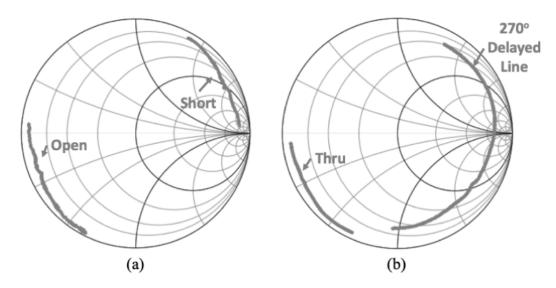

| 5.34 | Measurement of the corrected system calibration standards from                                        |     |

|      | 140-220 GHz shown on a Smith chart.                                                                   | 143 |

| 5.35 | Measurement of the reflection coefficient of a high resistivity                                       |     |

|      | silicon substrate: (a) magnitude with no air gap, (b) phase with                                      |     |

|      | no air gap, (c) magnitude with 72° air gap, (d) phase with 72°                                        |     |

|      | air gap                                                                                               | 144 |

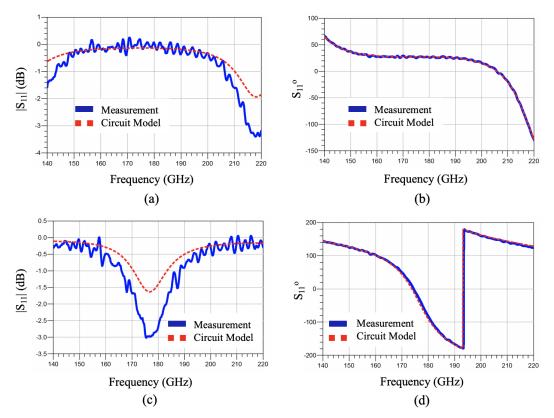

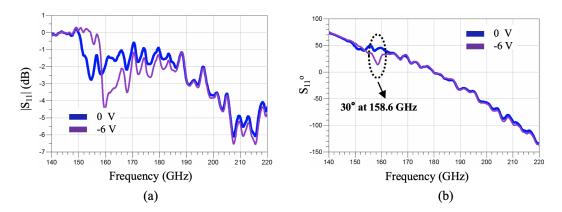

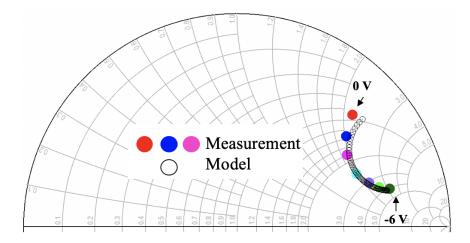

| 5.36 | Measurement of the reflection coefficient of the diode array for                                      |     |

|      | a mirror position of 93° (430 $\mu m)$ at 0 V (blue curve) and -6 V                                   |     |

|      | (purple curve): (a) magnitude, (b) phase                                                              | 145 |

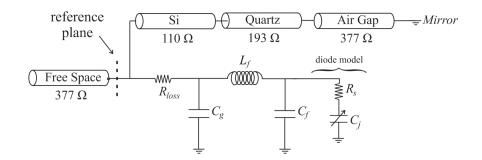

| 5.37 | Equivalent circuit representation used to model the diode array                                                                 | 1.40 |

|------|---------------------------------------------------------------------------------------------------------------------------------|------|

| 5.38 | measurementMeasurement and modeled reflection coefficient response of the                                                       | 146  |

|      | diode array for a mirror position of 90° (416 $\mu$ m) at 0 V: (a)                                                              |      |

|      | magnitude, (b) phase                                                                                                            | 147  |

|      | Response of the diode array as a function of bias voltage<br>Projected performance of a diode array which eliminates all losses | 147  |

|      | except for the diode series resistance                                                                                          | 148  |

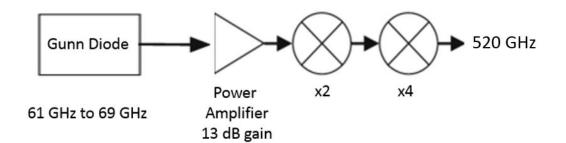

| 6.1  | Schematic diagram of the proposed 520 GHz multiplier chain.                                                                     | 151  |

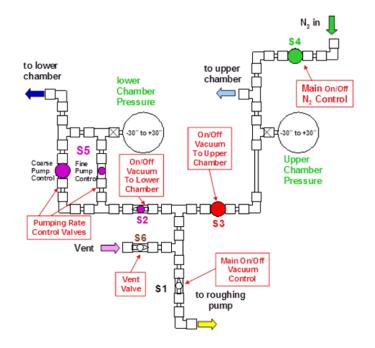

| A.1  | Diagram of Valve Control System.                                                                                                | 171  |

| D.1  | Diagram of Valve Control System.                                                                                                | 182  |

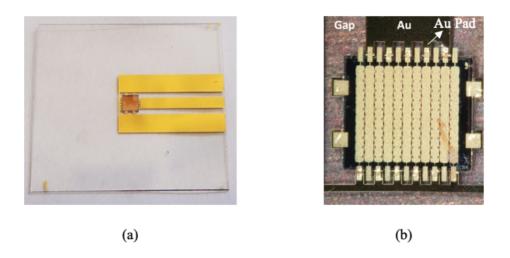

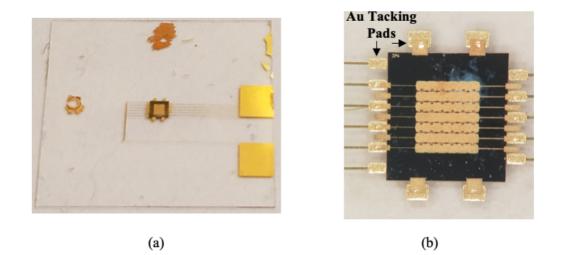

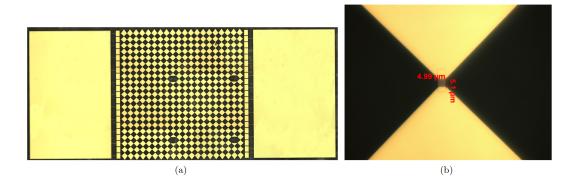

| F.1  | CAD image of the array holder mask. The bias lines are 50 $\mu\mathrm{m}$ wide. The                                             |      |

|      | gold tacking pads are plated twice, during GOLD1 with the rest of the                                                           |      |

|      | features, and again during GOLD2                                                                                                | 190  |

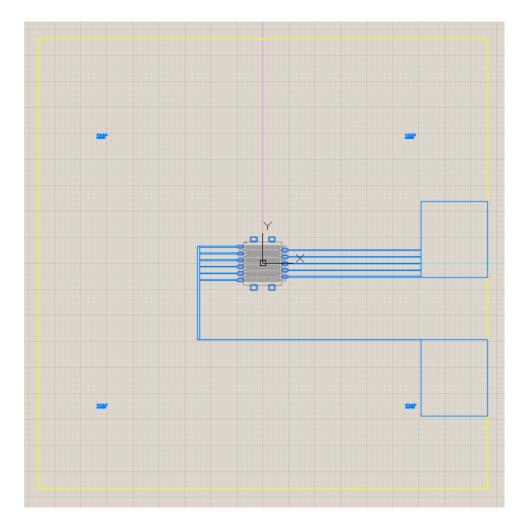

| G.1  | (a) Microscope image of the bowtie antenna array. The rows are connected                                                        |      |

|      | in parallel. The gure also shows the two gold contact pads on both sides.                                                       |      |

|      | Some elements are missing due to defects in the mask. The structure is                                                          |      |

|      | built on a sapphire substrate.(b) Higher magnication image of a single                                                          |      |

|      | bow<br>tie. The vanadium dioxide lm is located at the antenna feed. $\ . \ . \ .$                                               | 194  |

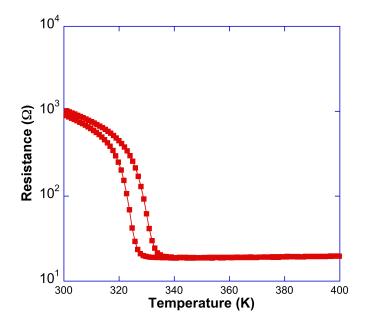

| G.2  | Resistance vs temperature measurement of the sample. The measurement                                                            |      |

|      | is done in a chamber that allows very accurate control of the temperature.                                                      |      |

|      | The resistance changes by about two orders of magnitude and the behavior                                                        |      |

|      | is hysteretic                                                                                                                   | 195  |

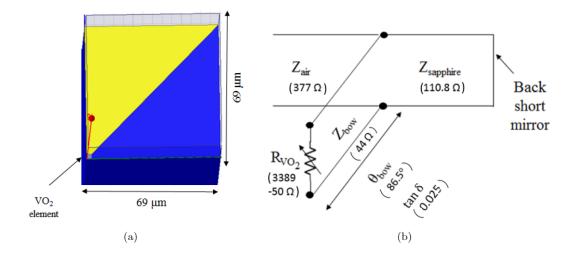

| G.3  | (a) Layout of the array unit cell represented as an equivalent waveguide.                                                       |      |

|      | The top and bottom walls are perfect E-walls. The right and left walls are                                                      |      |

|      | perfect H-walls. The sapphire (in blue) has a thickness of 400 $\mu m.$ The                                                     |      |

|      | vanadium dioxide lm lies at the bottom left corner of the unit cell. Both                                                       |      |

|      | the gold layer (in yellow) and the $VO_2$ have a thickness of 150 nm. (b)                                                       |      |

|      | Circuit model representing the bowtie antenna array. The vanadium lm is                                                         |      |

|      | represented as a variable resistor, with value ranging from 3.4 k $\Omega$ to 50 k $\Omega$                                     |      |

|      | dependent on temperature.                                                                                                       | 196  |

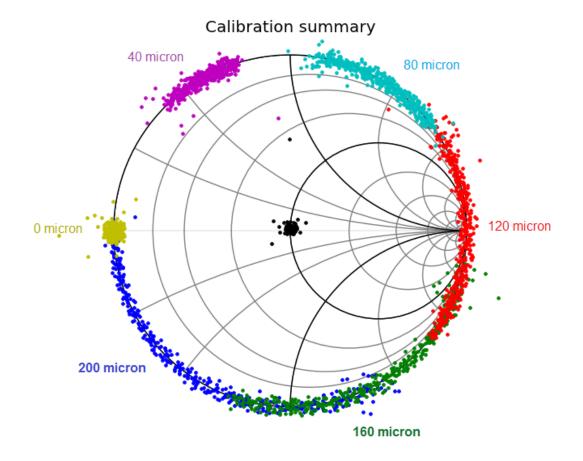

197

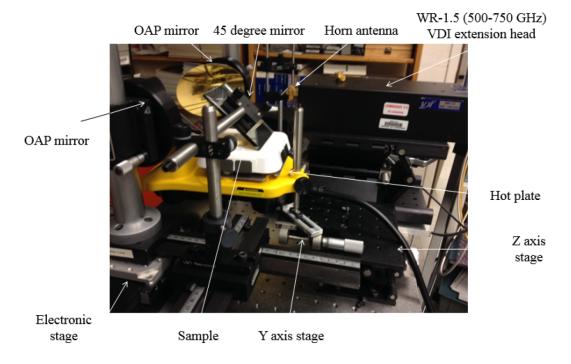

| G.4 | Reflection coefficient $S_{11}$ measurement setup for the WR-1.5 frequency |

|-----|----------------------------------------------------------------------------|

|     | range. The mirrors are used to direct the beam onto the sample that sits   |

|     | on the electronic hot plate. We can therefore ensure precise control and   |

|     | reading of the temperature of the hot plate and sample                     |

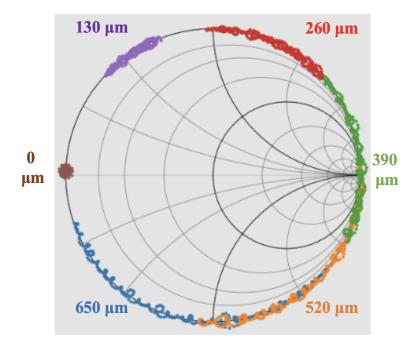

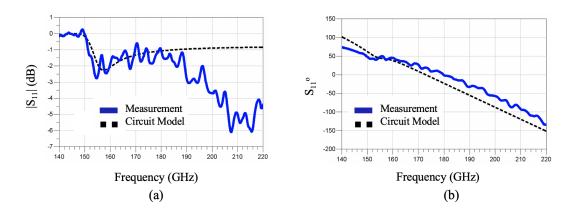

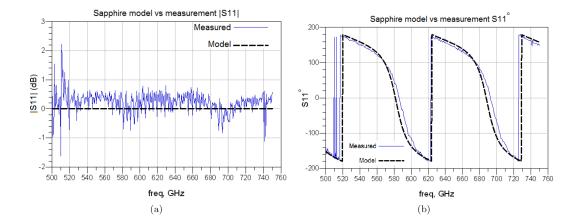

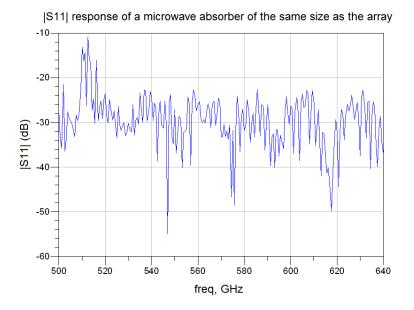

- G.6 (a) Magnitude of S<sub>11</sub> for a sapphire substrate with backshort conductor.

Sapphire is lossless over the WR-1.5 band and therefore all the energy is reflected back. There is a deviation by ±1 dB due to calibration error.

(b) Phase of S<sub>11</sub> (in degrees) for a piece of sapphire. The thickness of the piece of sapphire is 400 µm. The model also includes an air gap prior to the reference plane, and an air gap between the sample and the back short. 199

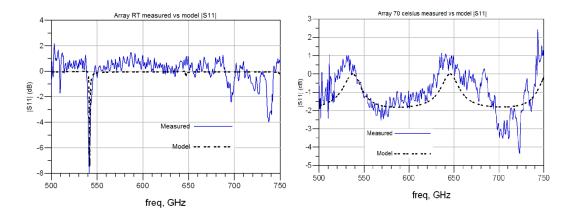

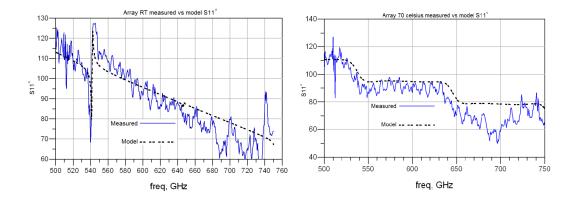

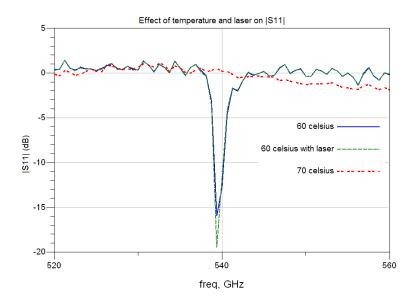

# G.8 (a) The magnitude of $S_{11}$ at room temperature in dB (semiconducting state). The absorption dip at 541 GHz shows coupling of the beam to the $VO_2$ film, (b) The magnitude of $S_{11}$ at 70 °C (metallic state). The absorption dip disappears which corresponds to the array being reflective. 201

# List of Tables

| 1.1 | Substrate properties for GaAs, Si, and quartz: relative dielec-<br>tric constant [26], loss tangent (at 10 GHz) [26], modulus of<br>resilience (in MPa) [26], thermal conductivity (W/m-K) [27], |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | and coefficient of thermal expansion $(10^{-6}/^{\circ}C)$ [27]                                                                                                                                  | 32  |

| 2.1 | New GaAs epitaxy for quasi-vertical diodes with InGaAs cap                                                                                                                                       |     |

|     | layers                                                                                                                                                                                           | 46  |

| 2.2 | Summary of the TLM specific contact resistance measurement                                                                                                                                       | 48  |

| 2.3 | RIE Dry Etch Parameters                                                                                                                                                                          | 55  |

| 2.4 | Extracted DC parameters for a 2.4 $\mu m,$ 3 $\mu m,$ and 4.0 $\mu m$ diam-                                                                                                                      |     |

|     | eter quasi-vertical diode. Conductance and saturation current                                                                                                                                    |     |

|     | normalized to the anode area are presented                                                                                                                                                       | 58  |

| 2.5 | Summary of the frontside processing steps                                                                                                                                                        | 61  |

| 2.6 | Si dry etch Oxford recipe.                                                                                                                                                                       | 62  |

| 3.1 | Summary of the parasitic element values with uncertainties.                                                                                                                                      | 77  |

| 3.2 | Reflection coefficient magnitude and phase errors associated                                                                                                                                     |     |

|     | with least-squares fitting                                                                                                                                                                       | 77  |

| 4.1 | Material thermal properties                                                                                                                                                                      | 92  |

| 4.2 | Extracted diode thermal parameters for diode (area $= 23.76$                                                                                                                                     |     |

|     | $\mu m^2$ ) vs power                                                                                                                                                                             | 98  |

| 4.3 | Measured thermal conductivities $\left(\frac{W}{m-K}\right)$ used in the quadrupler                                                                                                              |     |

|     | finite element analysis                                                                                                                                                                          | 107 |

| 4.4 | Measured thermal conductivities $\left(\frac{W}{m-K}\right)$ used in the quadrupler                                                                                                              |     |

|     | finite element analysis.                                                                                                                                                                         | 107 |

| 5.1 | Summary of the quasi-vertical diode membrane array processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

|     | steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 124  |  |  |

| 5.2 | Summary of the quasi-vertical diode Bosch array processing steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .129 |  |  |

| 5.3 | 5.3 Extracted DC parameters for a 36-element 2.4 $\mu m$ diameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |  |

|     | quasi-vertical diode array, compared to the extracted DC pa-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |  |  |

|     | rameters of a single 2.4 $\mu m$ diameter diode. $\hfill \hfill \h$ | 140  |  |  |

| 6.1 | Summary of the 520 GHz design parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 151  |  |  |

| A.1 | RIE Dry Etch Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 172  |  |  |

| A.2 | Typical Plating Condition (first plating)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 173  |  |  |

| B.1 | Si dry etch Oxford recipe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 174  |  |  |