# Machine Learning Models of Improving Effectiveness in Response to Semiconductors Shortage

A Thesis Prospectus In STS 4500 Presented to The Faculty of the School of Engineering and Applied Science University of Virginia In Partial Fulfillment of the Requirements for the Degree Bachelor of Science in Electrical Engineering Bachelor of Science in Computer Engineering

> By Xuanjia Bi

November 1, 2021

On my honor as a University student, I have neither given nor received unauthorized aid on this assignment as defined by the Honor Guidelines for Thesis-Related Assignments.

# ADVISORS

Adarsh Ramakrishnan, Department of Engineering and Society

Harry Powell, Department of Electrical and Computer Engineering

# I. Introduction

Semiconductors are an essential component of electronic devices, enabling advances in communications, computing, healthcare, military systems, transportation, clean energy, and countless other applications, according to the Semiconductor Industry Association. During COVID-19, many supply chains have a hard time keeping up with a huge surge in demand, and one of the major cautions is semiconductor chips for automotive. Semiconductor manufacturing plants are lagging behind in production; Boston Consulting Group shows American chipmakers' share of global production capacity declined from 37% in 1990 to 12% in 2020, while those in Europe fell from 44% in 1990 to 9% in 2020. In 2020, Apple has announced the mass production for flagship iphone 12 to be delayed for five weeks. Automotive industry is facing tremendous pressure from semiconductor shortage; the shortage is expected to cost the global automotive industry \$210 billion in revenue in 2021, according to consulting firm AlixPartners(Wayland, 2021), and the entry-level Tesla Model 3 requires an estimated 8 months of waiting. With no end in sight, Michael Dell, chief executive of Dell Technologies, believed the shortage would continue being the global issue for a few years. Solving semiconductor shortage has become one of the primary tasks in 2021 for many companies' leaders.

This paper offers two machine learning models to address the semiconductors shortage issues. Through the lens of Actor Network Theory, the current study shows how these two two machine learning models help semiconductor manufacturing decentralize fabrication plants and minimize the damage from environmental disasters. More details on this topic and the connection between the technical project and the present STS paper are given in the technical report and sociotechnical synthesis, respectively.

### II. Technical:

This paper will focus on improving the efficiency and pass ratio of fabricating in-demand semiconductors while providing water management solutions. According to Statista, approximately five billion U.S. dollars was wasted during fabricating semiconductors due to wafer crackages, equipment mismatching, and exploitation of ultra water. Improving the efficiency and correctness of fabrication is the only way to produce enough semiconductor chips for the growing market demand. This paper presents two machine learning models for improving semiconductor shortage resilience: the advanced process equipment matching (APEM) model and the scheduling model. These two models are expected to bring different enhancements for semiconductor manufacturing, and this paper discusses the potential of two in terms of production efficiency, financial cost, correctness of fabrication, and energy-saving as well as the concerns and existing drawbacks.

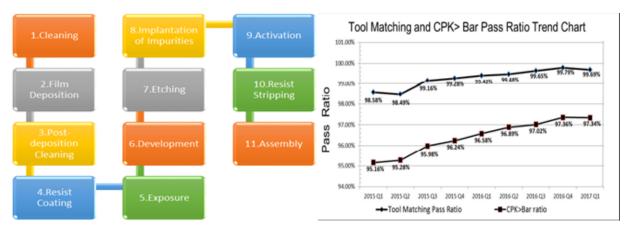

In order to assess how these two models enhance the mass production of semiconductors, it is essential to walk through the process of fabrication and establish a conventional understanding of each procedure. As stated by Dainippon Screen Mfg. Co., Ltd., the conventional fabrication has four major steps, wafer processing, die preparation, IC packing, and IC testing shown in Figure 1, as well as eleven procedures.

Below two models are developed by machine learning of artificial intelligence to tackle the issues in die preparation and IC packing. These two models optimal reduction of pass ratios and waiting time in semiconductor fabs. By applying these two models, semiconductor manufacturing can reduce the cost of fabrication plants in response to environmental disasters mentioned in the STS section as well .

2

Advanced process equipment matching methodology is a management method according to the tool match is a management method according to the SPC (Statistical Process Control) control mode. It is based on the inline (data collection on real products)/ offline (data collection on dummy wafers) monitor data to determine whether the EQP's actual process capability is able to achieve the golden level of the machine group which it belonging to, the golden level is setting by its belonging machine group's performance. Through this method, the abnormality can be detected and the correction can be executed in time .

In a fabrication plant, there are many machines sitting while waiting for new instructions. Scheduling model, also called the flexible capacity model, is designed to optimize the workload sequences for each machine and reduce the waiting time among machines in terms of reducing the cost of semiconductor manufacturing. In numerical study, the results show that the proposed strategy provides significant improvements in semiconductor wafer fabrication. This model produces multiple processes, provides additional capacity for each job, and reduces job waiting time.

#### **III. Methodology and Results**

# a. Advanced process equipment matching model

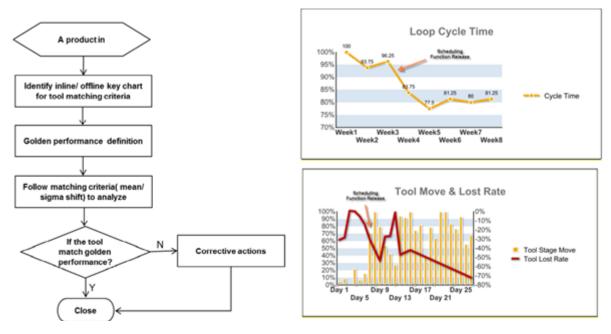

APEM defined three sets of numbers such as mean, sigma, and shift, to indicate if the fabrication matches its ideal performance. The data would transfer to such systems: manufacturing execution system, equipment monitoring system, statics process control system, and engineering data collection system, for further execution. Then the systems in the fab plant use a review mechanism based on the data to determine if the matching requires further adjustment. Figure 2 shows the routine review flow on actual manufacture.

#### b. Scheduling model

Scheduling model focuses on optimizing Equipment Flexibility and Loading Balance in the fabrication plant. The model leads to a short Qtime (waiting time) in order to improve the effectiveness of the production by applying expressions.

$$Min \quad a_{it} \sum_{i=1}^{m} O_{it} + TS + D \tag{1}$$

*s.t*.

$$s_{it} \le q_{it} + O_{it}, \forall i = 1, ..., m, \forall t = 1, ..., T.$$

(2)

$$arr_{it} \le s_{it}, \forall i = 1, ..., m, \forall t = 1, ..., T.$$

(3)

$$\sum_{j=1}^{n} x_{ijt} = 1, \forall i = 1, ..., m, \forall t = 1, ..., T.$$

(4)

$$s_{it} + p_{it} + b_i y_{it} = e_{it}, \forall i = 1, ..., m, \forall t = 1, ..., T.$$

(5)

Due to the purpose of this paper, further significance of Indices, variables, and parameters is not discussed. They apply the commercial software to solve the scheduling problem, and the results are presented below.

# c. Results

Such two machine learning algorithms have been proved by TSMC. There were several experiments conducted in TSMC research teams. After the implementation of APEM on a mature semiconductor production line, the tool matching pass ratios has made promising and continuous progression in Figure 3. The tool matching pass ratios have jumped from 98.5% to 99.7%, which is a large progressions in efficiency due to large scale manufacturing, after training the APEM machine learning models for three months. For the scheduling model, the loop cycle time also reduces 20% after two month of training shown in Figure 4.

## IV. STS

This paper focuses on analyzing the social factors by applying Actor Network Theory (ANT) demonstrates the machine learning models efficacy while decentralizing semiconductor fabrication plants. These same machine learning models show potential for minimizing environmental disasters such as droughts and fires.

ANT is a social theory originally developed by Michel Callon, Bruno Latour and John Law, which "represents technoscience as the creation of larger and stronger networks" with both human and non-human entities represented as actors in them. In the network, the actors are human; actants can be the objects, processes, and equipment. In other words, ANT is a theory to weigh technical, natural, and social factors equally and to consider the interconnections between these actors and realize the mutual determination between actors. With Actor Network Theory, the complex social factors caused the chip shortage can be further understood and analyzed.

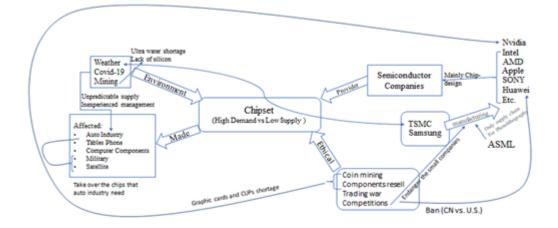

First there is a remaining essential question; what are the social factors that affect chip shortage? The current study walked through step by step from the top of suppliers down to clients. In summary, there are four major factors causing the supply chain to be unbalanced: the shrinking size of the supplier during COVID-19, the environment factors, the ethical interventions, and growing demands.

To visualize the social factors that cause semiconductor shortage, the study interprets the semiconductors into an ANT framework, showing in a social-technical diagram. This socio-technical diagram in the appendix shows the connections among the actors and objects. There are two main branches in this network, the supplier and the clients. The semiconductor manufacturers are directly affected by environmental factors such as COVID-19, the fire in Renesas, and the drought in TSMC. From the ethical part in the diagram, the Trading war between China and the United States and the digital-coin miners adds high pressure on the

supply chain as well. This paper uses ANT to create a framework for the above major actors and discuss how APEM and scheduling models tackle these issues.

In the semiconductor supply-demand portion, many companies such Apple, Intel, and AMD etc. play a part in designing chips. Due to the large cost of building a fabrication plant, except Intel, none of those chip-designing companies have their own commercial fabrication plants. Although there are some smaller firms offering semiconductor manufacturing, they could not supply advanced chips on a large scale. Thus, TSMC and Samsung take most of the responsibilities for supplying semiconductors globally. Thus, both manufacturers must work incessantly to keep up with the demand. Later, COVID-19 triggered the chipset crisis. As COVID-19 hit, TSMC and Samsung had to stop the plants to avoid large waste for running the plants without the clients. After the COVID-19 cooled down, the clients asked for more chips. However, the manufacturers spend a long time re-modifying and testing the equipment before putting designs on the production line. Thus, clumsiness of production makes the design stay in the design stage. For instance, Apple has reduced the production of iPhone from 100 million units of iPhone 12 in 2020 to 85 millions units of iPhone 13 in 2021. In ANT, The scalability of the production and growing demand has a direct relation; therefore, it is important to implement two proposed models. If the production efficiency is improved, scalability eventually will match with the surging demand.

The second social factor in the ANT is the environment. Due to the centralization of these semiconductor manufacturers, the disaster can play a huge impacting role on the production. As Taiwan experiences its worst drought in over 50 years, TSMC, which has over half of market shares in chip manufacturing, runs out of water to clean the wafer. For existing technology, it takes 8,500 liters of water to make 1 wafer of about 500 chips. If the fab plant adapts an APEM

6

model, by increasing the pass ratio, the fab plant will not waste excessive ultrawater. Also the APEM model and scheduling model reduce the cost of maintaining fab plants. Such that TSMC and other manufacturers can construct multiple fab plants in separate locations to avoid the effect of disaster on their only fab plant; decentralizations reduce the damage of disaster toward the whole production in a single company.

Although this paper shows the promising of these two machine learning models on increasing the pass ratio, improving the efficiency and flexibility and controlling the excessive waste, there still exist challenges and relationships not fully examined. Firstly, the impacts of governmental regulation, technological limitations and economic considerations were not discussed. As mentioned in the above diagram, for example, the United States has banned Chinese telecoms supplier and phone manufacturer Huawei for fearing that equipment could be used to spy on other countries and companies. Although the two models can help Huawei manufacture chips efficiently, if the United States still keeps banning Huawei nationally, none of the chips would be imported to solve the chip shortage.

The inherent complexities in these topics require a separate and more detailed analysis, whereas this STS paper was intended to study the merits of the technology more generally. Last but not the least, the fab plants require more skilled operators with specialized knowledge, and there will be more pressures and efforts on hiring labor to go to the affected areas and run the fab plants. This will require the introduction of a new training and recruitment program to human resources. The paper is focusing on providing solutions on existing global semiconductor shortages, but factors beyond the scope of this study need to be studied in order to more completely assess the feasibility of this actor's inclusion within the network.

# Conclusions

7

With implementation of APEM and scheduling models, the fabrication plant improves the efficiency of the mass production, reducing cost of mining and establishing new fabrication plants, and increasing the passing ratio for the products. From STS perspective, these two machine learning models show great promise on semiconductor shortage by decentralizing their fabrication plants all over the world. Although the global shortage in chipset will still last, the influenced area and influenced period will truly become smaller and shorter. Most importantly, under the insurance of these models, the shortage of semiconductor chips will not occur easily in the future. This paper focuses on the theories and the first step of establishing the models, there will be further technical and STS studies to implement the models into manufacturing.

# References

- Barrett, E. (2021, June 12). Taiwan's drought is exposing just how much water chipmakers like TSMC use (and reuse). Retrieved October 17, 2021, from https://fortune.com/2021/06/12/chip-shortage-taiwan-drought-tsmc-water-usage/

- Benqatla, M. S., Chikhaoui, D., & Bounabat, B. (2017). Actor network theory a framework of it collaboration. 2017 International Conference on Wireless Networks and Mobile Communications (WINCOM). doi:10.1109/wincom.2017.8238192

- Brown, C., & Linden, G. (2011). *Chips and change: How crisis reshapes the semiconductor industry* (1st ed.). MIT Press.

- Chuang, Y., Chang, Y., Dang, F. J., You, R. C., & Chang, S. M. (2013). Optimizing multi-station scheduling in consideration of equipment flexibility and loading balance in semiconductor wafer fabrication. ASMC 2013 SEMI Advanced Semiconductor Manufacturing Conference. doi:10.1109/asmc.2013.6552772

- Cosway, R. G., Burch, S. R., Rosser, A. D., & Lazok, P. T. (2016). A novel technique for epitaxy tool-to-tool and chamber matching and optimization: ER: Equipment reliability and productivity enhancements. 2016 27th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC). doi:10.1109/asmc.2016.7491090

- Huang, S. (2011). Tool matching statistical methodology and application. IEEE Xplore.

- Hwang, T., & Shi-Chung Chang, S. (2003). Design of a lagrangian relaxation-based hierarchical production scheduling environment for semiconductor wafer fabrication. *IEEE Transactions on Robotics and Automation*, 19(4), 566-578. doi:10.1109/tra.2003.814512

- Keane, S. (2019, February 3). Huawei Ban Timeline: Detained CFO makes deal with us justice department. Retrieved October 17, 2021, from https://www.cnet.com/tech/services-and-software/huawei-ban-timeline-detained-cfo-mak es-deal-with-us-justice-department/

- Liu, Z. J., Qian, H. H., & Liu, M. E. (2018). Advanced Process Equipment Matching Methodology in semiconductor manufacturing. 2018 China Semiconductor Technology International Conference (CSTIC). doi:10.1109/cstic.2018.8369285

- Pickett, B., & Zuniga, M. (n.d.). Modeling, scheduling, and dispatching in the dynamic environment of Semiconductor Manufacturing at FASL, Japan. 1997 IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop ASMC 97 Proceedings. doi:10.1109/asmc.1997.630779

- Rao, N., Kinney, P., & Gupta, A. (2008). High throughput wafer defect monitor for integrated metrology applications in photolithography. *Metrology, Inspection, and Process Control* for Microlithography XXII. doi:10.1117/12.772384

- Schulte, J. (2021, April 26). Additive Manufacturing, Supply Chains and Disaster Response. Retrieved October 17, 2021, from https://search.lib.virginia.edu/sources/uva\_library/items/c821gk55s

- Screen Co. (2021, August 03). Semiconductor Manufacturing Processes. Retrieved October 17, 2021, from https://www.screen.co.jp/spe/en/process

- SIA. (2020, October). What is a semiconductor? Retrieved October 17, 2021, from https://www.semiconductors.org/semiconductors-101/what-is-a-semiconductor/

- Sismondo, S. (2021). Science and Technology in Disaster Risk Reduction in Asia. Retrieved October 18, 2021, from https://www.academia.edu/47778072/Science\_and\_Technology\_in\_Disaster\_Risk\_Reduc tion\_in\_Asia

- Subbiah, V., & Bodenstab, J. (n.d.). Application of real-time expert systems in semiconductor manufacturing. *IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop - ASMC '92 Proceedings*. doi:10.1109/asmc.1992.253844

- Terpak, J., Laciak, M., Kacur, J., Durdan, M., Flegner, P., & Trefa, G. (2021). The mathematical model for indirect measurement of carbon concentration in the steelmaking process and its utilization in process control. 2021 22nd International Carpathian Control Conference (ICCC). doi:10.1109/iccc51557.2021.9454605

- Thomas, R., Husson, H., Garbuio, L., & Gerbaud, L. (2021). Comparative study of the tesla model S and Audi e-tron induction motors. *2021 17th Conference on Electrical Machines, Drives and Power Systems (ELMA)*. doi:10.1109/elma52514.2021.9503055

- Trudell, C. (2021, August 12). Elon Musk Calls Renesas and Bosch's Chip Supply 'Problematic'. Retrieved October 17, 2021, from https://www.bloomberg.com/news/articles/2021-08-12/tesla-s-musk-calls-renesas-and-bo sch-s-chip-supply-problematic

- Wayland, M. (2021, September 23). Chip shortage expected to cost auto industry \$210 billion in revenue in 2021. Retrieved October 17, 2021, from https://www.cnbc.com/2021/09/23/chip-shortage-expected-to-cost-auto-industry-210-billi on-in-2021.html#:~:text=Chip%20shortage%20expected%20to%20cost%20auto%20indu stry%20%24210%20billion%20in%20revenue%20in%202021,-Published%20Thu%2C% 20Sep&text=The%20semiconductor%20chip%20shortage%20is,according%20to%20con sulting%20firm%20AlixPartners.

- Willson, C. G., Dammel, R. R., & Reiser, A. (1997). Photoresist Materials: A historical perspective. Advances in Resist Technology and Processing XIV. https://doi.org/10.1117/12.275826

Xin, C. (2021, June 01). How A perfect storm created the global chip shortage. Retrieved October 17, 2021, from https://asia.nikkei.com/Spotlight/Caixin/How-a-perfect-storm-created-the-global-chip-sh ortage

# Appendix

Figure 1 Procedures of Traditional Fabrication

Figure 3 Achievement of Implementation of APEM in TSMC

Figure 2 Review Mechanism

Figure 4 Achievement of Scheduling Model in TSMC

Figure 5 Actor Network Theory Framework

| Indices         |                                                                    | Variable        |                                                                           |                  |                                                                                                                     |

|-----------------|--------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------|

| i               | The job                                                            | 0 <sub>it</sub> | The Qtime<br>violation time of<br>job <i>i</i> in Station <i>t</i> .      | S <sub>it</sub>  | The starting time of job $i$ to be processed in Station $t$ .                                                       |

| j               | The<br>equipment                                                   | TS              | The makespan                                                              | x <sub>ijt</sub> | The binary variable to determine job $i$ processed by equipment $j$ in station $t$ or not                           |

| t               | The station                                                        | D               | The difference<br>among the total<br>process time of<br>each equipment    | y <sub>it</sub>  | The binary variable to determine<br>the flexible capacity to be applied<br>to process job $i$ in station $t$ or not |

|                 |                                                                    | e <sub>it</sub> | The ending time of job $i$ to be processed in Station $t$ .               |                  |                                                                                                                     |

| Parameters      |                                                                    |                 |                                                                           |                  |                                                                                                                     |

| a <sub>it</sub> | The weight of<br>the variable<br>$O_{it}$ in station<br>t          | b <sub>i</sub>  | The setup time of flexible capacity to process job <i>i</i>               | arr <sub>i</sub> | The arrival time of job<br><i>i</i> in Station <i>t</i>                                                             |

| q <sub>it</sub> | The<br>remaining<br>Qtime of job<br><i>i</i> in Station <i>t</i> . | p <sub>it</sub> | The requiring<br>process time of<br>job<br><i>i</i> in Station <i>t</i> . |                  |                                                                                                                     |

Figure 6 Table for Scheduling Model