#### APPROVAL SHEET

This dissertation is submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy (Computer Science)

Sally A. McKee

stion has been read and approved by the Everyining

This dissertation has been read and approved by the Examining Committee:

William A. Wulf (Dissertation Advisor)

Jack W. Davidson (Committee Chair)

Andrew S. Grimshaw

James M. Ortega

James H. Aylor

Accepted for the School of Engineering and Applied Science:

R.W. Milz

Dean Richard W. Miksad School of Engineering and Applied Science

May 1995

# **Maximizing Memory Bandwidth for Streamed Computations**

#### A Dissertation

#### Presented to

the Faculty of the School of Engineering and Applied Science

at the

University of Virginia

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy (Computer Science)

by

Sally A. McKee

May 1995

© Copyright by

Sally A. McKee

All Rights Reserved

May 1995

To the memories of my grandmother, Helen Viola (1914-1993), and my great aunt, Eileen Alward (1915-1994).

### **Abstract**

Processor speeds are increasing much faster than memory speeds, and thus memory bandwidth is rapidly becoming the limiting performance factor for many applications, particularly those whose inner loops linearly traverse streams of vector-like data. Because they execute sustained accesses, these *streaming computations* are limited more by bandwidth than by latency. Examples of these kinds of programs include vector (scientific) computations, multi-media compression and decompression, encryption, signal processing, image processing, text searching, some database queries, some graphics applications, and DNA sequence matching.

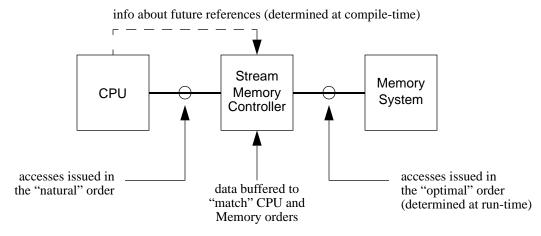

This dissertation proposes and analyzes a method for designing a computer memory subsystem to maximize memory performance for streaming computations, overcoming a problem not addressed by traditional techniques. Our approach is based on *access ordering*, or changing the order of memory requests to improve the rate at which those requests are serviced by a memory system with non-uniform access times. We propose a combined hardware/software approach: the compiler arranges for the processor to transmit stream information to a *Stream Memory Controller*, or SMC, at run-time; and the SMC dynamically reorders the accesses, attempting to issue them in a sequence that maximizes effective memory bandwidth. The processor issues its memory requests in the natural order

of the computation, and stream data is buffered within the controller until requested by the processor (for memory loads) or written to memory by the controller (for memory stores).

We demonstrate the viability and effectiveness of this approach by exploring the SMC design space through functional simulation and mathematical analysis. We then show how the uniprocessor solution can be extended to modest-size symmetric multiprocessors, and we address compiler and operating systems issues with respect to obtaining good memory system performance. For long-vector computations, the SMC represents a significant improvement over non-SMC systems, including those that employ traditional caching. For our set of benchmark kernels, we observe speedups by factors of 2 to 23 over systems that issue non-caching loads and stores in the natural order of the computation. Furthermore, the technique is practical to implement, exploiting existing compiler technology and requiring only a modest amount of special-purpose hardware. A prototype uniprocessor implementation has been fabricated as part of a larger research effort at the University of Virginia, and initial tests suggest that the SMC meets its performance specifications.

I shall be telling this with a sigh

Somewhere ages and ages hence:

Two roads diverged in a wood, and I —

I took the one less traveled by,

And that has made all the difference.

— "The Road Not Taken"

Robert Frost (1874-1963)

### Acknowledgments

As a woman in Computer Architecture, I have certainly taken the "road less traveled". For me, the path itself has made only some of the difference. The rest is due to the people I've encountered along the way, for they have made my life inestimably richer.

My friend Matt Blaze has wisely observed that in both doing research and acknowledging those who made the work possible, one must eventually realize that perfection is impossible and that "good enough" is just that. Just as there are always more experiments to be done and more references to search, there is always someone else to acknowledge and a better way to express gratitude. Eventually, I have to write something down, knowing that I risk omitting something or someone. I cannot begin to acknowledge all who have made this work possible, but for the most part, you know who you are. I will instead risk naming only a few, focusing on those who have been utterly indispensable, and those who may not realize just how much of a difference they've made. I apologize to those whom I have unintentionally slighted.

Bill Wulf has been advisor, teacher, and neighbor, but above all, friend. Bill was instrumental in my coming to Virginia to pursue my Ph.D., a move I have not once had cause to regret. Without him, I would certainly have given up on graduate school long ago. In addition to performing all the duties of a good advisor, he stood behind me (pushing at

all the right moments), laughed at my jokes, and even participated in my Halloween costume.\* Most importantly, he has always believed in me.

The other members of the SMC team, past and present, are Assaji Aluwihare, Jim Aylor, Alan Batson, Charlie Hitchcock, Bob Klenke, Trevor Landon, Sean McGee, Steve Moyer, Chris Oliver, Bob Ross, Max Salinas, Andy Schwab, Chenxi Wang, Dee Weikle, Ken Wright, and Bill Wulf. I am fortunate to have had the opportunity to collaborate with so many bright and capable people; they have taught me many things, and have in some sense provided the raison d'etre for my work. Seeing how my ideas helped shape the design of a real system has been tremendously rewarding.

Bill Wulf's group of students (current members are Chris Oliver, Ramesh Peri, Dee Weikle, Brett Tjaden, Alec Yasinsac, and Chenxi Wang; former members include Katie Oliver and Steve Moyer) provided me with excellent feedback at every step along the way. In addition, Joe Lavinus Ganley helped me work out the initial ideas that led to my analytic models, and Anand Natrajan helped me reason about the multiprocessor extensions to the startup delay model. Charlie Viles and Dallas Wrege have been sounding boards on several occasions. Norman Ramsey, Alan Batson, and Jack Davidson provided thoughtful comments to improve the quality of my writing.

The students, faculty, and staff of the Computer Science Department at Virginia have helped make my time here enjoyable and productive. Thank you for giving me a sense of community, for valuing my contributions and sharing with me all of yours.

This work was funded in part by the National Science Foundation and Intel Corporation. The Joint Institute for Computer Science at the University of Tennessee provided access to the i860 used to validate the analytic models of Chapter 2.

<sup>\*</sup> I was Little Red Riding Hood; Wulf was Big and Bad.

I am grateful to all the friends and "adopted family" who have helped make my various abodes "home": David Byrne; Karin Petersen and Jim Plank; Tish, Frank, and John Kelley; Dave Stein; and John Smith, Greg Lindahl, and Ari Rapkin. Special thanks go to Chuck Kalmanek for bringing Otis the Wonderdog into my life (yes, Otis is just a dog, but he's had a profound impact on the quality of my daily life).

Many people have provided inspiration or encouragement over the years, or have conspired to make my time in graduate school enjoyable and memorable. Along with many of the people mentioned above, this wonderful group includes (but is not limited to) Adam Buchsbaum, Ramón Cáceres, John Chamberlain, Steve Chapman, Matt Conway, Mike Delong, Bryan Diehl, Rob Ferguson, Mary Fernandez, Carsten Gebhardt, Mark Greenstreet, Kim Gregg, Anita Jones, Tina Kelley, Eleftherios Koutsofios, Kai Li, Béatrice Michel, Mike Macdonald, Francesmary Modugno, Pat Parseghian, Chris Rothko, Rich Schaefer, Emily Schifrin, Norbert Schlenker, Ed Smierciak, Lynn Smierciak, John Taylor, Tom Thivierge, Julia Walker, Haishu Wang, Emily West, Bryan Willman, Tongtong Zhang, and Jenny Zhao. Andrew Appel, Marc Brown, Gabe Robins, and Kevin Sullivan gave good advice and assistance when I needed it.

I have been blessed with many excellent teachers, all of whom contributed to my choosing the path I did and sticking with it. My parents first taught me to love learning. After that, Jurata Evans taught me how to read; Ann Trovillion-Timm taught me how to write; Alan Perlis taught me how to think; and Alfred Ganz, Rob Pike, and Paul Reynolds have helped me learn how to put it all together. The two eldest Williams sisters, Helen Williams Viola, and Eileen Williams Alward, were wonderful role models: their wit, wisdom, kindness, and lifelong dedication to teaching have always been an inspiration.

Finally, I thank my parents, Alton and Donna McKee, for always telling me I could be anything I wanted. And I thank all my family for their love, patience, and support while I figured out what I wanted to be, and went about becoming it.

### Contents

| List of Figures |      |         |                                        |                             | xiii |

|-----------------|------|---------|----------------------------------------|-----------------------------|------|

| List of Symbols |      |         |                                        | xvi                         |      |

| 1               | Intr | oductio | n                                      |                             | 1    |

|                 | 1.1  | Memor   | ry Hierarch                            | y                           | 1    |

|                 | 1.2  | The Mo  | emory Ban                              | dwidth Problem              | 6    |

|                 | 1.3  | Motiva  | ition                                  |                             | 6    |

|                 | 1.4  | Organi  | zation of th                           | e Thesis                    | 8    |

| 2               | Acc  | ess Ord | ering                                  |                             | 11   |

|                 | 2.1  | Bandw   | idth Examp                             | ole                         | 12   |

|                 | 2.2  | Taxono  | Taxonomy of Access Ordering Techniques |                             |      |

|                 |      | 2.2.1   | Compile                                | -Time Schemes               | 15   |

|                 |      | 2.2.2   | Run-time                               | e Schemes                   | 17   |

|                 | 2.3  | Evalua  | valuation of Access Ordering           |                             |      |

|                 |      | 2.3.1   | Performa                               | ance Models                 | 19   |

|                 |      |         | 2.3.1.1                                | Naive Accessing             | 20   |

|                 |      |         | 2.3.1.2                                | Block Prefetching           | 21   |

|                 |      |         | 2.3.1.3                                | Streaming into Local Memory | 24   |

|                 |      |         | 2.3.1.4                                | Static Access Ordering      | 25   |

|                 |      |         | 2.3.1.5                                | Dynamic Access Ordering     | 27   |

|                 |      | 2.3.2   | Performa                               | ance Examples               | 30   |

|                 |      |         | 2.3.2.1                                | Analytic Results            | 30   |

|                 |      |         | 2.3.2.2                                | Empirical Results           | 35   |

|                 | 2.4  | Related | d Work                                 |                             | 38   |

|                 | 2.5  | Summa   | ary                                    |                             | 41   |

Contents xi

| 3 | Unip                             | rocesso  | SMC Performance         |                                         | <b>43</b> |

|---|----------------------------------|----------|-------------------------|-----------------------------------------|-----------|

|   | 3.1 Ordering Policy Design Space |          |                         | • • • • • • • • • • • • • • • • • • • • | . 44      |

|   |                                  | 3.1.1    | Bank Selection          |                                         | . 45      |

|   |                                  | 3.1.2    | Fifo Selection          |                                         | . 46      |

|   | 3.2                              | Analytic | Models                  |                                         | . 47      |

|   |                                  | 3.2.1    | Modeling Assumptions .  |                                         | . 48      |

|   |                                  | 3.2.2    | Startup-Delay Model     |                                         | . 49      |

|   |                                  | 3.2.3    | Asymptotic Models       |                                         | . 51      |

|   |                                  |          | 3.2.3.1 Multiple-Vect   | or Computations                         | . 51      |

|   |                                  |          | 3.2.3.2 Single-Vector   | and Large-Stride Computations           | . 53      |

|   | 3.3                              | Simulat  | on Models               |                                         | . 54      |

|   |                                  | 3.3.1    | Simulation Environment  |                                         | . 55      |

|   |                                  |          | 3.3.1.1 Benchmark Su    | iite                                    | . 56      |

|   |                                  |          | 3.3.1.2 Ordering Police | cies                                    | . 57      |

|   |                                  | 3.3.2    | Comparative Results     |                                         | . 57      |

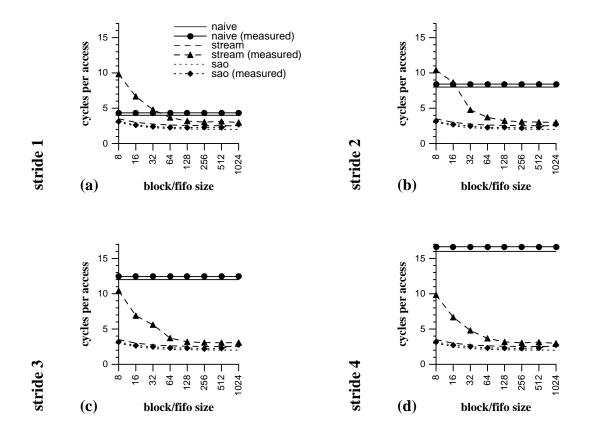

|   |                                  |          | 3.3.2.1 Analysis versu  | s Simulation                            | . 57      |

|   |                                  |          | 3.3.2.2 Bank-Centric    | versus FIFO-Centric Ordering            | . 63      |

|   |                                  |          | 3.3.2.3 Reordered ver   | sus Natural-Order Accesses              | . 72      |

|   | 3.4                              | Summa    | y                       |                                         | . 73      |

| 4 | Mult                             | iproces  | or SMC Performance      |                                         | 75        |

|   | 4.1                              | System   | Architecture            |                                         | . 76      |

|   | 4.2                              | Task Pa  | k Partitioning          |                                         |           |

|   | 4.3                              |          |                         |                                         | . 79      |

|   |                                  | 4.3.1    | Startup-Delay Model     |                                         | . 80      |

|   |                                  | 4.3.2    | Asymptotic Models       | • • • • • • • • • • • • • • • • • • • • | . 82      |

|   | 4.4                              | Simulat  | on Models               |                                         | . 84      |

|   |                                  | 4.4.1    | Ordering Policy         |                                         | . 85      |

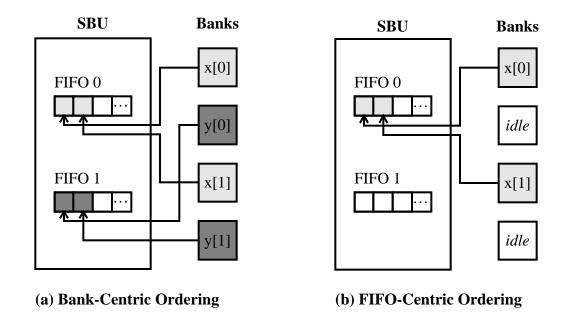

|   |                                  |          | 4.4.1.1 Bank-Centric    | Approach                                | . 86      |

|   |                                  |          | 4.4.1.2 FIFO-Centric    | Approach                                | . 87      |

|   |                                  |          | 4.4.1.3 Algorithms Si   | mulated                                 | . 88      |

|   |                                  | 4.4.2    | Performance Factors     | • • • • • • • • • • • • • • • • • • • • | . 89      |

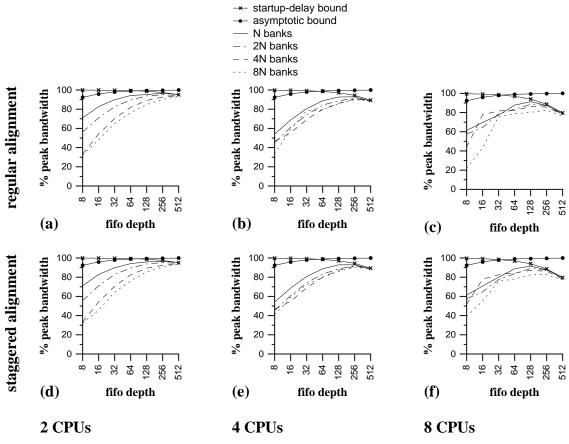

|   |                                  |          | 4.4.2.1 Data Layout .   |                                         | . 90      |

|   |                                  |          | 4.4.2.2 FIFO depth      |                                         | . 92      |

|   |                                  |          | 4.4.2.3 Workload Dis    | tribution                               | . 93      |

|   |                                  | 4.4.3    | Results                 |                                         | . 93      |

|   |                                  |          | 4.4.3.1 Block Schedul   | ling versus Cyclic Scheduling           | . 94      |

|   |                                  |          | 4.4.3.2 Performance 7   | Frends                                  | 106       |

|   | 4.5                              | Related  | Work                    |                                         | 112       |

|   | 4.6                              | Summa    | y                       |                                         | 113       |

Contents

| 5                         | Span             | parse Matrix Computations 11       |                                                   |     |

|---------------------------|------------------|------------------------------------|---------------------------------------------------|-----|

|                           | 5.1              | Sparse                             | Matrix Data Structures                            | 116 |

|                           | 5.2              | Access                             | Patterns                                          | 119 |

|                           |                  | 5.2.1                              | Regular Access Patterns                           | 119 |

|                           |                  | 5.2.2                              | Irregular Access Patterns                         | 120 |

|                           | 5.3              | Modeli                             | ing Assumptions                                   | 121 |

|                           | 5.4              | Results                            | 5                                                 | 122 |

|                           | 5.5              | Summa                              | ary                                               | 128 |

| 6                         | The SMC Hardware |                                    | 131                                               |     |

|                           | 6.1              | Overvi                             | ew                                                | 132 |

|                           | 6.2              | Archite                            | ecture                                            | 133 |

|                           | 6.3              | Prograi                            | mmer's Interface                                  | 136 |

|                           | 6.4              | Summa                              | ary                                               | 138 |

| 7                         | Con              | npiling f                          | for Dynamic Access Ordering                       | 139 |

|                           | 7.1              | Genera                             | nting Code for Streaming                          | 140 |

|                           |                  | 7.1.1                              | Recurrence Detection and Optimization Algorithm . | 141 |

|                           |                  | 7.1.2                              | Streaming Optimization Algorithm                  | 143 |

|                           | 7.2              |                                    |                                                   |     |

|                           | 7.3              | Selecting FIFO Depth               |                                                   |     |

|                           | 7.4              | Choosing a Parallelization Scheme  |                                                   |     |

|                           | 7.5              | Selecting the Number of Processors |                                                   |     |

|                           | 7.6              | Cache Coherence                    |                                                   |     |

|                           | 7.7              | Related Work                       |                                                   |     |

|                           | 7.8              | 7.8 Summary                        |                                                   |     |

| 8                         | Oth              | er Syste                           | ems Issues                                        | 155 |

|                           | 8.1              | Data C                             | oherence                                          | 155 |

|                           |                  | 8.1.1                              | Memory Consistency Models                         | 157 |

|                           |                  | 8.1.2                              | Coherence Mechanisms                              | 158 |

|                           |                  |                                    | 8.1.2.1 Snooping                                  | 159 |

|                           |                  |                                    | 8.1.2.2 Directories                               | 160 |

|                           | 8.2              | Virtual                            | Memory                                            | 162 |

|                           | 8.3              | Contex                             | ct Switching                                      | 164 |

| 8.4 Summary               |                  |                                    |                                                   | 166 |

| 9                         | Con              | clusions                           | S                                                 | 167 |

| $\mathbf{A}_{\mathbf{j}}$ | ppeno            | dix A A                            | Access Ordering Source                            | 171 |

| Bi                        | bliog            | raphy                              |                                                   | 183 |

|                           | 0                |                                    |                                                   |     |

## List of Figures

| 1 | Intr | roduction                                                         | 1    |

|---|------|-------------------------------------------------------------------|------|

|   | 1.1  | Typical Memory Hierarchy                                          | 2    |

|   | 1.2  | Interleaved Memory System                                         |      |

|   | 1.3  | DRAM Organization                                                 | 4    |

|   | 1.4  | Dynamic Access Ordering System                                    | 8    |

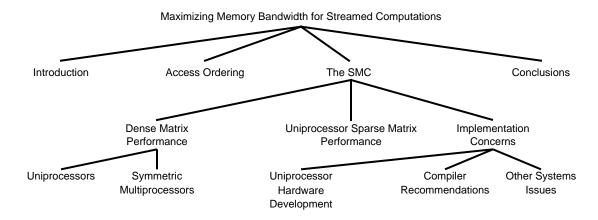

|   | 1.5  | Dissertation Structure                                            | . 10 |

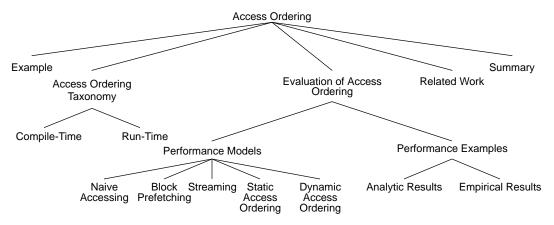

| 2 | Acc  | ess Ordering                                                      | 11   |

|   | 2.1  | Chapter Structure                                                 | . 12 |

|   | 2.2  | tridiag Code                                                      | . 13 |

|   | 2.3  | tridiag Memory Performance                                        | . 14 |

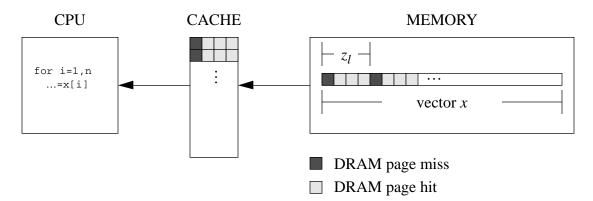

|   | 2.4  | Naive Accessing (Traditional Caching)                             | . 21 |

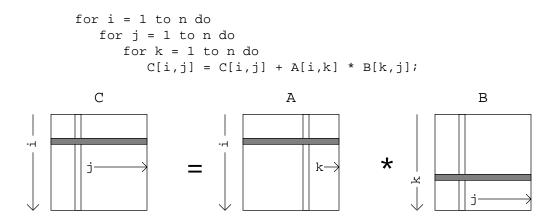

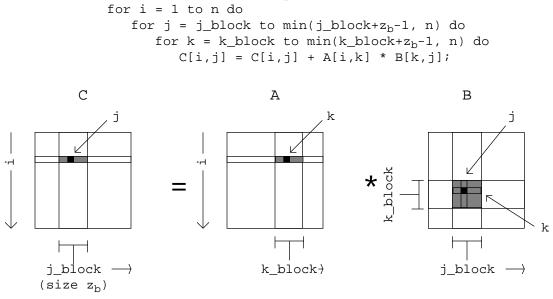

|   | 2.5  | Data Access Pattern in Unblocked (Natural) Matrix Multiplication  | . 22 |

|   | 2.6  | Data Access Pattern in Blocked Matrix Multiplication              | . 22 |

|   | 2.7  | Block Prefetching                                                 |      |

|   | 2.8  | Streaming Data into Cache                                         | . 25 |

|   | 2.9  | Static Access Ordering                                            | . 26 |

|   | 2.10 | Stream Memory Controller System                                   | . 28 |

|   | 2.11 | Dynamic Access Ordering via the SMC                               | . 29 |

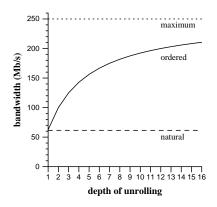

|   | 2.12 | Vector Load Performance                                           | . 31 |

|   | 2.13 | Vector Load Performance for Increasing Page Miss/Hit Cost Ratios. | . 33 |

|   | 2.14 | Scaled Vector Load Performance for Decreasing Page Hit Costs      | . 34 |

|   | 2.15 | Vector Load Performance for Increasing Strides                    | . 35 |

|   | 2.16 | Vector Load Performance for the i860XR                            | . 37 |

| 3 | Uni  | processor SMC Performance                                         | 43   |

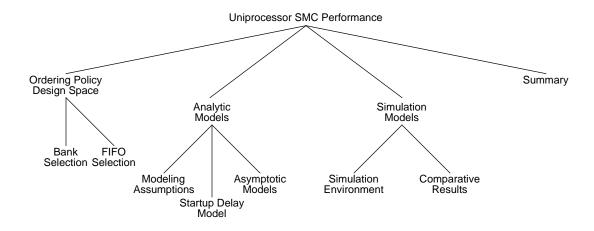

|   | 3.1  | Chapter Structure                                                 | . 44 |

List of Figures xiv

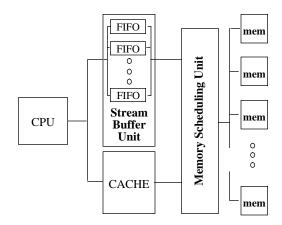

|   | 3.2                                                                                                                          | Uniprocessor Stream Memory Controller (SMC) System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 45                                                                                                              |

|---|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

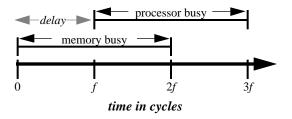

|   | 3.3                                                                                                                          | Startup Delay for 2 Read-Streams of Length f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 50                                                                                                              |

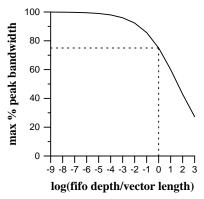

|   | 3.4                                                                                                                          | Performance Limits Due to Startup Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 51                                                                                                              |

|   | 3.5                                                                                                                          | Benchmark Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 57                                                                                                              |

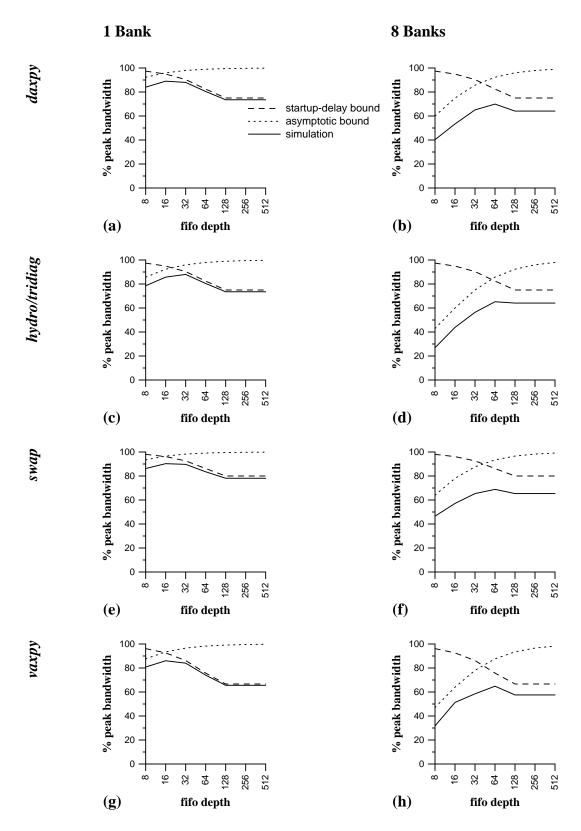

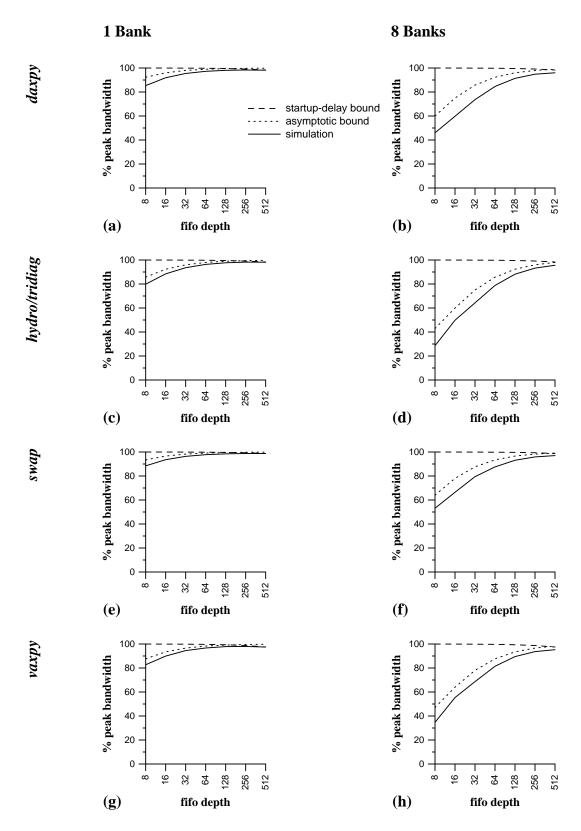

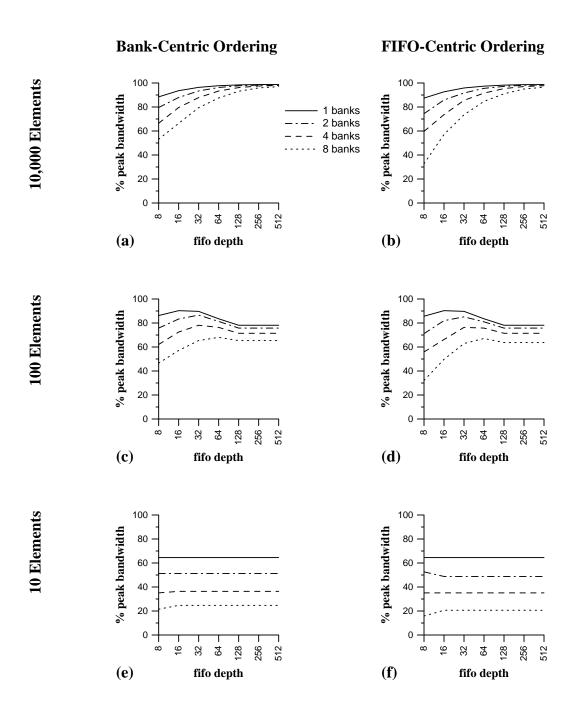

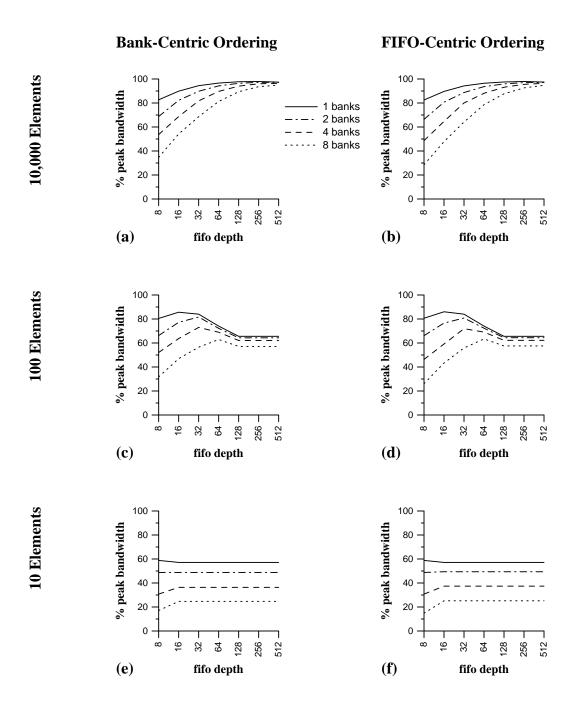

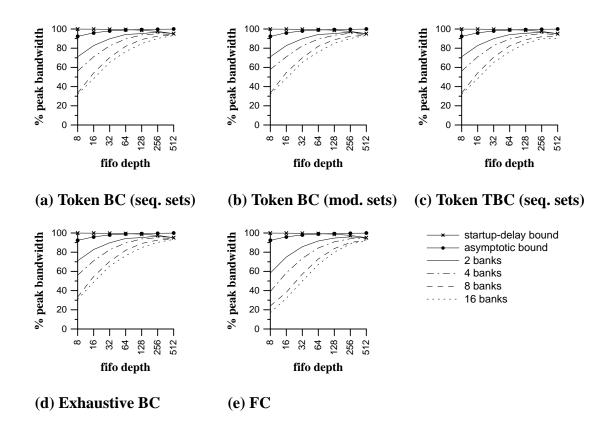

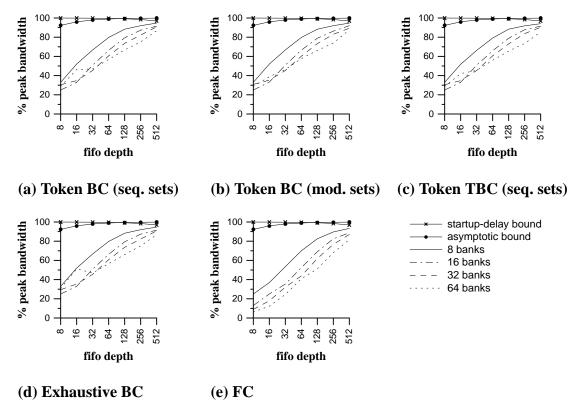

|   | 3.6                                                                                                                          | Medium-Vector Performance for Multi-Vector Kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 59                                                                                                              |

|   | 3.7                                                                                                                          | Long-Vector Performance for Multi-Vector Kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 60                                                                                                              |

|   | 3.8                                                                                                                          | Long- and Medium-Vector Performance for scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 61                                                                                                              |

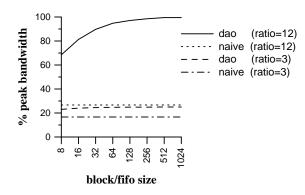

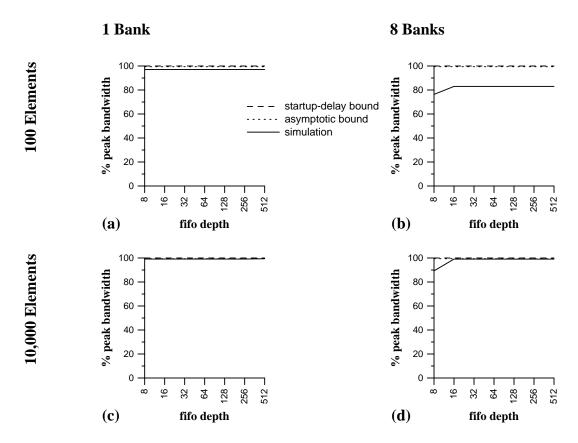

|   | 3.9                                                                                                                          | copy Performance When Bandwidth Scales with Interleaving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 62                                                                                                              |

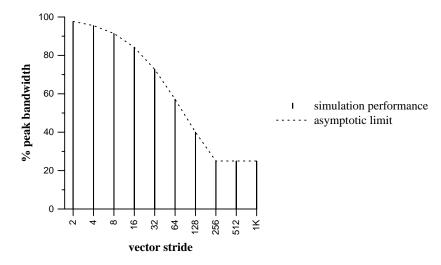

|   | 3.10                                                                                                                         | Asymptotic Limits for Increasing Strides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 62                                                                                                              |

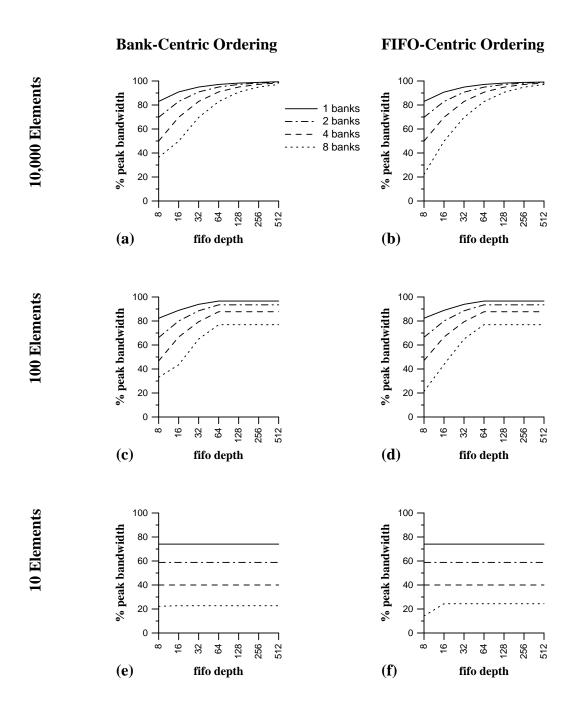

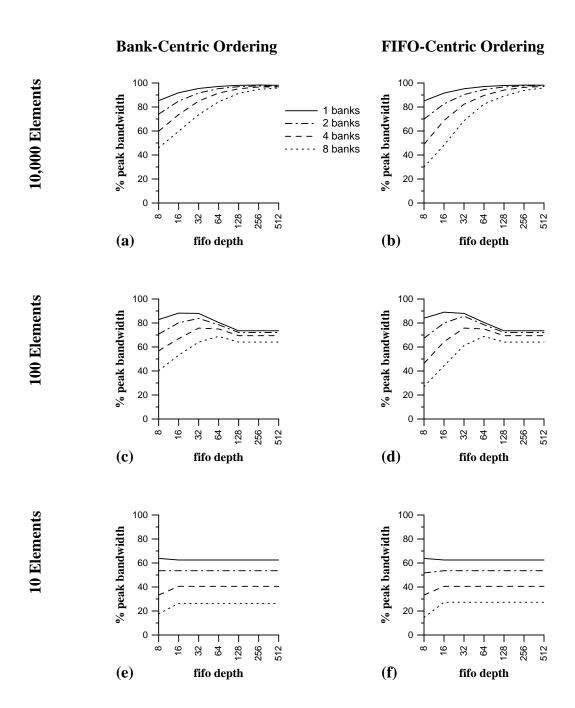

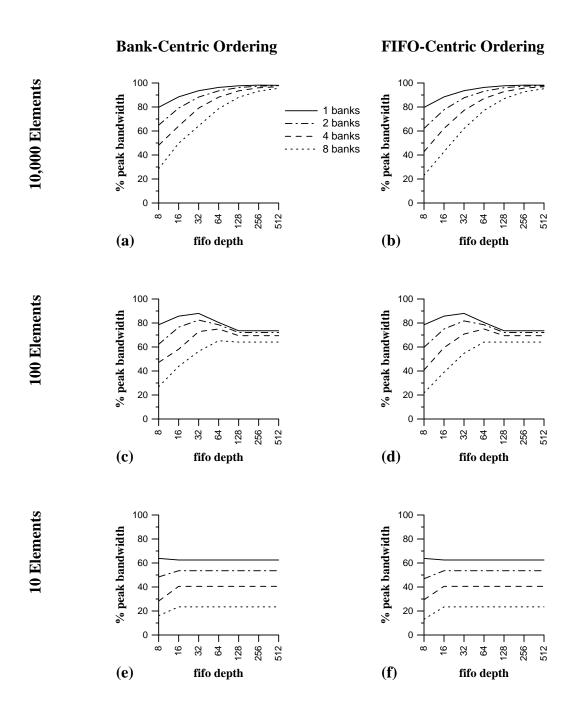

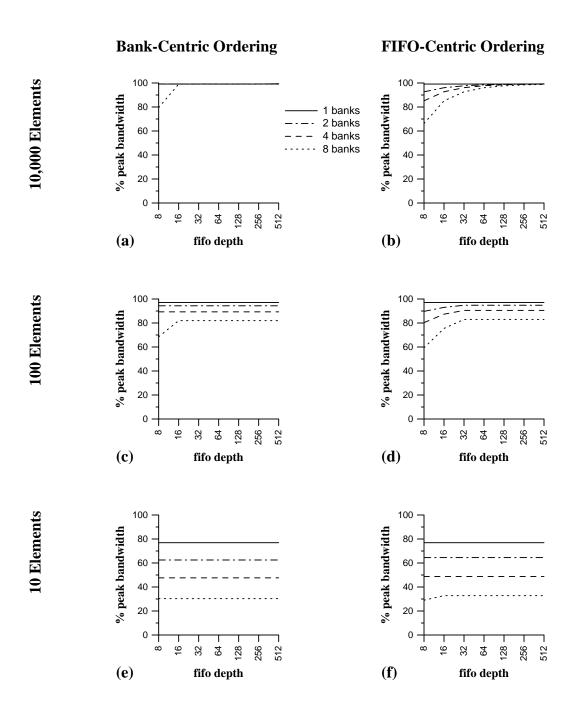

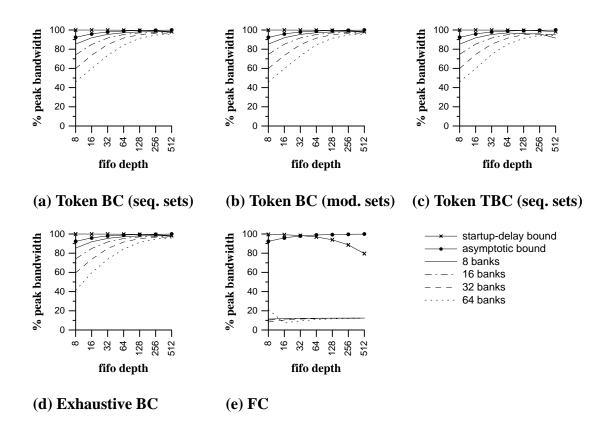

|   | 3.11                                                                                                                         | Simulation Performance for <i>copy</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 64                                                                                                              |

|   | 3.12                                                                                                                         | Simulation Performance for <i>daxpy</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 65                                                                                                              |

|   | 3.13                                                                                                                         | Simulation Performance for <i>hydro/tridiag</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 66                                                                                                              |

|   | 3.14                                                                                                                         | Simulation Performance for <i>scale</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 67                                                                                                              |

|   | 3.15                                                                                                                         | Simulation Performance for <i>swap</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 68                                                                                                              |

|   | 3.16                                                                                                                         | Simulation Performance for <i>vaxpy</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 69                                                                                                              |

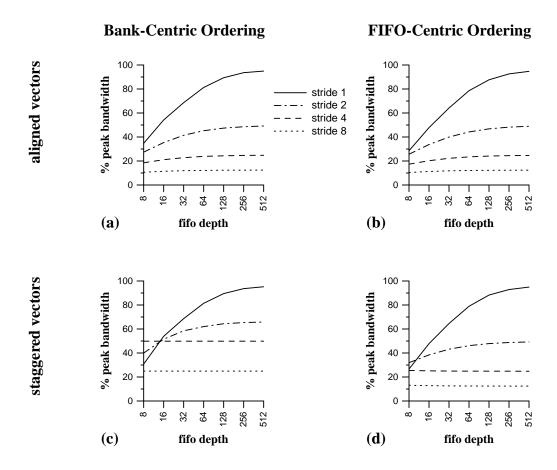

|   | 3.17                                                                                                                         | Bank Concurrency for Stride-2 Vectors with Staggered Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 70                                                                                                              |

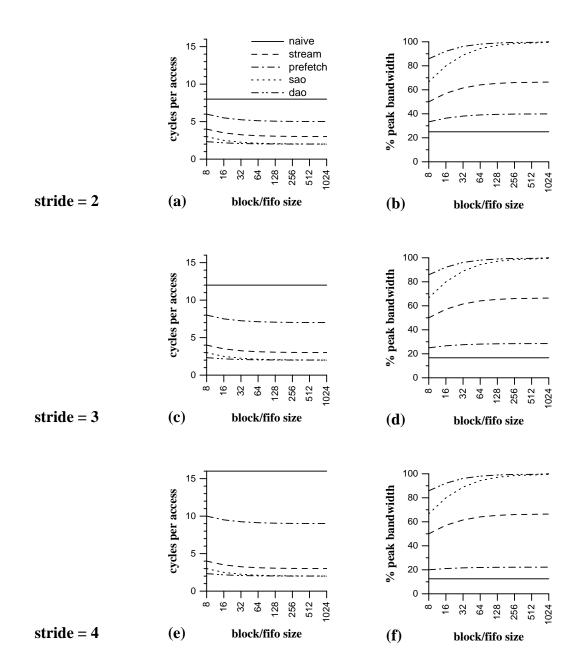

|   | 3.18                                                                                                                         | BC versus FC for Non-Unit Stride <i>vaxpy</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 71                                                                                                              |

|   | 3.19                                                                                                                         | Comparison of Non-SMC and SMC Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 73                                                                                                              |

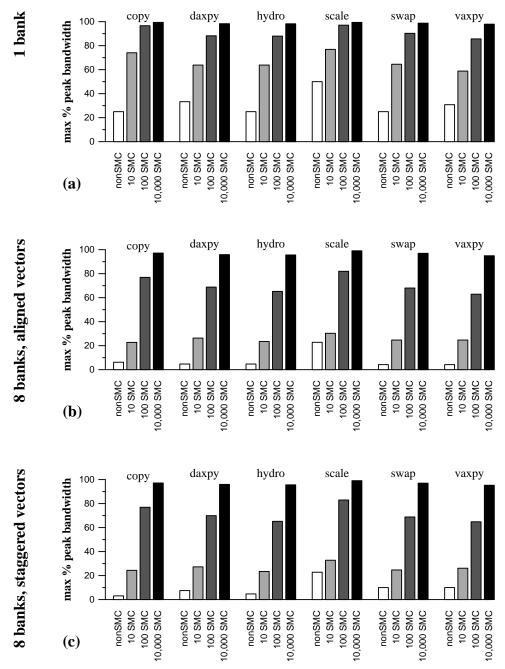

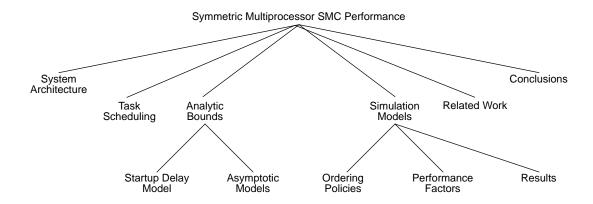

| 4 | Mul                                                                                                                          | tiprocessor SMC Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75                                                                                                                |

|   |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                   |

|   | 4.1                                                                                                                          | Chapter Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 75                                                                                                              |

|   | 4.1<br>4.2                                                                                                                   | Chapter Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                   |

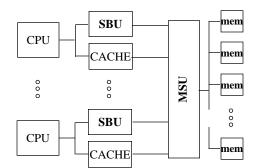

|   |                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 76                                                                                                              |

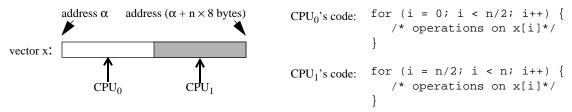

|   | 4.2                                                                                                                          | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79                                                                                              |

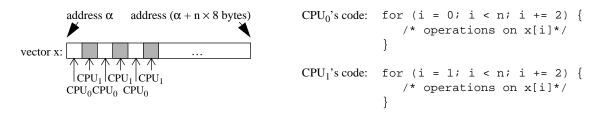

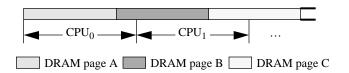

|   | 4.2<br>4.3                                                                                                                   | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79                                                                                              |

|   | 4.2<br>4.3<br>4.4                                                                                                            | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89                                                                                      |

|   | 4.2<br>4.3<br>4.4<br>4.5                                                                                                     | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89                                                                                      |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                              | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91                                                                      |

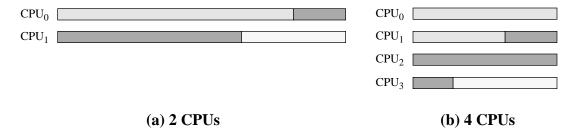

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                                                                       | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91                                                                      |

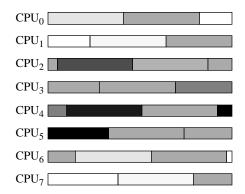

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                                                         | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92                                                              |

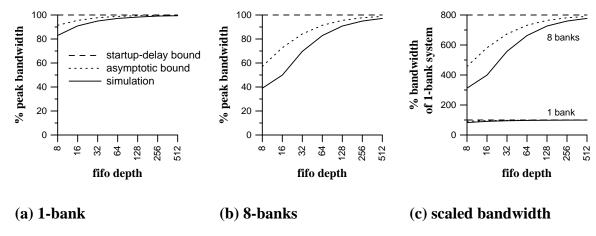

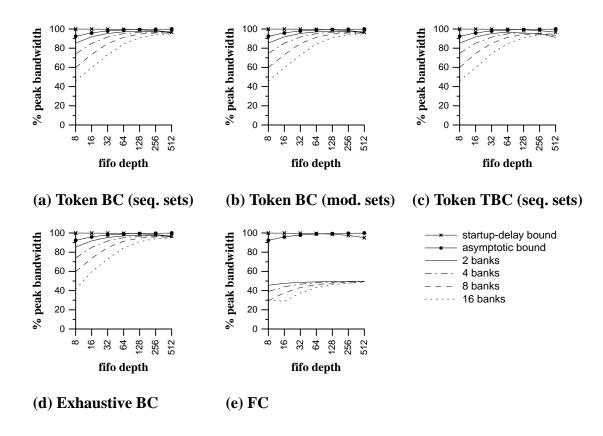

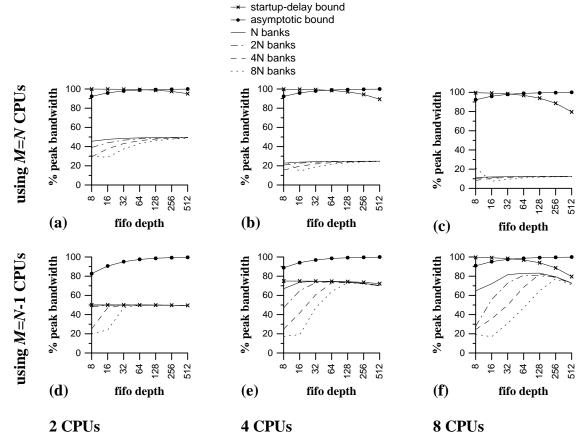

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                                                                 | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92<br>. 95<br>. 96                                              |

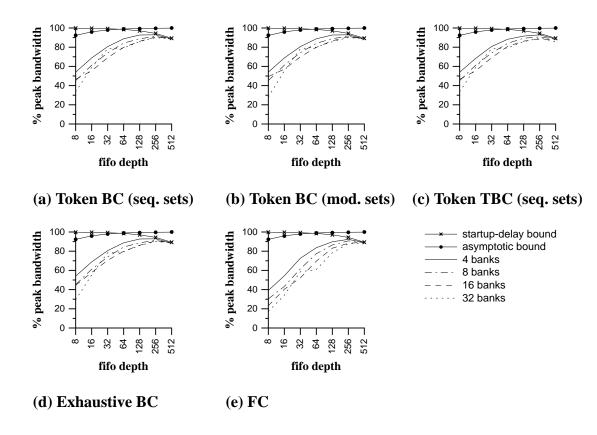

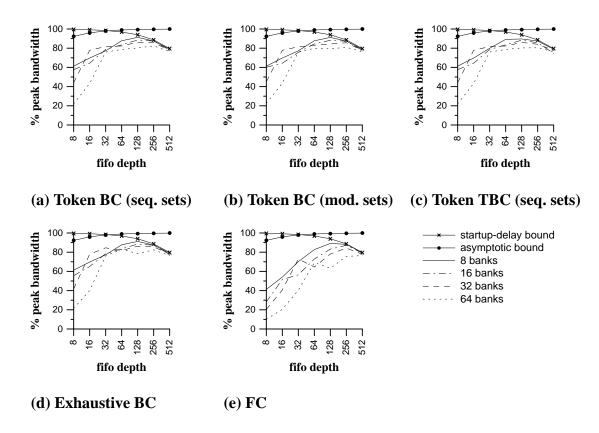

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                                                         | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92<br>. 95<br>. 96<br>. 97                                      |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12                                                 | Symmetric Multiprocessor SMC Organization  Prescheduling: Data Distribution for 2-CPU System  Cyclic Static Scheduling: Data Distribution for a 2-CPU System.  Five Ordering Policies  Vector Layout in Memory  Distribution of 10,000-Element Vector for 8 Banks  Blocked Distribution of 80,000 Elements for 8 Banks and 8 CPUs  Blocked daxpy Performance for 2 CPUs  Blocked daxpy Performance for 4 CPUs  Blocked daxpy Performance for 8 CPUs                                                                                                                                                                                                                                  | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92<br>. 95<br>. 96<br>. 97                                      |

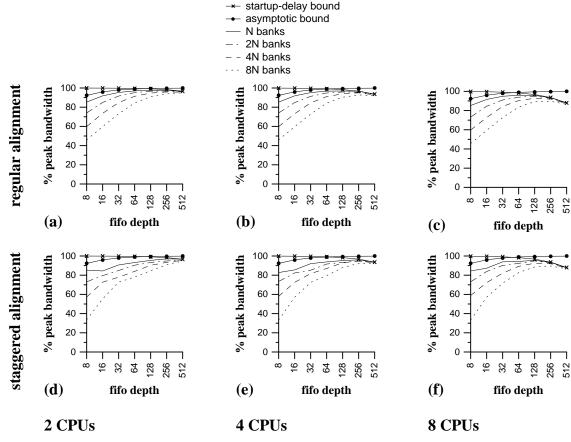

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13                                         | Symmetric Multiprocessor SMC Organization  Prescheduling: Data Distribution for 2-CPU System  Cyclic Static Scheduling: Data Distribution for a 2-CPU System.  Five Ordering Policies  Vector Layout in Memory  Distribution of 10,000-Element Vector for 8 Banks  Blocked Distribution of 80,000 Elements for 8 Banks and 8 CPUs  Blocked daxpy Performance for 2 CPUs  Blocked daxpy Performance for 4 CPUs  Blocked daxpy Performance for 8 CPUs  Blocked daxpy Performance for 2 Data Alignments                                                                                                                                                                                 | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92<br>. 95<br>. 96<br>. 97<br>. 98                              |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14                                 | Symmetric Multiprocessor SMC Organization  Prescheduling: Data Distribution for 2-CPU System  Cyclic Static Scheduling: Data Distribution for a 2-CPU System.  Five Ordering Policies  Vector Layout in Memory  Distribution of 10,000-Element Vector for 8 Banks  Blocked Distribution of 80,000 Elements for 8 Banks and 8 CPUs  Blocked daxpy Performance for 2 CPUs  Blocked daxpy Performance for 4 CPUs  Blocked daxpy Performance for 8 CPUs  Blocked daxpy Performance for 2 Data Alignments  Blocked daxpy Performance for 8 CPUs and 80,000-Element Vectors                                                                                                                | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 95<br>. 96<br>. 97<br>. 98<br>. 99                              |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16                 | Symmetric Multiprocessor SMC Organization  Prescheduling: Data Distribution for 2-CPU System  Cyclic Static Scheduling: Data Distribution for a 2-CPU System.  Five Ordering Policies  Vector Layout in Memory  Distribution of 10,000-Element Vector for 8 Banks  Blocked Distribution of 80,000 Elements for 8 Banks and 8 CPUs  Blocked daxpy Performance for 2 CPUs  Blocked daxpy Performance for 4 CPUs  Blocked daxpy Performance for 8 CPUs  Blocked daxpy Performance for 2 Data Alignments  Blocked daxpy Performance for 8 CPUs and 80,000-Element Vectors  Cyclic daxpy Performance for 2 CPUs  Cyclic daxpy Performance for 4 CPUs  Cyclic daxpy Performance for 8 CPUs | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 95<br>. 96<br>. 97<br>. 98<br>. 99<br>100<br>101                |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16<br>4.17         | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92<br>. 95<br>. 96<br>. 97<br>. 98<br>. 99<br>100<br>101<br>102 |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16<br>4.17         | Symmetric Multiprocessor SMC Organization  Prescheduling: Data Distribution for 2-CPU System  Cyclic Static Scheduling: Data Distribution for a 2-CPU System.  Five Ordering Policies  Vector Layout in Memory  Distribution of 10,000-Element Vector for 8 Banks  Blocked Distribution of 80,000 Elements for 8 Banks and 8 CPUs  Blocked daxpy Performance for 2 CPUs  Blocked daxpy Performance for 4 CPUs  Blocked daxpy Performance for 8 CPUs  Blocked daxpy Performance for 2 Data Alignments  Blocked daxpy Performance for 8 CPUs and 80,000-Element Vectors  Cyclic daxpy Performance for 2 CPUs  Cyclic daxpy Performance for 4 CPUs  Cyclic daxpy Performance for 8 CPUs | . 76<br>. 78<br>. 79<br>. 89<br>. 90<br>. 91<br>. 92<br>. 95<br>. 96<br>. 97<br>. 98<br>. 99<br>100<br>101<br>102 |

|   | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16<br>4.17<br>4.18 | Symmetric Multiprocessor SMC Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 76<br>. 78<br>. 79<br>. 89<br>. 91<br>. 95<br>. 95<br>. 96<br>. 97<br>. 98<br>99<br>100<br>101<br>102<br>103    |

List of Figures xv

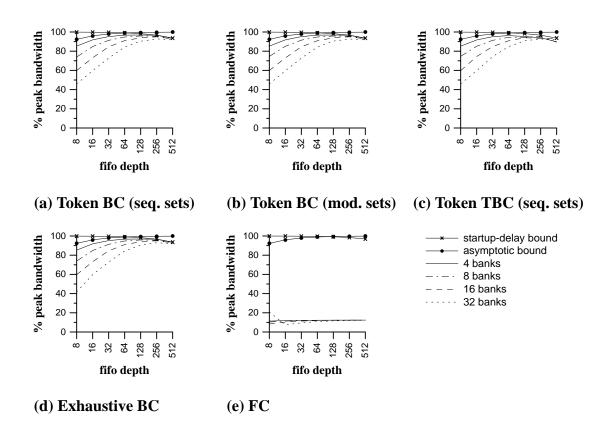

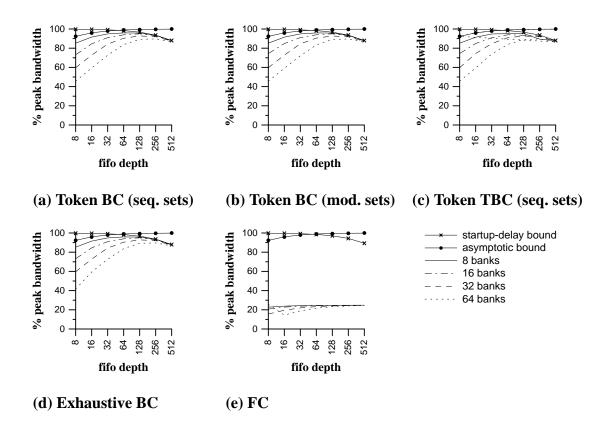

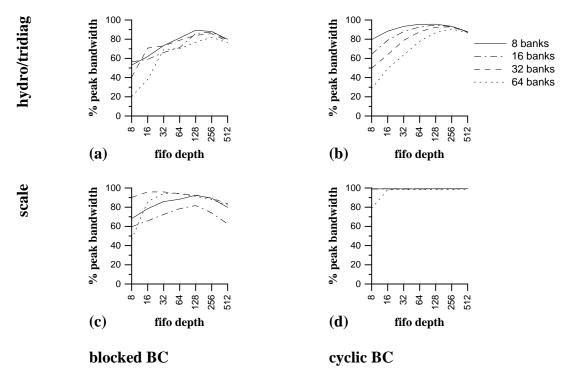

|   | 4.21 | hydro/tridiag Performance for 80,000-Element Vectors and 8 CPUs. 1 | .08 |

|---|------|--------------------------------------------------------------------|-----|

|   | 4.22 | Blocked BC Performance for <i>scale</i>                            | .09 |

|   | 4.23 | Blocked FC Performance for 8 CPUs and 10,000-Element Vectors 1     | .11 |

| 5 | Spa  | rse Matrix Computations 1                                          | 15  |

|   | 5.1  | Chapter Structure                                                  | 15  |

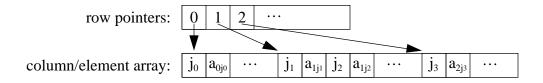

|   | 5.2  | Sparse Matrix Data Structure                                       | .19 |

|   | 5.3  | Sample Computation with Stream and Scalar Accesses                 | 20  |

|   | 5.4  | Inner Loop of Sparse <i>jacobi</i> Kernel                          | 23  |

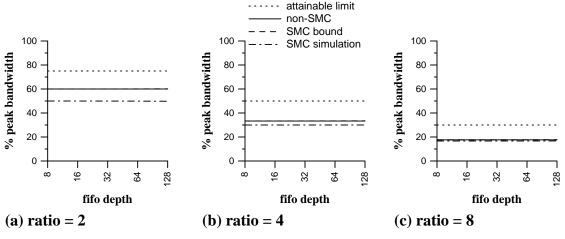

|   | 5.5  | 5000-Element Sparse Matrix Performance                             | 24  |

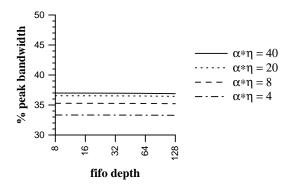

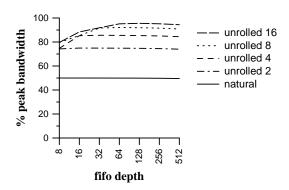

|   | 5.6  | Effects of Loop Unrolling on Sparse-Matrix Performance             |     |

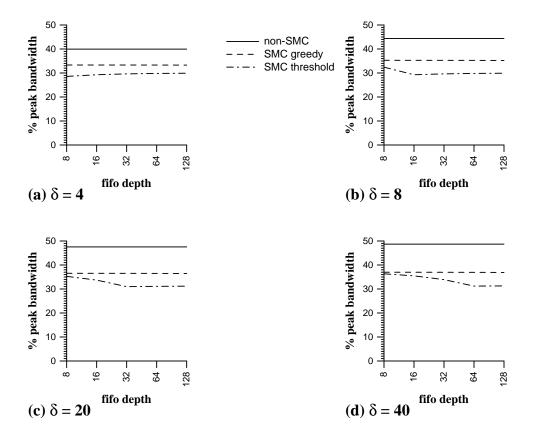

|   | 5.7  | SMC Performance for 5000 Elements and a Miss/Hit Cost Ratio of 4 1 | 127 |

|   | 5.8  | SMC Performance for 5000 Elements and a Miss/Hit Cost Ratio of 8 1 | 128 |

| 6 | The  | SMC Hardware 1                                                     | 31  |

|   | 6.1  | Chapter Structure                                                  | 32  |

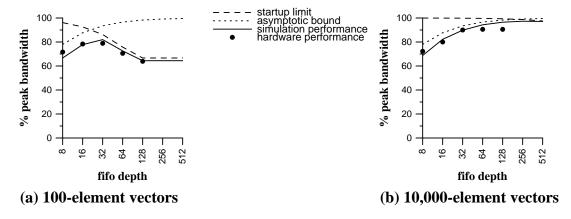

|   | 6.2  | SMC Performance for the <i>vaxpy</i> Benchmark                     | 33  |

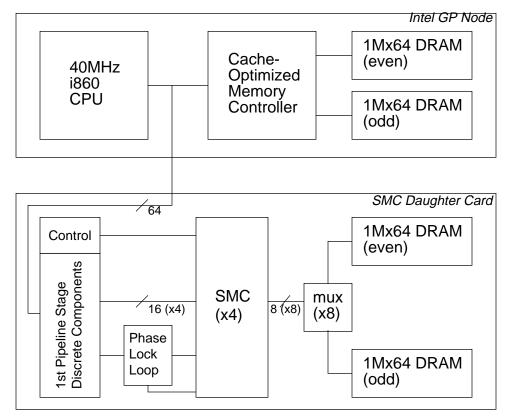

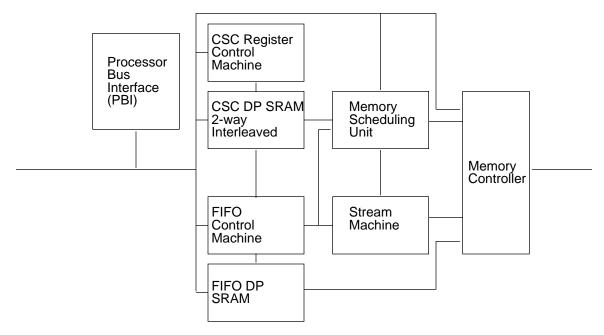

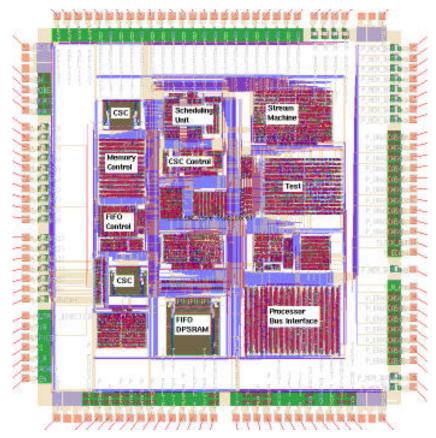

|   | 6.3  | SMC System Architecture                                            | 34  |

|   | 6.4  | SMC ASIC Architecture                                              |     |

|   | 6.5  | SMC Chip                                                           | 36  |

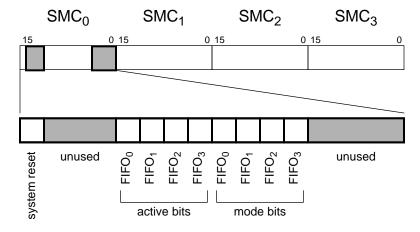

|   | 6.6  | Status Register Composition                                        | 37  |

|   | 6.7  | Memory Mapping of CSC Registers                                    | 37  |

|   | 6.8  | CSC Register Composition for Each FIFO                             | 38  |

|   | 6.9  | Memory Mapping of FIFO Heads                                       | .38 |

| 7 | Con  | npiling for Dynamic Access Ordering                                | 39  |

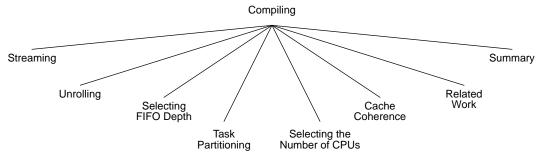

|   | 7.1  | Chapter Structure                                                  | 39  |

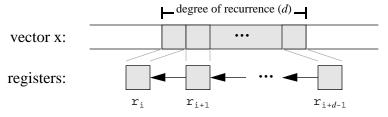

|   | 7.2  | Pipelining Recurrence Values through Registers                     | 41  |

|   | 7.3  | Example Recurrence Relation — Tridiagonal Elimination 1            | 41  |

|   | 7.4  | daxpy Performance for an Off-Chip SMC                              | 46  |

|   | 7.5  | Optimal FIFO Depth versus Best Simulation Performance for daxpy 1  | .49 |

| 8 | Oth  | er Systems Issues 1                                                | 55  |

|   | 8.1  | Chapter Structure                                                  | 55  |

### List of Symbols

- α a memory address

- $\delta$  the number of elements in a sparse-matrix data structure needed to represent one element of the original matrix

- η the number of non-stream accesses in a loop

- μ the depth of loop unrolling

- $\sigma$  the vector stride, or distance between consecutive elements (unit-stride means that successive elements are contiguous in memory)

- $a_{ij}$  an array element at row i and column j

- b the number of interleaved memory banks

- f the FIFO depth, in vector elements

- M the number of CPUs participating in a computation

- N the number of CPUs in the system

- *n* the dimension of matrix or length of vector

- s the total number of streams in a computation

- $s_r$  the number of read-streams

- $s_w$  the number of write-streams

- $t_{cr}$  the cost of reads that hit in the cache, in processor cycles

- $t_{cw}$  the cost of writes that hit in the cache, in processor cycles

List of Symbols xvii

- $t_{pm}$  the DRAM page-miss cost, in processor cycles

- $t_{ph}$  the DRAM page-hit cost, in processor cycles

- w the width of the memory system, or the amount of data transferred on each access

- $z_b$  the number of vector elements in a data block (submatrix) to be loaded

- $z_l$  the number of vector elements that fit in a cache line

- $z_p$  the number of data elements in a DRAM page

"Be not astonished at new ideas; for it is well known to you that a thing does not therefore cease to be true because it is not accepted by many."

— Benedict [Baruch] Spinoza (1632-1677)

### Chapter 1

### Introduction

This dissertation proposes and analyzes a method for designing a computer memory subsystem to maximize memory performance, overcoming a problem not addressed by traditional techniques. For applications involving long series of references to sequentially addressed memory locations (such as scientific computations involving long vector operands), our results demonstrate improvements in memory performance by factors of 2 to 23. Furthermore, the technique is practical to implement, exploiting existing compiler technology and requiring only a modest amount of special-purpose hardware.

#### 1.1 Memory Hierarchy

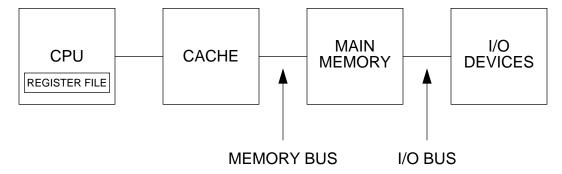

Figure 1.1 depicts the simplified *memory hierarchy* of a typical computer system. This organization is guided by two design principles: first, smaller memories positioned closer to the CPU can be made to run faster than larger components that are farther away; second, data that has been accessed recently is likely to be used again in the near future, a property referred to as *temporal locality of reference*. The data needed by the processor during a particular interval of the program's execution constitutes its *working set*. In order to

improve overall performance, compilers and architectures attempt to keep a program's working set of data in the smaller, faster levels of the memory hierarchy.

Figure 1.1 Typical Memory Hierarchy

This work focuses on the first three levels of the hierarchy: *registers*, *cache*, and *main memory*. Registers are small, fast storage buffers within the CPU. The compiler is responsible for managing their use, deciding which values should be kept in the available registers at each point in the program. *Register pressure* occurs when the computation's demand for registers exceeds the CPU's supply.

A cache is a small, fast memory located close to the CPU. Whenever the CPU issues a memory reference, the cache checks to see if it contains the appropriate value. A *cache hit* occurs when the value is found in cache. A *cache miss* occurs when the value is not in cache and must be fetched from main memory. Caches typically exploit the principle of *spatial locality of reference* by fetching a fixed amount of data contiguous to the referenced value. The assumption is that whenever a memory location is referenced, it is likely that nearby locations will also be referenced in the near future. Caches can vary widely in their size and organization, and there may be more than one level of cache in the hierarchy. These details are not important to our discussion; we do not address them further.

<sup>1.</sup> We use this term in a more informal sense than its original definition, which refers to virtual memory pages [Den68].

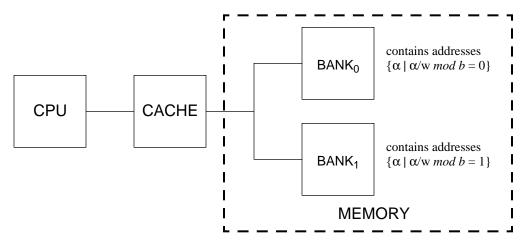

The next level of the hierarchy is main memory, which can be organized in a variety of ways. The important parameters for our discussion are width, bandwidth, interleaving, and latency. Width refers to the amount of data that is transferred on each access; for simplicity, we assume this width, w bytes, is equal to the size of the data items directly manipulated by the CPU. Memory chips can be arranged in banks so that accesses to different banks can be overlapped in time, thereby increasing the memory system throughput, or bandwidth. One common organization is an interleaved (byte-addressable) memory system of b banks, in which a physical memory address  $\alpha$  maps to bank ( $\alpha/w$ ) modulo b). b is sometimes referred to as the interleaving factor. Figure 1.2 depicts a system with two interleaved banks. For simplicity, we assume that memory is interleaved according to the width of the memory system. Latency describes the amount of time between the initiation and completion of an event, in this case a memory access.

Figure 1.2 Interleaved Memory System

Bandwidth and latency are important measures of memory system performance. We distinguish between the *peak bandwidth* of a system, or the maximum possible throughput of the main memory, and the *effective bandwidth* of a computation, or the amount of the system's peak bandwidth that the application exploits. In addition, we will occasionally refer to *attainable bandwidth*, or the bounds on effective bandwidth imposed by a given application.

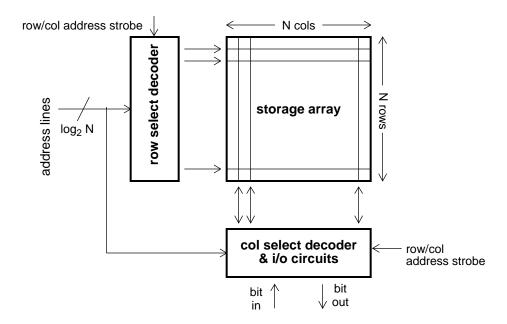

The banks of the memory systems we consider are composed of *Dynamic Random Access Memory* (DRAM) devices. Each packaged DRAM chip contains an array of memory cells, and current chips have capacities of up to 64Mbits. The cells store data as charge on capacitors: the presence or absence of charge in a capacitor is interpreted as a binary 1 or 0. This storage medium is termed *dynamic* because the charges must be refreshed periodically to compensate for the capacitors' natural tendency to discharge. The storage arrays are typically square, and each cell is connected to a row line and a column line. With this  $2^{1/2}D$  organization, the bits of a particular word are spread across multiple chips. To select a bit, the word address is split into two parts: row and column. The row address is transmitted first, followed by the column address. Figure 1.3 (adapted from [Sta90]) depicts a  $2^{1/2}D$ , one-bit-per-chip memory organization.

Figure 1.3 DRAM Organization

The DRAM *access time* is the latency between when a read request is initiated and when the data is available on the memory bus, whereas *cycle time* is the minimum time between completion of successive requests. For *sustained accesses* — series of accesses performed in succession — cycle time becomes the limiting performance factor.

The term DRAM is slightly misleading: it was coined to indicate that accesses to any "random" location require about the same amount of time, but most modern devices provide special capabilities that make it possible to perform some access sequences faster than others. For instance, nearly all current DRAMs implement a form of *fast-page mode* operation [Qui91].

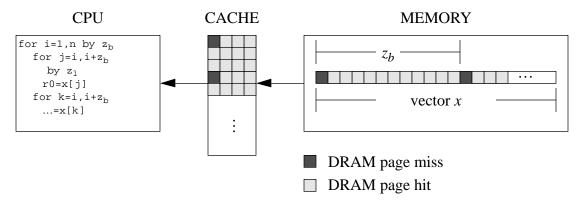

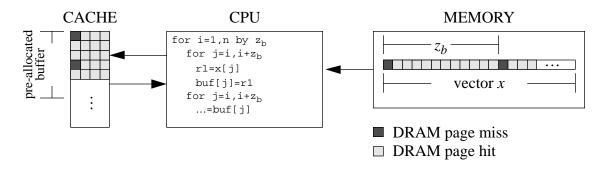

Fast-page mode devices behave *as if* implemented with a single, on-chip cache line, or *page*. A memory access falling outside the address range of the current page forces a new one to be set up, a process that is significantly slower than repeating an access to the current page. In fact, the pages are just the rows of the storage array. Fast-page mode takes advantage of the fact that although a certain amount of time is needed to precharge the selected page (row) before any particular column can be accessed, the page remains charged long enough for many other columns to be accessed, as well. Both the row and column addresses must be transmitted for the initial access (*page-miss*), but only the column addresses are sent for the subsequent accesses (*page-hits*). DRAM pages should not be confused with virtual memory pages. Throughout this dissertation the term "page" will be used to refer to a DRAM page, unless explicitly stated otherwise.

Other common devices offer similar features (nibble-mode, static column mode, or a small amount of SRAM cache on chip) or exhibit novel organizations (such as Rambus [Ram92], Ramlink, and the new synchronous DRAM designs [IEE92]). The details of their implementation are not important here; it suffices to note that the order of requests strongly affects the performance of all these memory devices.

For interleaved memory systems, the order of requests is important on another level: accesses to different banks can be performed faster than successive accesses to the same bank.

#### 1.2 The Memory Bandwidth Problem

It has become painfully obvious that processor speeds are increasing much faster than memory speeds. While microprocessor performance has improved steadily at a rate of 50-100% per year over the past decade, DRAM performance has increased at an annual rate of less than 10% [Hen90]. This disparity has caused memory to become the performance bottleneck for many applications. For example, a 300 MHz DEC Alpha can perform more than 20 instructions in the time required to complete a single memory access to a 40ns DRAM. Not only is the current problem serious, but it is growing at an exponential rate.

This dissertation addresses the memory bandwidth problem for an important class of applications: those whose inner loops linearly traverse streams of vector-like data, i.e. structured data having a known, fixed displacement between successive elements. Because they execute sustained accesses, these *streamed computations* are limited more by bandwidth than by latency. Examples of these kinds of programs include vector (scientific) computations, multi-media compression and decompression, encryption, signal processing, image processing, text searching, some database queries, some graphics applications, and DNA sequence matching. We will often couch our discussion in terms of scientific computation, but our results are applicable to a much wider class of applications.

#### 1.3 Motivation

Caching has often been used to bridge the gap between microprocessor and DRAM performance, but as the bandwidth problem grows, the effectiveness of the technique is rapidly diminishing [Bur95,Wul95]. Even if the addition of cache memory is a sufficient solution for general-purpose scalar computing (and even some *portions* of vector-oriented computations) its general effectiveness for vector processing is questionable. The vectors used in streamed computations are normally too large to cache, and each element is visited only once during lengthy portions of the computation. This lack of temporal locality of reference makes caching less effective than it might be for other parts of the program.

In addition to traditional caching, other proposed solutions to the memory bandwidth problem range from software prefetching [Cal91,Kla91,Mow92] and iteration space tiling [Car89,Gal87,Gan87,Lam91,Por89,Wol89], to prefetching or non-blocking caches [Bae91,Che92,Soh91], unusual memory systems [Bud71,Gao93,Rau91,Val92, Yan92], and address transformations [Har87,Har89]. The following chapters discuss the merits and limitations of each of these in the context of streaming, but all these solutions overlook one simple fact: they presume that memory components require about the same time to access any random location. As noted above, this assumption no longer applies.

Vector computers deliver high performance for numerical problems that can be vectorized. These architectures achieve their performance through heavy pipelining: they support streaming data through a single pipeline, and allow multiple pipelines to operate concurrently on independent streams of data [Sto93]. Vector processors range from auxiliary processors attached to microcomputers to expensive, high-speed supercomputers. The latter class of machines feature special, high-speed memory systems (usually composed of *Static RAMs*, which are not as dense as DRAMs, but are generally faster and don't require data-refresh cycles). These memory systems often include sophisticated circuitry to avoid bank conflicts when loading vector registers.

Although the solution we propose here is described in terms of general-purpose, microprocessor-based systems, it is equally applicable to vector computers: the SMC can be used to maximize memory performance when loading or storing vector operands. It provides the same functionality as the conflict-avoidance hardware (and works well for combinations of vector strides that often hinder the latter hardware), in addition to taking advantage of memory component features (for those devices that have non-uniform access times), prefetching read operands, and buffering writes. Furthermore, the SMC can achieve vector-like memory performance for streamed computations with recurrences that prevent vectorization.

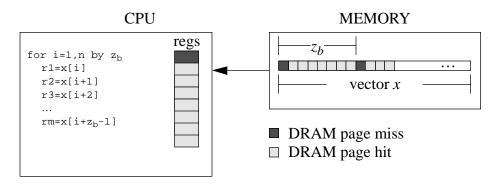

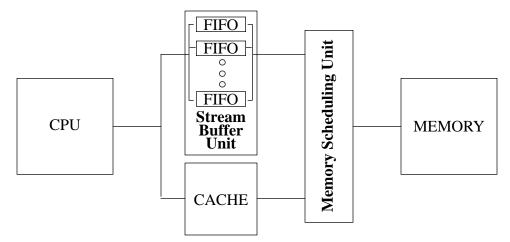

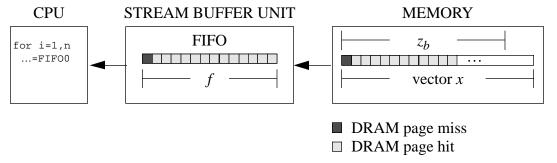

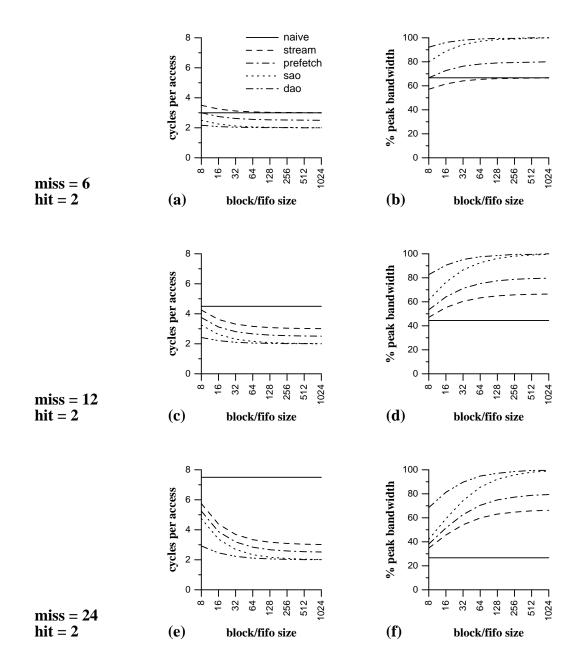

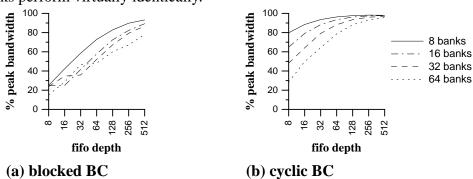

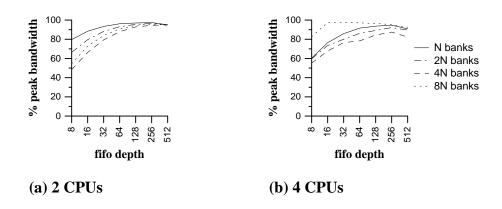

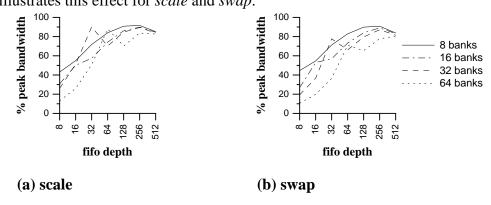

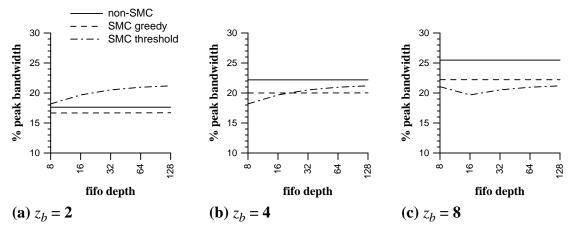

#### 1.4 Organization of the Thesis