# WAWA Final Report: ROMULUS I

| I. STATEMENT OF WORK                                                                                                      |     | I-A             | August E       | Bresnaider                                                  | 1      |

|---------------------------------------------------------------------------------------------------------------------------|-----|-----------------|----------------|-------------------------------------------------------------|--------|

| A. August Bresnaider                                                                                                      |     | I-B             |                | g Ploch                                                     | 1      |

| Lead software design. Directed instruction set architecture                                                               |     | I-C<br>I-D      |                | iicci                                                       | 1<br>1 |

| and finite state machine design. Proved Turing completeness of architecture. Helped design PCBs and pick parts to use.    |     |                 |                |                                                             | 1      |

| Played role in debugging and determining the capabilities of                                                              | II  | Table o         | f Content      | s                                                           | 1      |

| the hardware through testing. Designed simulator, assembler and compiler, and wrote code to specify FSM and ALU flash,    | III | Backgr          | ound           |                                                             | 3      |

| as well as Arduino code to flash the chips.                                                                               | IV  | Project         | _              | on - Specifications                                         | 3      |

| B. Wolfgang Ploch                                                                                                         |     | IV-A            |                | on Set Architecture                                         | 3      |

| Lead hardware design. Participated in instruction set archi-                                                              |     |                 | IV-A1          | Overview                                                    | 3      |

| tecture design and high level architecture design. Designed cir-                                                          |     |                 | IV-A2          | Move Instructions (Opcodes 0-3)                             | 4      |

| cuitry, designed PCB, and wrote hardware description sections                                                             |     |                 | IV-A3          | Bitwise Instructions (Op-                                   | •      |

| for boards 1, 2, 3, 5, and 6. Assisted in circuitry design for                                                            |     |                 |                | codes 4-7)                                                  | 4      |

| board 4. Soldered components on all 6 boards. Lead case and control panel design. Assembled entire device. Troubleshot    |     |                 | IV-A4          | Arithmetic / Logical Instruc-                               |        |

| hardware and implemented hardware solutions during testing.                                                               |     |                 | TX 1           | tions (Opcodes 8-B)                                         | 4      |

| Designed and provided teletype peripheral and wrote driver                                                                |     |                 | IV-A5          | Control Flow Instructions (Opcodes C-F)                     | 1      |

| programs for it. Wrote cost and physical constraint sections of the final report.                                         |     | IV-B            | Finite Sta     | ate Machine                                                 | 4<br>5 |

| C. Will Rimicci                                                                                                           | V   | Project         | Descripti      | on - Software                                               | 7      |

|                                                                                                                           |     | V-A             | Assemble       | er ("romASM")                                               | 7      |

| Participated in instruction set architecture design and high level architecture design. Designed circuitry, designed PCB, | X7T | D               | D              |                                                             | 7      |

| and wrote hardware description section for board 4. Wrote                                                                 | VI  | Project<br>VI-A | Board 1        | on - Hardware                                               | 7<br>7 |

| code to generate control signals FSM flash data. Rigorously                                                               |     | V 1-A           | VI-A1          | Overview                                                    | 7      |

| tested machine code simulator and assembler. Wrote several                                                                |     |                 | VI-A2          | LED Displays                                                | 7      |

| test programs to be run on simulator and computer. Trou-                                                                  |     |                 | VI-A3          | Register Design                                             | 7      |

| bleshot hardware and helped design hardware solutions during                                                              |     |                 | VI-A4          | Addressing the Registers                                    | 7      |

| testing. Recorded tests for debugging purposes. Designed                                                                  |     |                 | VI-A5          | Modifications                                               | 7      |

| circuitry, designed PCB, and soldered general input/output peripheral. Wrote background, societal impact, intellectual    |     | VI-B            | Board 2        |                                                             | 7      |

| property, full system test, and final results sections of the final                                                       |     |                 | VI-B1          | Overview                                                    | 7      |

| report. Helped keep team focused on deliverables when due                                                                 |     |                 | VI-B2          | Clock Signals                                               | 8      |

| over the course of the semester.                                                                                          |     |                 | VI-B3          | Pause Handling                                              | 12     |

|                                                                                                                           |     |                 | VI-B4          | Reset Timing                                                | 12     |

| D. Austin Chappell                                                                                                        |     |                 | VI-B5          | Timing Signals and Counters                                 | 12     |

| Assisted in the creation of ISA, software tools, and testing                                                              |     |                 | VI-B6          | Interrupt Handling Correction<br>Finite State Machine Flash | 13     |

| processes. Wrote the comprehensive test program for the                                                                   |     |                 | VI-B7          | Chip Lookup Table                                           | 15     |

| whole project. Ensured timely and quality completion of                                                                   |     | VI-C            | Board 3        |                                                             | 17     |

| project deliverables. Wrote standards, timeline, insights, and                                                            |     | VI-C            | VI-C1          | Overview                                                    | 17     |

| compiled references in this report. Helped keep team focused                                                              |     |                 | VI-C2          | Memory Address Register                                     | .,     |

| on deliverables when due over the course of the semester.                                                                 |     |                 | . = <b>. =</b> | (MAR)                                                       | 17     |

| II. TABLE OF CONTENTS                                                                                                     |     |                 | VI-C3          | Address Decoding                                            | 17     |

| CONTENTS                                                                                                                  |     |                 | VI-C4          | Mapped IO Port                                              | 17     |

|                                                                                                                           |     |                 |                |                                                             |        |

1

Statement of Work

VI-C5

Mapped IO Port Control Sig-

nal Logic . . . . . . . . . . . . . 17

39

|      |           | V1-C6              | Memory SRAM and Sup-                                |          | AVII | Appe |

|------|-----------|--------------------|-----------------------------------------------------|----------|------|------|

|      |           |                    | porting Circuitry                                   | 18       |      |      |

|      | VI-D      | Board 4            |                                                     | 18       |      |      |

|      |           | VI-D1              | Arithmetic and Logic Unit                           | 10       |      |      |

|      |           | VI-D2              | (ALU)                                               | 18<br>19 |      |      |

|      |           | VI-D2<br>VI-D3     | Compare Logic                                       | 21       |      |      |

|      |           | VI-D4              | 7-Segment Hex Displays                              | 21       |      |      |

|      | VI-E      | Board 5            | · · · · · · · · · · · · · · · · · · ·               | 21       |      |      |

|      |           | VI-E1              | Overview                                            | 21       |      |      |

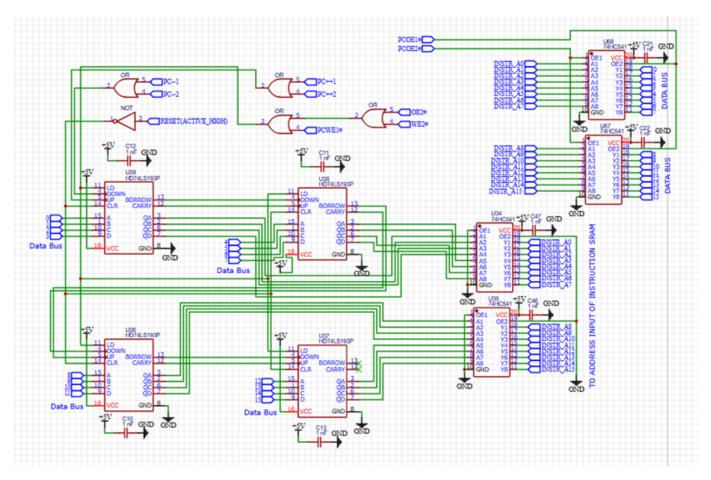

|      |           | VI-E2              | Program Counter                                     | 21       |      |      |

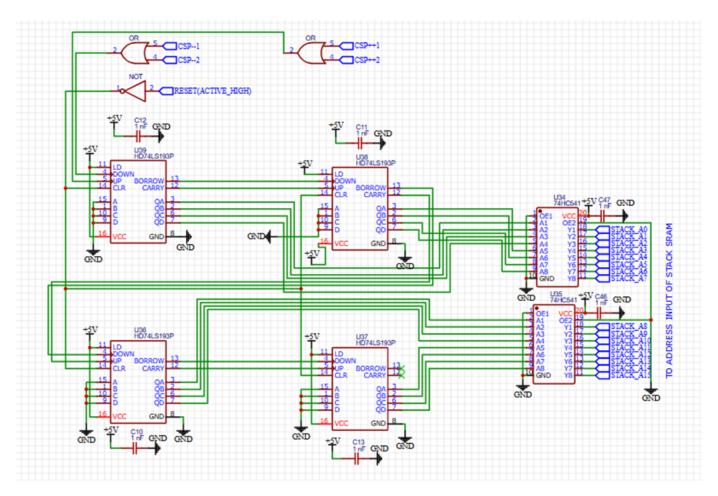

|      |           | VI-E3              | Stack Pointer Counter                               | 24       |      |      |

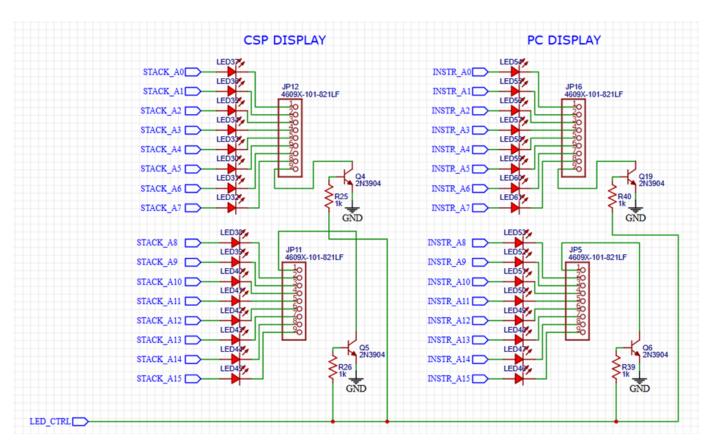

|      |           | VI-E4              | Program Counter and Stack                           |          |      |      |

|      |           |                    | Pointer Counter LED Displays                        | 24       |      |      |

|      |           | VI-E5              | Dip-switches for Interrupt                          |          |      |      |

|      |           |                    | Jump Location                                       | 24       |      |      |

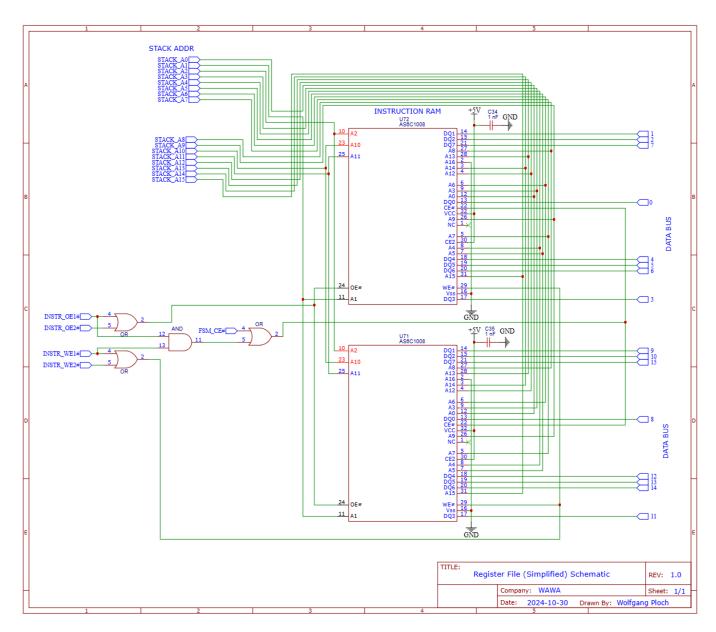

|      |           | VI-E6              | Instruction SRAM                                    | 25       |      |      |

|      |           | VI-E7              | Stack SRAM                                          | 25       |      |      |

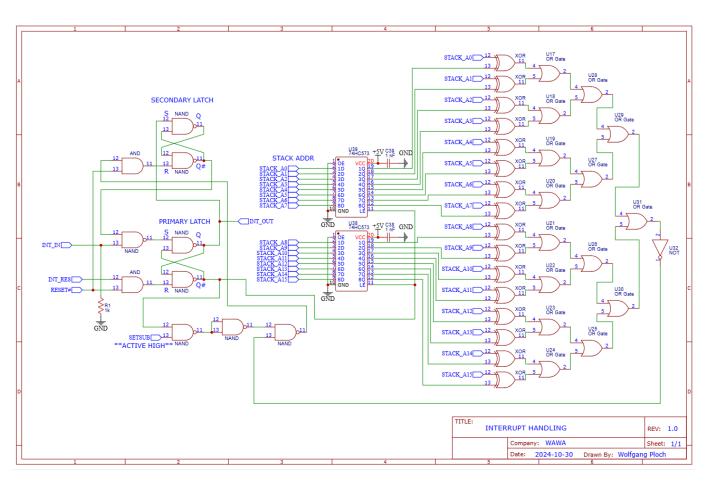

|      |           | VI-E8              | Interrupt Handling                                  | 26       |      |      |

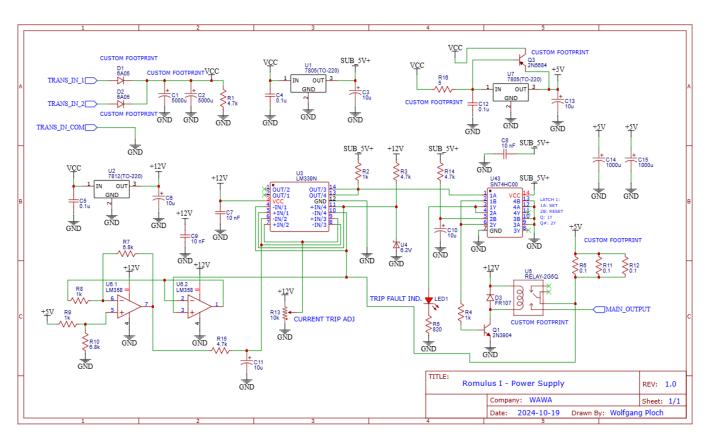

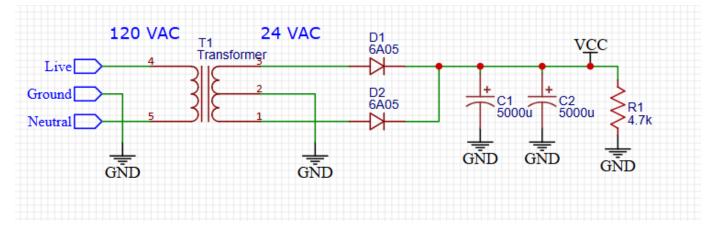

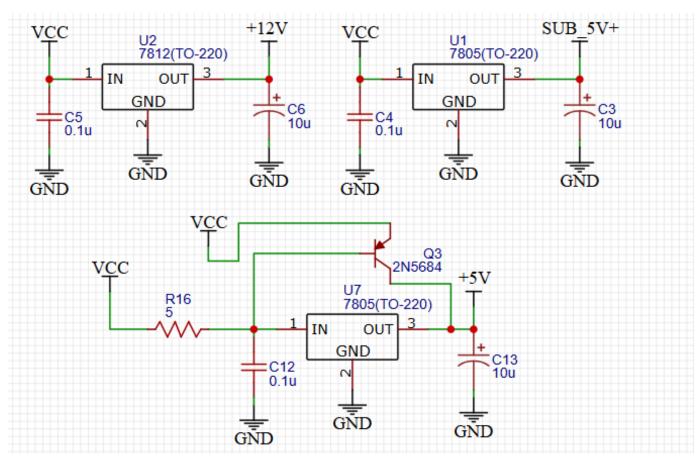

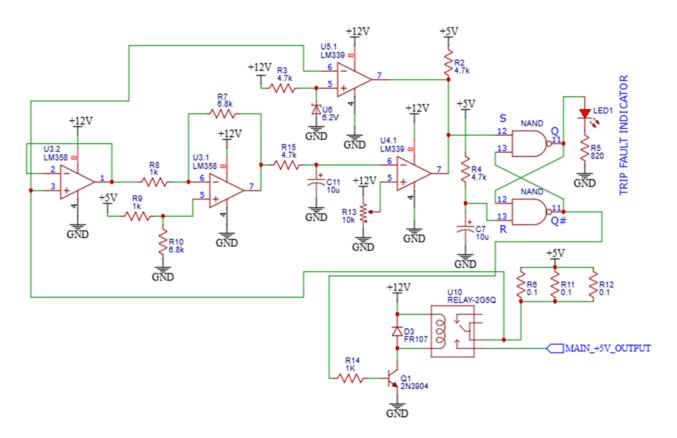

|      | VI-F      | Board 6            |                                                     | 26       |      |      |

|      |           | VI-F1              | Overview                                            | 26       |      |      |

|      |           | VI-F2<br>VI-F3     | Power Regulation Design Over Current and Over Volt- | 27       |      |      |

|      |           | V1-F3              |                                                     | 27       |      |      |

|      |           |                    | age Protection                                      | 21       |      |      |

| VII  | Test Pla  | ın                 |                                                     | 28       |      |      |

| VIII | Physical  | l Constraiı        | nts                                                 | 36       |      |      |

|      | VIII-A    |                    | d Manufacturing Constraints .                       | 36       |      |      |

|      | VIII-B    | Tools Use          | d in the Project                                    | 36       |      |      |

|      |           | VIII-B1            | Visual Studio 2022                                  | 36       |      |      |

|      |           | VIII-B2            | Digital                                             | 36       |      |      |

|      |           | VIII-B3            | Multisim                                            | 36       |      |      |

|      |           | VIII-B4            | ANTLR                                               | 36       |      |      |

|      |           | VIII-B5            | Arduino IDE and Arduino                             | 26       |      |      |

|      |           | VIII-B6            | Mega                                                | 36<br>36 |      |      |

|      |           | VIII-B0<br>VIII-B7 | Notepad                                             | 36       |      |      |

|      | VIII-C    |                    | straints                                            | 36       |      |      |

|      | VIII-D    |                    | a Production Version                                | 36       |      |      |

| IX   |           | Impact             |                                                     | 36       |      |      |

| X    |           | l Standard         | lo                                                  | 37       |      |      |

|      |           |                    |                                                     |          |      |      |

| XI   | Intellect | tual Prope         | rty Issues                                          | 37       |      |      |

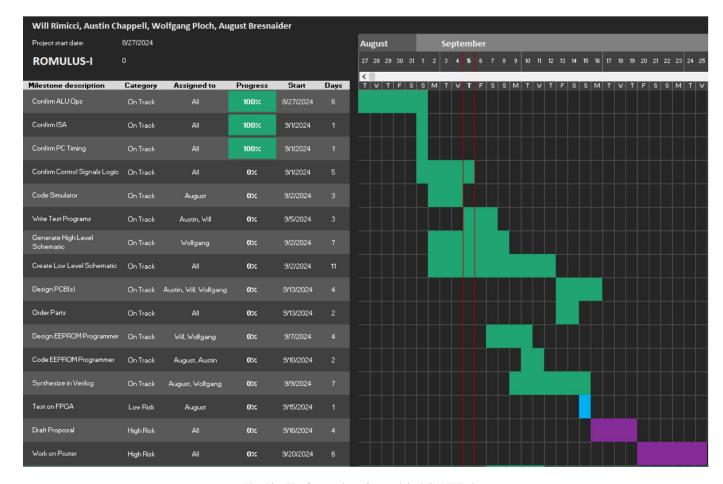

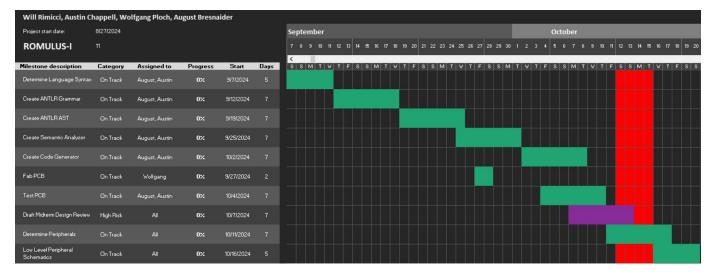

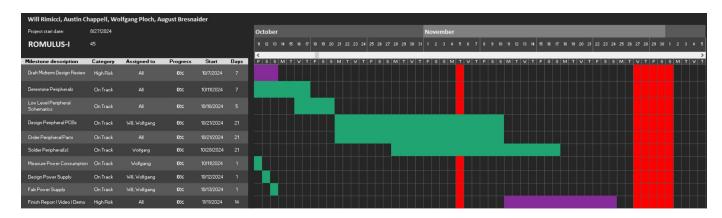

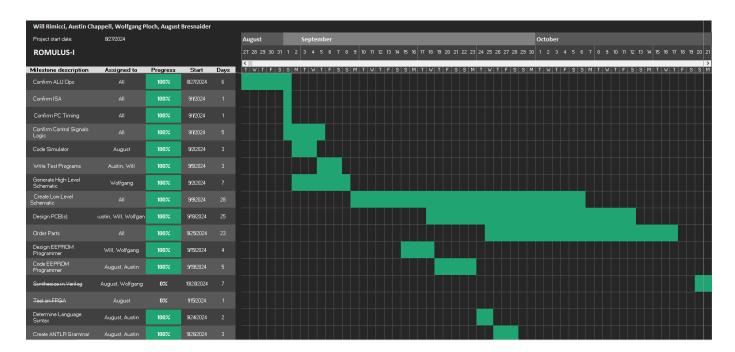

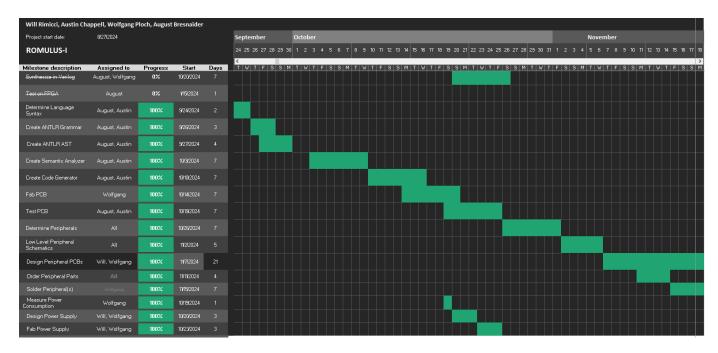

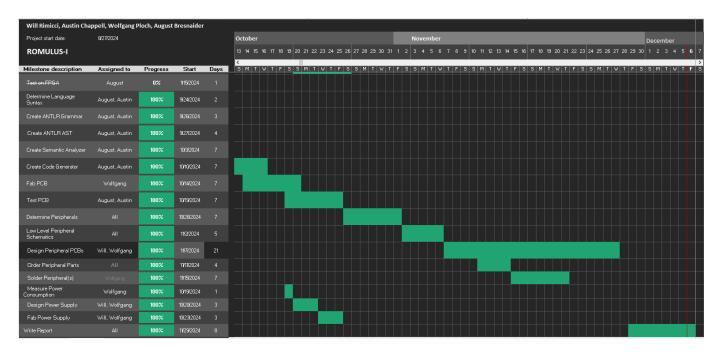

| XII  | Timelin   | e                  |                                                     | 37       |      |      |

| XIII | Costs     |                    |                                                     | 38       |      |      |

| XIV  | Final R   | esult              |                                                     | 38       |      |      |

| XV   | Enginee   | ering Insig        | ht                                                  | 38       |      |      |

| XVI  | Future    | Work               |                                                     | 39       |      |      |

|      |           | *****              |                                                     |          |      |      |

Abstract—Our project revolves around the design and fabrication of a 16-bit CPU and supporting memory using Flash memory, 74XX series logic chips, and passive components. Aimed to be a educational device for students to learn computer architecture, digital logic, machine code, and electronics, the Romulus I is equipped with LEDs on the internal registers, 7-segment displays, debugging tools, and multiple clock speeds. The scope of this project also includes a compiled language and an assembler providing increasing layers of abstraction, allowing for either a top-down or bottom-up approach to teaching about computing systems and organization.

## III. BACKGROUND

We chose this project for a number of reasons. First, we were inspired by our experiences in other classes like Computer Systems and Organization and Digital Logic Design. After using the Digital open-source logic simulator [1] and the ToyISA simulator [2], both of which are virtual tools, we felt that we could create a physical, hands-on teaching tool that would help students understand computers in a new way. Second, we wanted to see if we could use what we had learned in those classes through lectures and homeworks to make something new. Finally, we just thought it would be a fun and interesting challenge.

Throughout this project, we used many techniques we learned in our classes. The general structure of the computer, having a control signals FSM, an ALU, a program counter, and memory, was material from Digital Logic Design. In that class, we created a programmable computer with those blocks in Digital [1] (though most of the designs of the blocks themselves were different from the approach we were taught in that class). The design of the instruction set architecture and assembly were from Computer Systems and Organization 1. The knowledge on how to create an assembler and compiler were from Computer Systems and Organization 2. Finally, the knowledge on how to create a PCB layout, order parts, and solder circuits were from the ECE Fundamentals series.

Though this project was based on and inspired by a number of past works, it is a new and distinct product. As mentioned above, we took inspiration from the virtual tools we used in our classes, like Digital [1] and ToyISA [2]. While these are fantastic tools for learning, they are only virtual programs, and do not provide a physical, interactable model from which to learn. Another similar past work is Ben Eater's 8-bit breadboard computer [3]. In his video series, Ben Eater creates a full-functional, programmable 8-bit computer on a set of breadboards using only simple logic gates. It has a clock, registers, ALU, RAM, program counter, and control logic. While this project is similar to our own, it is built on a set of breadboards, meaning the circuits are not as permanent as ours made from soldered PCBs, and it is much less versatile than ours: it is only eight bits and there are only two general purpose registers, compared to our 16 bits and 16 general purpose registers. Our work is different from any projects before it.

#### IV. PROJECT DESCRIPTION - SPECIFICATIONS

## A. Instruction Set Architecture

1) Overview: The instruction set architecture (or ISA, for short) acts as a specification that defines the operations the CPU is capable of, as well as their binary representations. By giving an operation a mapping, we include it in the capabilities of the CPU. Designing an ISA is a balancing act: If an ISA is too simple, common operations can become arduous (i.e., not including A & B requires the programmer to do  $\overline{(A|B)}$  any time a bitwise AND is needed), or in the worst case, the CPU may not be Turing complete. On the contrary, if the ISA is overly complicated, it may require an overly complicated hardware implementation. To avoid the negative effects of these two poles, our ISA should be as follows:

## Turing complete

If our ISA is not Turing-complete, there is a strict and provable upper bound on the computational power of our hardware, which means our CPU will not be able to compute any given algorithm.

## • Logically comprehensive

While the bare minimum number of operations needed to make a Turing-complete ISA is remarkably small (by our count, it is roughly 5 or 6), it's to include more instructions for ease of use purposes, much like the bitwise AND example above, to avoid frustration and code repetition on the programmer's part.

#### • Easy to code / represent in hexadecimal

As one of the revisions to ToyISA that we aim to implement, the bitcode should be intuitive and require minimal bit-fiddling on the programmer's part. ToyISA had 8-bit instructions, with the most significant 4 bits representing opcode, the next 2 representing rA (parameter 1), and the least significant 2 representing rB (parameter 2) or an optional set of selector bits for unary operations. When programming using bitcode, it is often a hassle having to compute the lower hexadecimal digit when changing rA or rB, so our ISA should split each 16-bit value into groups of 4 or 8 wherever possible to avoid this.

#### • Able to be utilized in higher-level abstraction

The ISA should be fully functional when programming using bitcode, but there should also be instructions geared towards higher-level concepts. For example, while a stack pointer and instructions incrementing and decrementing the stack is not strictly required, it gives way to creating a call stack and allowing for the writing of functions, loops, and recursion: features only truly available in romASM and / or Hawk. The ISA we designed for Romulus I in order to solve these problems to the best of our ability is given by Table I.

As referenced in the table, we settled on using 16 instructions, which allows our opcode to fit within the most significant 4 bits of the instruction. Bits 8-11 generally act as placeholder for  $R_A$ , the first parameter in many operations. From there, bits 4-7 are reserved for  $R_B$ , the second parameter for many operations, and finally, bits 0-3 are usually reserved

for  $R_Y$ , the register in which to store the result. Each group of 4 instructions are similar to each other, and so the next 4 sections will discuss the "Move", "Bitwise", "Arithmetic / Logical", and "Control Flow" instruction groups.

- 2) Move Instructions (Opcodes 0-3): The first 4 opcodes deal with moving values into and between registers, as well as interacting with memory. Opcode 0 deals with registerregister moves, which we intentionally mapped as opcode 0, so that the bitcode "0000" refers to moving  $R_0 \rightarrow R_0$ , or essentially a NOP instruction. Thus, if the instruction RAM is initialized to all 0's, it will default to NOP instructions, instead of a random arithmetic or control flow operation. Instruction 1 moves an immediate value into a register, this being our only Itype instruction (as opposed to the 15 R-type instructions), in which the opcode and registers are in the first 16-bit value, and the second 16-bit value specifies the immediate value to load. We originally wanted to restrict the size of each instruction to 16 bits, and limit the size of immediates to 12 bits, but after discussion regarding the simplicity of multiaddress instructions within our control signals logic, as well as the fact that 12-bit immediates would limit our addressing space to 4096 addresses, we decided to go forward with a true immediate-type instruction. This instruction is the only way to load immediate values, a decision we made to keep the total number of instructions within 16 to fit into a 4-bit opcode. The next two instructions (2 and 3) involve interfacing with memory, or more specifically, our data RAM. If we were to simulate a Turing machine, these instructions would be akin to reading and writing from the tape.

- 3) Bitwise Instructions (Opcodes 4-7): The next four instructions represent the four most commonly used bitwise logical operations in programming. While NAND is expressively complete (meaning, every logic gate can be derived from repeated applications of NAND), the NAND is not often used in programming, and operations like OR and XOR would require lots of register moves and instructions if only NAND were available. By selecting AND, OR, NOT and XOR, we only leave out NAND, XNOR and NOR, all three of which are fairly uncommon, and can be computed with a maximum of two operations (and no register shifting) if needed.

- 4) Arithmetic / Logical Instructions (Opcodes 8-B): When designing our ISA, we knew that we would be using parallel flash memory to implement our ALU. While this provides its benefits, namely the smaller ALU footprint and the ability to reconfigure, the drawback of this is that, due to the small number of address pins in parallel flash, each bit of an arithmetic operation may only rely on the opcode, the bit above it, and the bit below it. This works for an operation like addition or subtraction, where the operation happens in a rippling fashion (that is, carry and borrow bits are always adjacent to the bit in question) but this does not work for an operation like multiplication, where each bit of parameter A needs bits from parameter B that are not necessarily adjacent. Thus, we decided for our main arithmetic / logical operations to be addition, subtraction, logical NOT, and a logical shift right. Addition and subtraction are obvious choices to include,

and we made a conscious decision to include both even though subtraction can be represented by an addition and a negation. This was another decision we made to improve the ease of use of our ISA. We the implemented logical NOT, which sets the least significant bit to 1 if the entire value is zero, and zero if the entire value is non-zero. While this may at first seem like a non-inline instruction, we planned to implement this instruction in a rippling fashion, where we begin with the most significant bit of the parameter, and use borrow-out inputs to signify if any of the numbers are non-zero. This ripples down to the least significant bit, which becomes zero if the borrow out is non-zero, and vice versa. Our last instruction of this section is a logical shift right, which again takes advantage of the borrow-out behavior to set subsequent bits. We discussed implementing an arithmetic right shift (i.e. sign-extending), but it is our belief that a generic operation that shifts the bits down is much more useful than one that acts on two's complement numbers. In order to abide by the in-lining rule though, it was necessary to require that right-shift only shifts 1 over. While we would have liked to implement a logical shift left, we decided that it would be strictly less valuable than any of the instructions currently in our ISA. Further, moving all digits to the left 1 place in binary is equivalent to multiplying that number by 2, or adding it to itself. Thus, using a little bit of creative bit-fiddling, the programmer can implement left-shift using addition if they so please. In fact, in our assembly, there is a left-shift instruction that takes advantage of this trick, abstracting this shortcoming away from the user.

5) Control Flow Instructions (Opcodes C-F): Instructions 12 and 13 are meant solely to interact with stack RAM. This stack can be utilized as a data structure, loading and storing values from registers, or to load and store values from the program counter, or in other words, jump program execution to another location. This is especially useful in higher levels of abstraction for calling and returning from functions, where a call can be represented as pushing the value to return to, and then unconditionally jumping to an arbitrary location, and a return can be represented as popping the value at the top of the stack into the program counter (or PC). It should be worth noting that this is why pushing PC actually pushes PC + 2, since a call takes 2 instructions, and the user would want to return to the next instruction after the call. In order to differentiate between pushing / popping with the PC or with registers, instructions 12 and 13 have an  $Op_2$  bit in bit 7, where setting it interacts with PC, and resetting it interacts with the register designated in  $R_A$  or  $R_Y$ , depending on the instruction. Instruction 14 handles unconditional jumps, which sets the value in PC to that of the defined register. This similar format is followed in instruction 15, where a jump is only initiated if a predicate is true, as specified by the flags in the lowest 4 bits of the instruction, and the mapping in Table II(note: X refers to don't-care bits; their values can be 1 or 0). Most assembly languages have something akin to jumping based on an arbitrary predicate (i.e. a ; b), amd while we would have liked to have a similar instruction, it was unable to make it within our 16 instructions.

TABLE I Instruction Set Architecture Mapping

| Opcode (Op) | Instruction             | Registers                                            |        | Bits      | (MSB LSB)     |           |

|-------------|-------------------------|------------------------------------------------------|--------|-----------|---------------|-----------|

| 0 (0000)    | Register to Register    | $R_A \to R_Y$                                        | Op (4) | $R_A$ (4) | X (4)         | $R_Y$ (4) |

| 1 (0001)    | Immediate to Register   | $I \rightarrow R_{Y}$                                | Op (4) |           | X (8)         | $R_Y$ (4) |

| 1 (0001)    | Illinediate to Register | $1 \rightarrow Ity$                                  |        | In        | nmediate (16) |           |

| 2 (0010)    | Register to Memory      | $R_A \to M_{RB}$                                     | Op (4) | $R_A$ (4) | $R_B$ (4)     | X (4)     |

| 3 (0011)    | Memory to Register      | $M_{RA} \rightarrow R_Y$                             | Op (4) | $R_A$ (4) | X (4)         | $R_Y$ (4) |

| 4 (0100)    | Bitwise OR              | $R_A - R_B \rightarrow R_Y$                          | Op (4) | $R_A$ (4) | $R_B$ (4)     | $R_Y$ (4) |

| 5 (0101)    | Bitwise NOT             | $\sim R_A \to R_Y$                                   | Op (4) | $R_A$ (4) | X (4)         | $R_Y$ (4) |

| 6 (0110)    | Bitwise AND             | $R_A$ && $R_B \rightarrow R_Y$                       | Op (4) | $R_A$ (4) | $R_B$ (4)     | $R_Y$ (4) |

| 7 (0111)    | Bitwise XOR             | $R_A \hat{R}_B \to R_Y$                              | Op (4) | $R_A$ (4) | $R_B$ (4)     | $R_Y$ (4) |

| 8 (1000)    | Add                     | $R_A + R_B \rightarrow R_Y$                          | Op (4) | $R_A$ (4) | $R_B$ (4)     | $R_Y$ (4) |

| 9 (1001)    | Subtract                | $R_A - R_B \rightarrow R_Y$                          | Op (4) | $R_A$ (4) | $R_B$ (4)     | $R_Y$ (4) |

| A (1010)    | Logical NOT             | $!R_A \rightarrow R_Y$                               | Op (4) | $R_A$ (4) | X (4)         | $R_Y$ (4) |

| B (1011)    | Logical Shift Right     | $R_A >> 1 \rightarrow R_Y$                           | Op (4) | $R_A$ (4) | X (4)         | $R_Y$ (4) |

| C (1100)    | Push                    | $(R_A \text{ or PC+2}) \rightarrow \text{Top stack}$ | Op (4) | $R_A$ (4) | Op2 (1)       | X (7)     |

| D (1101)    | Pop                     | Top stack $\rightarrow (R_Y \text{ or PC})$          | Op (4) | X (4)     | Op2 (1) X (3) | $R_Y$ (4) |

| E (1110)    | Unconditional Jump      | $R_A 	o PC$                                          | Op (4) | $R_A$ (4) | X (8)         |           |

| F (1111)    | Conditional Jump        | If $(R_B ?? 0): R_A \to PC$                          | Op (4) | $R_A$ (4) | $R_B$ (4)     | Flags (4) |

TABLE II CONDITIONAL JUMP FLAGS

| Flags | Comparison                           |

|-------|--------------------------------------|

| 0000  | N/A (Instruction functions as a NOP) |

| 0001  | $R_B == 0$                           |

| 001X  | $R_B := 0$                           |

| 01XX  | $R_B < 0$                            |

| 1XXX  | $R_B > 0$                            |

#### B. Finite State Machine

We implemented the control signals finite state machine as a flash chip lookup table because we though it would be easier and take up less board space than making it out of logic chips. We needed three flash chips because we have 24 FSM outputs, and each chip only had 8 data output bits.

A flowchart of the FSM is in figure 1.

Every instruction starts with a fetch step: Einstr activates, which allows the instruction in the instruction memory at the address of the current program counter onto the bus, and Cir activates, which takes the value off of the bus and puts it into the instruction register.

For opcode 0, register-to-register assignment, we first take the value from the chosen read register (Erx) and temporarily store it in the ALU (Cp0). We then take it from the ALU without operating on it (Ealu), then store it in the chosen write register (Crx, sel1). Crx opens the register file, and sel1 chooses which part of the instruction is being used as the address. Finally, we increment the PC to go to the next instruction (pcinc), and we reset the sub-instruction counter (setsub) to reset the FSM and start the next instruction.

For opcode 1, immediate-to-register assignment, after fetching, we just increment the PC (pcinc) and read the next value in instruction memory (Einstr) into the chosen register (Crx, sel1). Then, we increment the PC (pcinc) and reset the subcounter (setsub), same as before.

For opcode 2, register-to-memory assignment (storing), we first take the memory address from the register file (Erx, sel0)

and put it into the memory address register (Cmar). With the address set, we take the data from the desired register (Erx) and put it into memory (Cdata). Finally, we increment the PC and reset the subcounter (pcinc, setsub).

Opcode 3, memory-to-register assignment (loading), is similar to opcode 2. We take the memory address from the register file (Erx) and put it into the MAR (Cmar). Then, we take the data from memory (Edata) and put it into the correct register (Crx, sel1). Last, we poinc ans setsub as usual.

Opcodes 4 through B (11), the ALU opcodes, operate nearly identically. First, we load the data in the desired register (Erx) into the ALU's first parameter register (Cp0). If the operation being performed is binary, that is, it operates on two operands, then the second value is taken from its register (Erx, sel0) and put into the ALU's second parameter register (Cp1). (This step is skipped for unary operations, like both NOTs and shift right.) The ALU does the proper calculation according to the opcode, and the result is taken (Ealu) and placed into the desired output register (Crx, sel1). Finally, we poinc and setsub.

Opcode C (12), push, has two different cases: pushing a register value, and pushing the PC. Pushing a register is similar to register-to-memory assignment: We take the data from the desired register (Erx) and put it into the stack at the address given by the stack pointer (Cstack). We then increment the stack pointer (Csp++) and finish the instruction with a poinc and a setsub.

To push the PC to the stack, we actually push PC+2. This is because the only reason you would be pushing the PC to the stack is to call a function, and there needs to be room after pushing to jump to the function with a jump instruction before continuing the program. To do this, first we fetch, then we increment PC twice to make it PC+2 (pcinc x2). We then take the value from the PC (Epc) and write it to the stack (Cstack). We then decrement the PC twice to return it to its original state (pcdec x2), then we add one to the stack pointer (csp++) and pcinc, setsub as usual.

Fig. 1. A flowchart of the control signals FSM

Opcode D (13), pop, is similar to push in that it has two versions: popping to a register and popping to the PC. Popping to a register is like memory-to-register assignment: First we decrement the stack pointer (csp–), then we take what's in the stack (Estack) and move it to the desired register (Crx, sel1), then poinc and setsub.

To pop to the PC, we first decrement the stack pointer (csp-), same as before, but after taking it from the stack (Estack), instead of putting it into a register, we just put it in the PC (Cpc). We then skip the pcinc step, since we just updated the PC by putting a new value in it instead, and setsub as normal.

Opcode E (14), unconditional jump, is very straight forward. After fetching, we take the value from the desired register (Erx) and put it into the PC (Cpc). We again do not increment the PC, and instead just skip straight to setsub.

Finally, opcode F (15) is a conditional jump. We first take the value we are comparing to from the register and put it onto the bus (Erx, sel0). The data bus is connected directly to the compare logic, which makes the comparison immediately and stores the result in a D-latch (Ccmp), using the last four bits of the instruction as flags to determine which comparison, ==0, !=0,  $\xi$ 0, or  $\xi$ 0, to make. Then, if the comparison is true, the FSM jumps like it would in opcode 14 by moving the value from the register (Erx) to the PC (Cpc), the setting the subcounter (setsub) as before. If the comparison is false, the

FSM simply performs the usual pcinc and setsub.

Finally, the FSM can also handle interrupts from the peripheral slots and the reset button. If an interrupt is received from a peripheral slot, instead of fetching, the computer immediately takes the PC (Epc) and puts it onto the stack (Cstack) to be jumped to once the interrupt service routine is finished, then increments the stack pointer (csp++). It then takes the interrupt function location from the dip switches (Edip) and puts it into the PC (Cpc). Since the PC was updated manually, there is no need to pcinc, but the FSM does setsub as always.

If the reset button is pushed, the FSM stops all the other devices from putting anything onto the bus. Because the bus lines each have a pulldown resistor (i.e., a resistor on them connected to ground), the value of the bus is 0x0000 by default, when nothing is being actively put on it. Then, the FSM activates the write enable on every register and counter, which takes the value 0x0000 on the bus and stores it in all of them, resetting them. It does not, however, reset the instruction RAM, which means that you can run the program again without having to reupload it, and it also leaves the stack and data RAM alone (though because they are volatile memory, they are undefined when the computer starts up anyway).

#### V. PROJECT DESCRIPTION - SOFTWARE

## A. Assembler ("romASM")

The assembler, which I will refer to as romASM is designed to act as a direct mapping to the bitcode, while also allowing for the implementation of higher level concepts like functions and loops that are arduous to implement with bitcode alone. This also allows us to fix up some of the shortcomings of our ISA. For example, as previously mentioned, there is no instruction for a left shift, whereas using the addition trick, the assembler has a built in instruction for it. Lastly, in any scenario where instructions have flags or bits specifying other nuances (push and pop have  $Op_2$ , conditional jump has flags), those were split into different assembly instructions. Following this, the capabilities of romASM are specified in full in Table III.

## VI. PROJECT DESCRIPTION - HARDWARE

The hardware was designed using 74XX series logic chips for the most part. The general AND, NAND, OR, NOT, and XOR gate IC data sheets can be found in references [4], [5], [6], [7], and [8]. These chips contain 4 logic gates (6 for the NOT gate chip) in a single chip and are powered with 5 volts. The more specialized chips are discussed later in their sections.

## A. Board 1

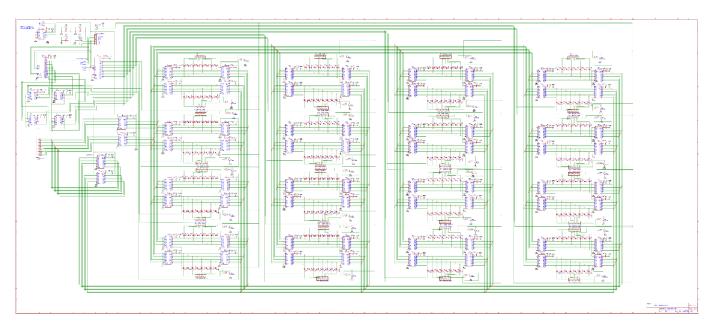

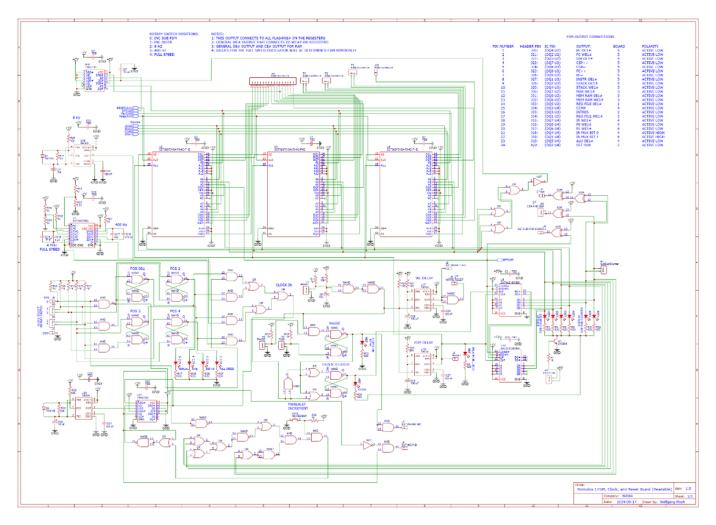

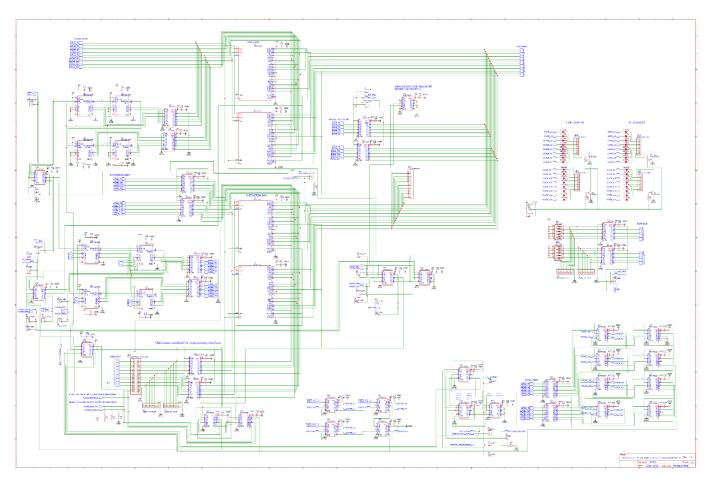

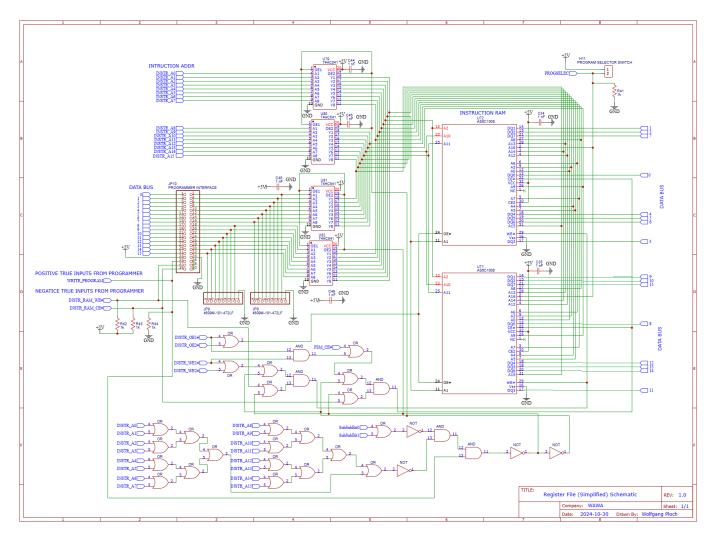

- 1) Overview: Board 1 contains the register file and supporting circuitry The register file was chosen to have 16 registers because in order to address 16 registers, four bits are needed. Using 4 bits to select the register allows three registers to be chosen and the four-bit opcode to be specified all in one 16-bit instruction. Each register stores 16 bits. Each bit of each register was designed to be indicated with an LED. The SN74HC573 8-bit register [9] was chosen to store the contents of each register. Because each are 16-bit, two 74HC573s are needed per register. Unfortunately, the tri-state buffer built into the 74HC573 was not able to be used as we needed access to the data even when it is not active. The OE# of all the buffers were grounded so the output always reflected the data. The full Schematic of the register file board can be seen in Figure 2. It is referred to as board 1 in other sections.

- 2) LED Displays: The LEDs sourced were tested with various resistor values. A pleasant brightness was found with 820  $\Omega$  resistors. One LED draws 4.2 mA in this arrangement. This means the board could draw up to 1.075 amps from just the LEDs if 0xFFFF is stored in all the registers. To save space on the board, instead of using one discrete resistor for each LED, 8-resistor resistor arrays were sourced. These are SIP-9 components that have 8 resistors with one common pin. The anodes of each LED connect to the output of the register and the cathodes are grouped into 8s and connected to the resistor array, 2 resistor arrays per register. The common pin of each resistor array is connected to ground through a 2N3904 with a 1 K $\Omega$  resistor on the base. The other ends of the resistors are all connected to a common point. The transistor allows all the LEDs to be turned off with a single signal. This will be useful when running the computer at the highest speed.

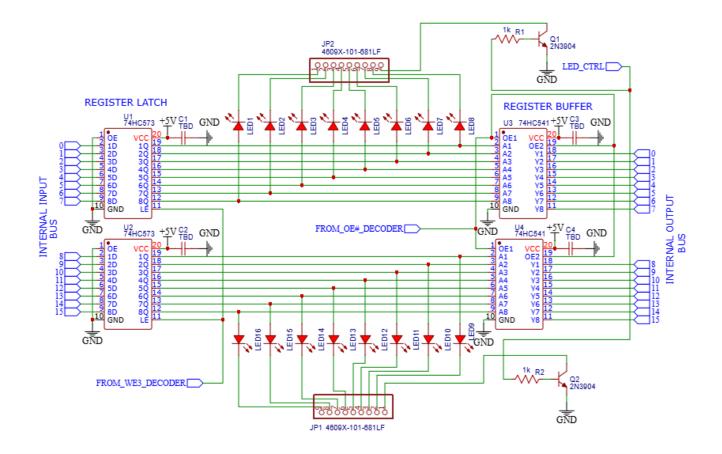

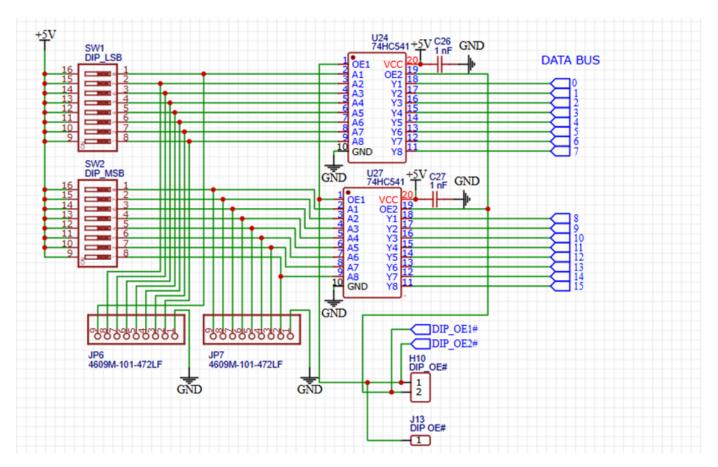

- 3) Register Design: The outputs of the registers are connected to a 74HC541 buffer IC [10]. It is an 8-bit device so two of them are needed per register. The OE# are controlled by the decoder. All outputs of these buffers are connected by bit and then feed into two more 74HC541s to act as the final output enable. The schematic of a single register can be seen below in Figure 3.

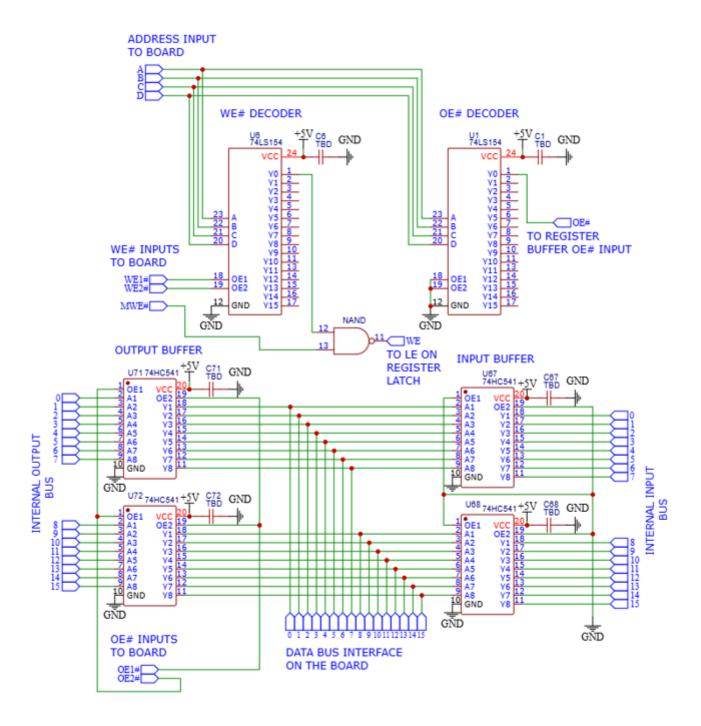

- 4) Addressing the Registers: Two 74LS154s [?] were used to make the decoder. One is connected to the 4-bit address and its outputs connect directly to the OE# on the buffer pairs. The outputs of the 74LS154 and OE# inputs on the 74HC541 are both active low. The enable pins of the decoder are connected to ground to constantly enable the decoder. This way, one of the registers is constantly on the internal bus. The final buffer mentioned above connects the selected one to the bus using the OE# inputs on the board. The other decoder is used to write to the registers. The two WE# s connect to its two enable pins. Each output passes through a NAND gate whose other input is wired to MWE# . Pulling MWE# low causes all the registers to be written simultaneously. This is used during an asynchronous reset. Its address pins are also connected to the 4-bit address input. Each chip on the circuit has a 1 nF capacitor across its power pins to decouple the IC. The boards inputs are OE1#, OE2#, WE1#, WE2#, 4-bit address, LED CTRL. It has a 16-bit IO connection for the data bus. A trace width calculator was used to design the widths of the traces on the PCB to ensure they could supply the proper power. A simplified schematic of the control circuitry can be seen below in Figure 4.

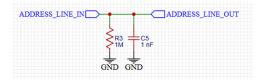

- 5) Modifications: The PCB needed two modifications to work properly after its design and order. The first modification was the addition of the second OE# input to the board. The overall low-level architecture was not solidified before the PCB was ordered and it was not yet known that a second OE# would be needed. It was created by adding a daughter board on the PCB with a single 74HC32. The second modification was adding parallel RC networks on each of the four-bit address inputs for addressing the register. Transient issues were observed when multiple registers started to write at the same time due to errant pulses on these lines. The Parallel RC networks suppressed these and stopped the transient voltages. The resistor and capacitor values are  $1\ M\Omega$  and  $1\ nF$  respectively. One of these networks can be seen in Figure 5.

## B. Board 2

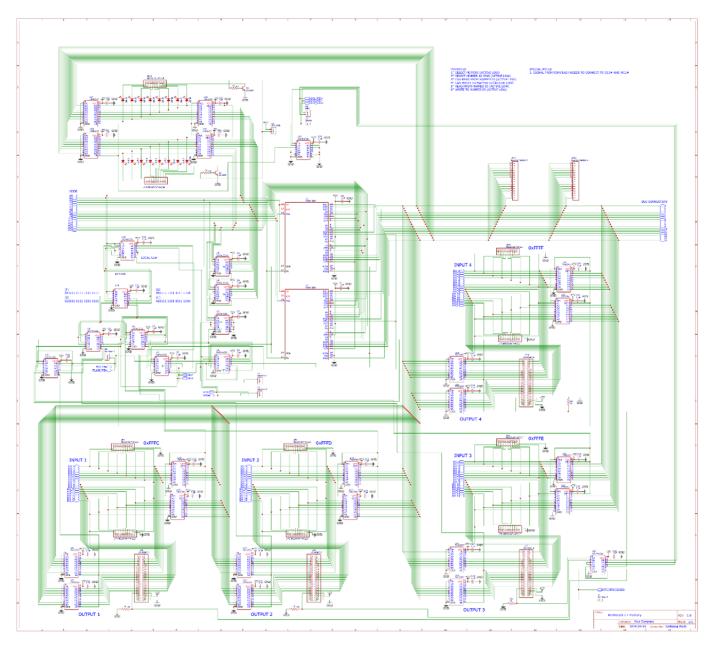

1) Overview: The purpose of the FSM Clock and Reset Board (Board 2) is to generate the clock signals, the logic to switch between them, the reset signal, the control signals for the registers and other items on the other boards, and the timing signals used by the RAM chips. The control signals for the rest of the boards are generated using the outputs of flash memory chips, the SST39SF010A [11] to be exact. The reason that this design approach was taken was to allow for the finite state machine that runs the computer to be customizable. This proved to be a smart choice, as the finite state machine logic stored in these chips was rewritten

TABLE III ROMASM SPECIFICATION

| Instruction           | Registers                                            | Format       |

|-----------------------|------------------------------------------------------|--------------|

| Register to Register  | $R_A \rightarrow R_Y$                                | MOV rA rY    |

| Label to Register     | $LABEL \to R_Y$                                      | MOV LABEL rY |

| Immediate to Register | $\operatorname{imm} \to R_Y$                         | MOV imm rY   |

| Register to Memory    | $R_A \to M[R_B]$                                     | STR rB rA    |

| Memory to Register    | $M[R_A] \rightarrow R_Y$                             | LDA rA rY    |

| Bitwise OR            | $R_A - R_B \rightarrow R_Y$                          | OR rA rB rY  |

| Bitwise NOT           | $\sim R_A \rightarrow R_Y$                           | INV rA rY    |

| Bitwise AND           | $R_A \& R_B \rightarrow R_Y$                         | AND rA rB rY |

| Bitwise XOR           | $R_A \hat{R}_B \to R_Y$                              | XOR rA rB rY |

| Add                   | $R_A + R_B \rightarrow R_Y$                          | ADD rA rB rY |

| Subtract              | $R_A$ - $R_B 	o R_Y$                                 | SUB rA rB rY |

| Logical NOT           | $!R_A \rightarrow R_Y$                               | NOT rA rY    |

| Logical Shift Right   | $R_A >> 1 \rightarrow R_Y$                           | SHR rA rY    |

| Logical Shift Left    | $R_A <<1 \rightarrow R_Y$                            | SHL rA rY    |

| Push                  | $R_A \to \text{Top stack}$                           | PUSH rA      |

| Call                  | $PC+2 \rightarrow Top stack$<br>$R_A \rightarrow PC$ | CALL rA      |

| Pop                   | Top stack $\rightarrow R_Y$                          | POP rY       |

| Return                | Top stack $\rightarrow$ PC                           | RET          |

| Unconditional Jump    | $R_A 	o 	ext{PC}$                                    | JMP rA       |

| Jump If Equal         | If $(R_B == 0)$ : $R_A \to PC$                       | JEZ rA rB    |

| Jump If Not Equal     | If $(R_B != 0)$ : $R_A \to PC$                       | JNZ rA rB    |

| Jump If Greater       | If $(R_B > 0)$ : $R_A \to PC$                        | JGZ rA rB    |

| Jump If Less Than     | If $(R_B < 0)$ : $R_A \rightarrow PC$                | JLZ rA rB    |

Fig. 2. Full Schematic of Register File Board

multiple times to compensate for problems discovered during troubleshooting. The full circuit can be seen below in Figure 6. It is important to note that this circuit was made using discrete gates rather than full chips. This was done to make the schematic more intelligible. The schematic used to create the PCB looks different but represents the same circuit. 1 nF bypass capacitors are placed on the power rails of every chip

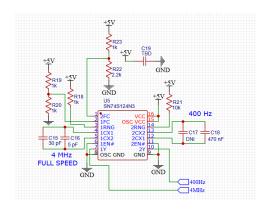

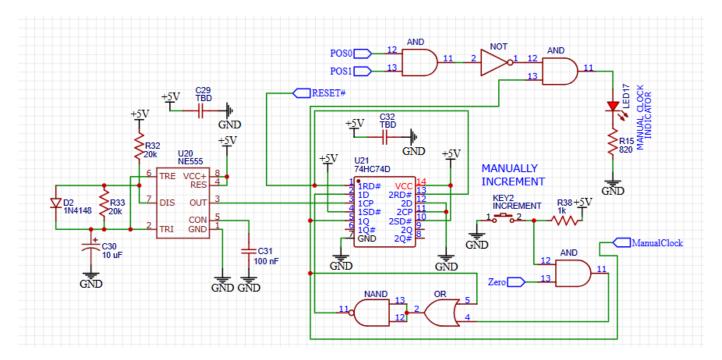

2) Clock Signals: The board creates five different clock signals that can be selected using the rotary switch mounted on the control panel. The speed options are 4 MHz, 400 Hz,

8 Hz, manually increment one full instruction, and manually increment one sub-instruction. The 4 MHz and 400 Hz clock signals were generated using a single SN74S124 oscillator chip [12]. It contains 2 independent oscillators. The chip requires a voltage present at the FC pin, a current through the RNG pin and a capacitance across the two CX pins. Unfortunately, the datasheet graphs for the voltage, current and capacitance values did not match up completely with the oscillation frequency. Different values were used until the desired frequencies were obtained. The oscillator circuit can

Fig. 3. Simplified Schematic of a Single Register in the Register File

be seen below in Figure 7.

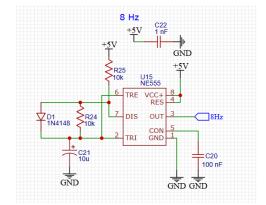

The 8 Hz oscillator was created using an NE555 timer chip [13]. It was wired in a generic astable mode with the addition of a 1N4148 diode to bypass the second resistor. The purpose of this diode is to make the capacitor charge through one of the resistors and discard through the other. Setting the values of both resistors to the same value creates an oscillator with a perfect 50% duty cycle. This signal is more pleasing to the eye of the user. With this modification, the equation for the oscillating frequency becomes

$$f_{osc} = \frac{1}{1.34RC}$$

$10~K\Omega$  resistors a 10 uF capacitor were chosen which yield an oscillation frequency of 7.46 Hz. The schematic for this oscillator can be seen below in Figure 8.

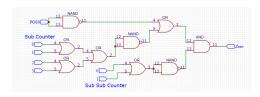

The oscillator sections for the two manually increment models were a little more complicated to design as they required their own finite state machine. The sub-FSM and sub-sub-FSM counter needed to be used in this FSM. They will be described in more detail later. The sub-sub-FSM counter is a two-bit counter used to time the operations that happen in a sub instruction. The sub-FSM counter is a four-bit counter that is directly driven by the sub-sub-FSM counter. It is used to keep track of the current sub instruction. In order to increment

through a sub-instruction, the FSM needs to start oscillating when a button is pressed and stop oscillating when the sub-sub-counter is 0b00. In order to increment though a full instruction, the FSM needs to start oscillating when the button is pressed and stop when both the sub-counter and sub-sub counter are 0b0000 and 0b00 respectively. Instead of designing two FSMs for each of these options, a single one was designed with an input that is high when either the sub-sub counter is 0b00 and increment one sub instruction is selected on the rotary switch or both the sub-sub counter and the sub counter are 0b00 and 0b0000 respectively. The logic for this part can be seen below in Figure 9. "POS0" is the position on the rotary encoder that corresponds to manually increment one sub instruction, it is active low.

The finite state machine was then developed using the one zero signal. The finite state machine is a mealy machine because it uses both current and stored values to determine the next output state. It has one output. The output stays low if the button is not pressed. Once the button is pressed, the output will toggle until the zero input is high, signaling that it has either reached the end of the instruction or sub instruction. An artifact of this FSM is that if the button is held down, the computer will increase forever until the button is released, it will then finish the instruction that it is on. The frequency that

Fig. 4. Simplified Register Control Circuitry Schematic

Fig. 5. RC Network Used to Filter Address Lines

this oscillation occurs at is 4 Hz. This was chosen so there is enough to see everything that is happening as this is mostly a feature for debugging. Another artifact is that the button needs to be held down for at most a 4th of a second so the FSM can see it and begin its cycle. The last artifact is that the finite state machine will trigger if the sub counters are not zero even if it is not on the manual setting. For instance, if the computer is run at a different speed, paused, and switched to manual, it

Fig. 6. Full Finite State Machine, Clock and Reset Board Schematic

Fig. 7. 4 MHz and 400 Hz Oscillators

Fig. 8. 8 Hz Oscillator Schematic

will automatically start incrementing if the sub counter were not at zero at the time the computer is paused.

To make the finite state machine, a 74HC74 Dual D-Latch [14] was used to store the state and logic was used to realize the transfer table. A 4 Hz oscillator was designed using an NE555 [13] and the same equation used to design the 8 Hz

oscillator. This circuit can be seen in Figure 10. "POS0" and "POS1" are the two positions on the rotary encoder that correspond to the two manual modes. The logic designed using them flashes the LED indicator on the control panel when clocking through manually.

Fig. 9. Zero Determination Logic Schematic

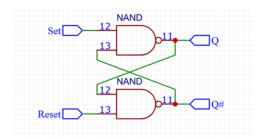

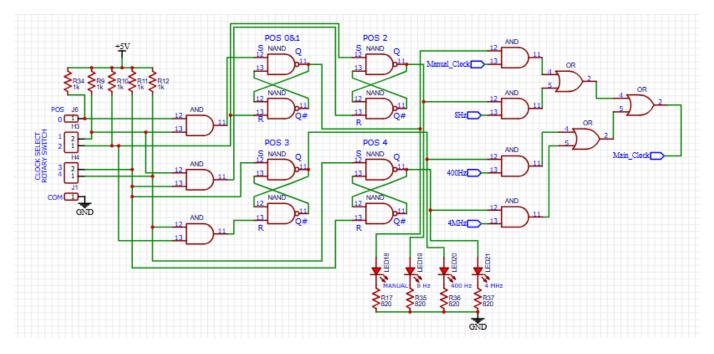

To switch between all of the clock signals, a 5-position rotary switch is used. The common pin is grounded which each of the position pins are pulled to 5 volts using a 1  $k\Omega$  resistor. To generate the signals used to select the different clocks, a sophisticated SR latch circuit was designed. Physical switches often introduce "bouncing" in a circuit. The metal contact vibrates at the instant it is closing causing an undesired, short series of pulses upon a transition. To prevent this, the circuit was designed to latch the positions the instant that they are reached. The basic principle is that the desired position on the rotary switch sets its corresponding latch, this latch is then reset by the positions on either side of it. For instance, the latch for position 2 is set by position 2 and reset by either position 1 or 3. Positions on the edges require one reset (When at position 0, it can only possibly turn to position 1 from there). The positions 0 and 1 both correspond to the manual increment modes. Since both connect the same clock source to the clock input, they are combined and treated as one position as far as this debouncing circuit is concerned. The SR latches used in this circuit and the rest of the board are made from 2 NAND gates in an arrangement shown in Figure 11. The main output (Q) is active high (Q#) is active low and the reset and set inputs are active low as well.

These were used to make the rotary switch selection circuit. The outputs of the position latches than feed into AND gates. The other input of the AND gates are connected to the corresponding clock. These are all ORed together to create a single clock output. This portion of the circuit can be seen below in Figure 12.

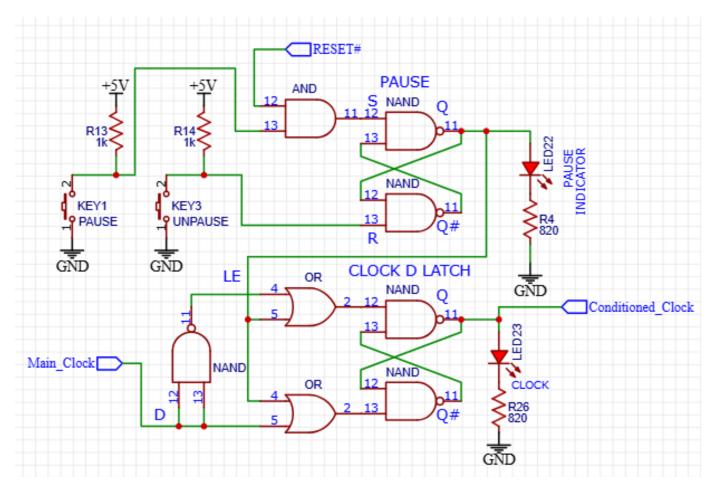

- 3) Pause Handling: This "main clock" signal created in the circuit above is connected to the input of a D latch. This D latch is used to pause and un-pause the computer by latching the clock when the pause button is pressed. The pause and un-pause buttons are located on the control panel. There is an indictor for pause on the control panel and the circuit board. To make it easy to keep the computer in its reset state upon startup, reset automatically pauses the computer. Pressing pause sets the pause SR latch while pressing unpause, resets the latch. These SR latches are again designed using the NAND gate SR latch in Figure 6. The Q of the Pause SR latch is then connected to the LE input of the D latch. The "Conditioned Clock" is the final clock signal that will be used to drive the counter ICs. This portion of the circuit can be seen below in Figure 13.

- 4) Reset Timing: The computer resets itself when it is turned on and when the user presses the reset button on the control panel. To create this reset signal when the computer

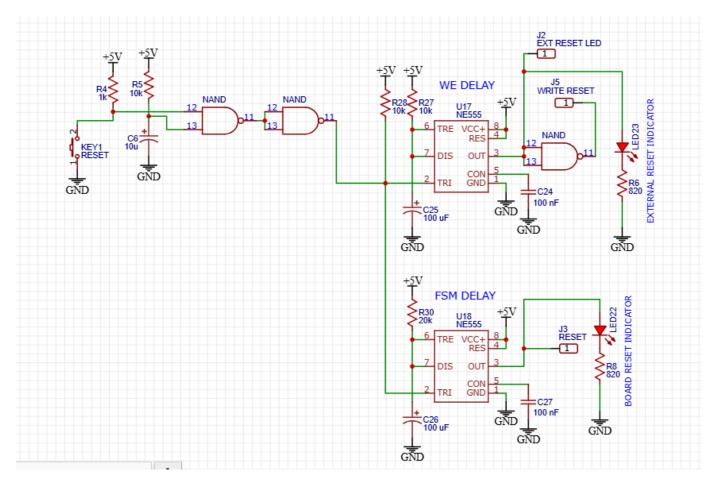

is powered on, an RC network is used to create an active low signal. The capacitor voltage starts at 0 volts and charges through the resistor until it reaches the high input level of the logic gate. With a resistor value of 10  $k\Omega$  and 10 uF, this reset signal takes 120 milliseconds to reach the high threshold level of the logic gate family used. This pulse is then ANDed with an active low button press to create a combined signal. This active low reset signal "RESET#" then connects to a few latches on this board. It can be seen in Figures 5 and 8. This "RESET#" is used to trigger two NE555 timers [13] in monostable mode. The first one is the "WE DELAY" which creates a one second pulse and the second is the "FSM DELAY" which creates a two second pulse. The reason these two timing signals are needed comes down to the latches used in all of the registers. They level triggered, not edge triggered. This means that the data that is latched into them needs to be held at the inputs after the latch enable input is deactivated. The data bus is pulled to ground using 4.7  $k\Omega$  resistors on board 4. The FSM DELAY timer is an input to the FSM flashes. When this input is high, the all of the output and write enables of all of the registers are deactivated, meaning that nothing is on the bus. The resistors pull the bus to ground. The output of WE DELAY is inverted, then wired off the board to the master writes on all registers in the computer. The delay for the FSM is longer than the delay used to latch the registers to ensure they all latch 0x0000 properly during a reset. The reset and timing circuitry can be seen in Figure 14.

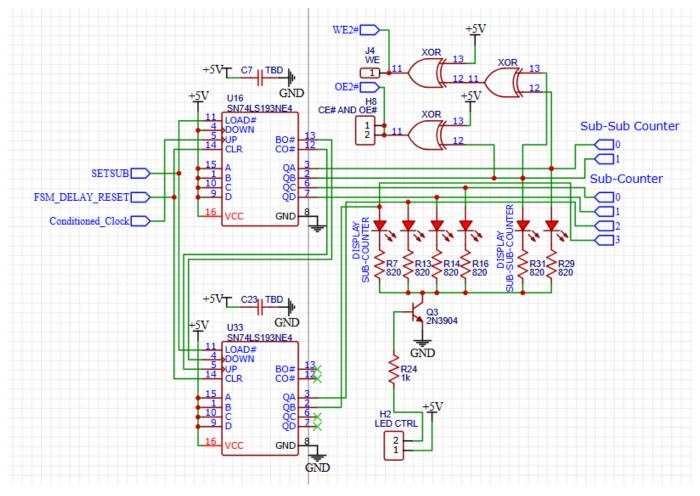

5) Timing Signals and Counters: The sub counter and the sub-sub counter described in previous sections are generated using two 4-bit binary counter ICs, the 74LS193 [15]. This IC has a borrow and carry outputs that makes it easy to string them together and create counters higher than 4 bits. The carry output is connected to increment of the next chip and the borrow output is connected to its decrement. This is how the two 74LS193s were connected in the circuit. When the increment or decrement inputs on the chip are being used, the other one needs to be pulled to Vcc. Because this counter is only incrementing, the decrement input is permanently tied to 5 volts. The counter has an active high clear, both are connected to the FSM DELAY. The counter IC also offers 4 inputs for each bit. There is an active low load input as well. When this load input is pulled low, the data on these inputs is latched to the outputs. All of the data inputs on both chips are pulled high to 5 volts. The load input is connected to one of the FSM outputs, called SETSUB. The lowest order 2 bits of this 8 bit counter are the sub-sub counter, the next 4 bits are the sub-counter. The highest order 2 bits are unused. Since not all instructions use the same amount of sub instructions, there is a sub instruction called SETSUB. As a side note, this output is inverted and wired to an output on the board, an active high version is needed by board 5 to deal with hardware interrupts. When it is activated, it loads 0b111111 to the combined counter. This jumps the counter to the end, causing the next clock pulse to take it to 0b000000, and therefore, the next instruction. This is a way of terminating the instruction after all of the sub instructions are done instead of having to

Fig. 10. Manual Increment Finite State Machine Circuit

Fig. 11. SR Latch Circuit Using NAND Gates

wait for the counter to count past the unused sub-instruction slots.

Each of the 6 bits are connected to LED indicators on the board. These indicators (along with the main clock indicator) have their cathodes tied to the collector of a 2N3904 transistor. The base of this transistor is then controlled by the main LED control switch on the control panel. This connects to all of the other cathode transistors controlling all of the other LEDs on the other boards.

Special timing routines need to be used when writing and reading information to the selected SRAM chips, the AS6C1008s [16]. Their wiring is exploring in more detail when discussing their circuits, but the timing will be described here. The AS6C1008 does not have separate input and output signals, instead, IO pins that switch. The chip requires the WE# pin be pulled low and a period of time elapse before the CE# input be pulled low and data be present at the pins. Since the IO pins of the chip are connected directly to the data bus, this means the data cannot be present on the bus until a time after the WE# input is pulled low. The period of time is much

shorter than the maximum clock frequency of the computer, but it still needs to be accounted for. This timing issue is the reason behind the two-bit sub-sub clock. This creates four different slots that be used to create this timing sequence. The timing sequence can be seen below in Figure 15.

WE is write enable, OE is output enable, and CE is chip enable. This timing sequence works for the write and output enable inputs of the registers as well. The reason that they are labeled with a 2 after the name is due to the way the FSM selected the register of SRAM to use. Every device has two WE# inputs and two OE# inputs. Both inputs must be low for the desired operation to take place. The first ones (OE1# and WE1#) are connected to signals from the FSM flash chips. This is way the FSM selects the devices needed for the subinstruction. The second set of inputs (OE2# and WE2#) are controlled by the timing sequence seen in Figure 10. This allows the timing sequence to control the devices selected by the FSM. Each of the SRAM chips has two extra inputs (CE1# and CE2#). CE1# is created on the board by ANDing its OE1# and WE1#. This reduces the number of outputs needed from the FSM flash chips. This allows the chip to be enabled if it is being written to or read from. Logic was used to generate these timing signals from the two bits of the sub-sub counter. The counter circuit and timing signal generating circuit can be seen below in Figure 16.

6) Interrupt Handling Correction: The interrupt signal generated on board 5 was initially a direct input to one of the addresses of the flash chips. This caused errors when an interrupt was triggered half way through an instruction. The solution was to latch the state of the interrupt input at the beginning of an instruction and use a control signal from the

Fig. 12. Rotary Switch De-bounce and Clock Selection Circuitry

Fig. 13. Clock Pause Handling Circuit

Fig. 14. Reset Timing Circuitry

| Sub-Sub Counter | 0b00 | 0b01 | 0b10 | 0b11 |

|-----------------|------|------|------|------|

| WE2#            | High | Low  | Low  | High |

| CE2#            | High | High | Low  | Low  |

| OE2#            | High | High | Low  | Low  |

Fig. 15. Sub-Sub Counter Control Signals Timing Diagram

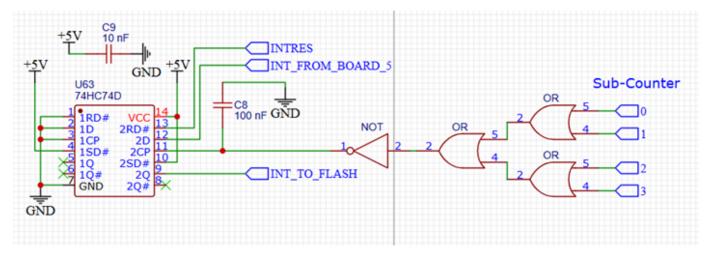

FSM to reset it at the end of the interrupt path. To accomplish this, a 74HC74 D latch [14] was used. Its data bit is connected to the incoming interrupt signal, its Q pin is connected to the address bit of the flash. The clock pin is connected to logic that triggers it when the sub-counter is 0b0000. The reset pin is connected to INTRES, an active low signal created during the troubleshooting process that is used to control timing associated with the interrupt handling. This circuit can be seen below in Figure 17.

7) Finite State Machine Flash Chip Lookup Table: The finite state machines outputs are data locations store across three flash chips. These chips are the SST39SF010As [11]. They have 17 address inputs (A0-A16), and 8 outputs (DQ0-DQ7). They are programmed externally using a microcontroller and inserted into the circuit using 32 PDIP sockets. This way, their WE, CE, OE can be wired to constant voltage sources to make the chip always output data, making it act as

simple combinational logic. Only 12 address inputs are used, the unused five (A12-A16) are wired to ground. The 12 used addresses of the flash chips are all wired together so each chip gets the same address. Each of the outputs of the three chips (24 of them total) is assigned a specific control signal that are sent to other parts of the computer. The programming of the flash chips and the flow of the FSM is explored further in its section. A summary of the inputs to the FSM flash chips can be seen in Table IV.

TABLE IV

INPUTS TO THE FSM FLASH CHIPS

| Signal          | Polarity    | Flash Chip Address |

|-----------------|-------------|--------------------|

| Sub Clock Bit 0 | Active High | A0                 |

| Sub Clock Bit 1 | Active High | A1                 |

| Sub Clock Bit 2 | Active High | A2                 |

| Sub Clock Bit 3 | Active High | A3                 |

| Opcode Bit 0    | Active High | A4                 |

| Opcode Bit 1    | Active High | A5                 |

| Opcode Bit 2    | Active High | A6                 |

| Opcode Bit 3    | Active High | A7                 |

| Interrupt       | Active High | A8                 |

| Op2.0           | Active High | A9                 |

| Jump            | Active High | A10                |

| Reset           | Active High | A11                |

Fig. 16. Sub Counter, Sub-Sub Counter, and Control Signal Timing Circuit

Fig. 17. Interrupt Latching Circuit

The four bits of the opcode come from the instruction register on board 4. The signal "Op2.0" is described in more detail in the section describing the instruction set architecture. Jump comes from board 4 as well and is described in the section on board 4. These are the 12 signals that the FSM

needs in order to determine what its outputs should be. The outputs of the FSM flash chips are summarized below in Table V.

The signals outlined in Table V, not already mentioned in this section are explored in the section corresponding to their

TABLE V FSM Flash Chip Outputs

| Signal        | Polarity    | Destination Board | Flash IC | Pin |

|---------------|-------------|-------------------|----------|-----|

| PC OE1#       | Active Low  | 5                 | U2       | DQ4 |

| PC WE1#       | Active Low  | 5                 | U2       | DQ2 |

| DIP OE1#      | Active Low  | 5                 | U2       | DQ3 |

| CSP++         | Active Low  | 5                 | U3       | DQ7 |

| CSP-          | Active Low  | 5                 | U3       | DQ6 |

| PC++          | Active Low  | 5                 | U3       | DQ0 |

| PC-           | Active Low  | 5                 | U3       | DQ5 |

| INSTR OE1#    | Active Low  | 5                 | U3       | DQ1 |

| STACK OE1#    | Active Low  | 5                 | U3       | DQ2 |

| STACK WE1#    | Active Low  | 5                 | U3       | DQ4 |

| MAR WE1#      | Active Low  | 3                 | U2       | DQ7 |

| MEM RAM OE1#  | Active Low  | 3                 | U2       | DQ0 |

| MEM RAM WE1#  | Active Low  | 3                 | U2       | DQ6 |

| REG FILE OE1# | Active Low  | 1                 | U2       | DQ5 |

| CCMP          | Active Low  | 4                 | U4       | DQ3 |

| INTRES        | Active Low  | 2,4               | U3       | DQ3 |

| REG File WE1# | Active Low  | 1                 | U2       | DQ1 |

| IR WE1#       | Active Low  | 4                 | U4       | DQ7 |

| P0 WE1#       | Active Low  | 4                 | U4       | DQ0 |

| P1 WE1#       | Active Low  | 4                 | U4       | DQ6 |

| IR MUX BIT 0  | Active High | 4                 | U4       | DQ4 |

| IR MUX BIT 1  | Active High | 4                 | U4       | DQ1 |

| ALU OE1#      | Active Low  | 4                 | U4       | DQ5 |

| SETSUB        | Active Low  | 2                 | U4       | DQ2 |

board. These outputs connect directly to header pins on the edge of the board for ease of wiring to other boards.

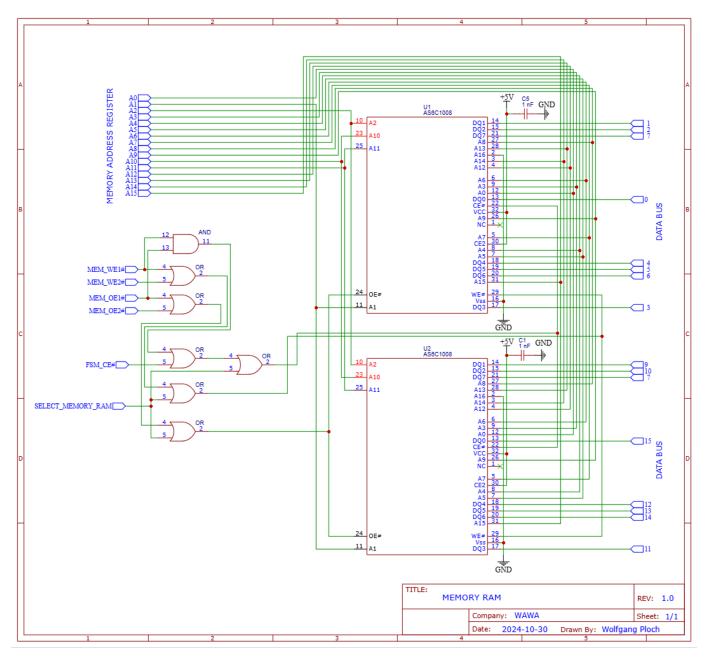

## C. Board 3

- 1) Overview: The memory and mapped IO board contains the memory SRAM, the mapped IO slots, and the memory address register (MAR). It is referred to as board 3 in other design sections. It uses the same SRAM chips as board 5 (the AS6C1008s) [16]. The IO ports have 16 inputs and 16 outputs each. They are addressed as the last four memory addresses; 0xFFFC, 0xFFFD, 0xFFFE, and 0xFFFF. The full schematic of this board can be seen in Figure 18.

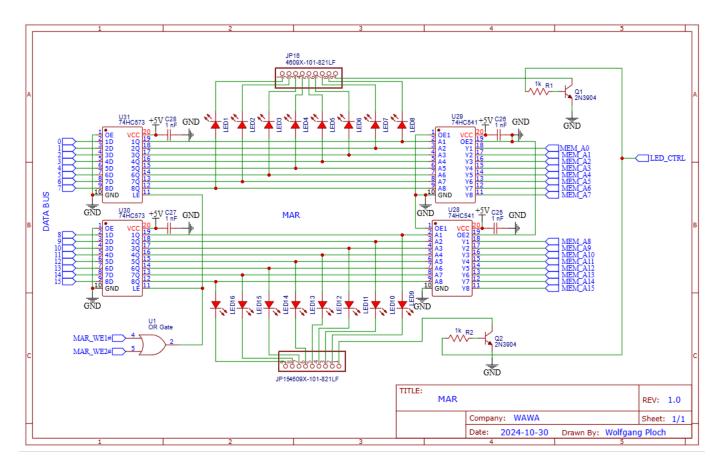

- 2) Memory Address Register (MAR): The MAR stores the memory address used by the RAM to find the correct value. It is identical in operation to the registers on board 1. Its inputs connect directly to the bus and its outputs connect directly to the address inputs of the SRAM chips. Since it is always outputting to the memory RAM, it does not have OE1# and OE2# signals. It's circuitry can be seen in Figure 19. In addition to what is seen in Figure 2, it has a MWE# which writes the register regardless of WE1# or WE2#.

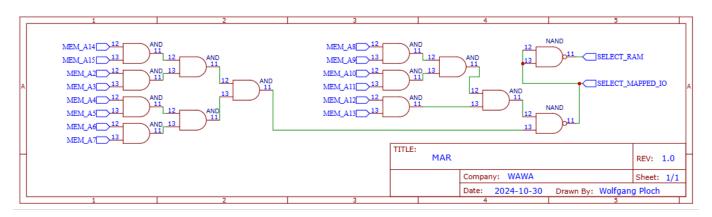

- 3) Address Decoding: The circuit needs to be able to be able to detect if the addresses being written to or read from are in the SRAM or in the memory mapped IO slots (last 4 addresses). This is accomplished using combinational logic. Since the last 4 addresses correspond to the lowest order 14 addresses being 1, (0b11111111111111111xx), if they are all 1 then the address has to be in the memory mapped IO section. Two signals are created, SELECT RAM and SELECT MAPPED IO. These signals are both active low. The logic used to create these signals can be seen below in Figure 20. The schematic shows stand 2-input AND gates for simpicity

but 4-input AND gates were used in the real schematic and the PCB, the 74LS21 [17].

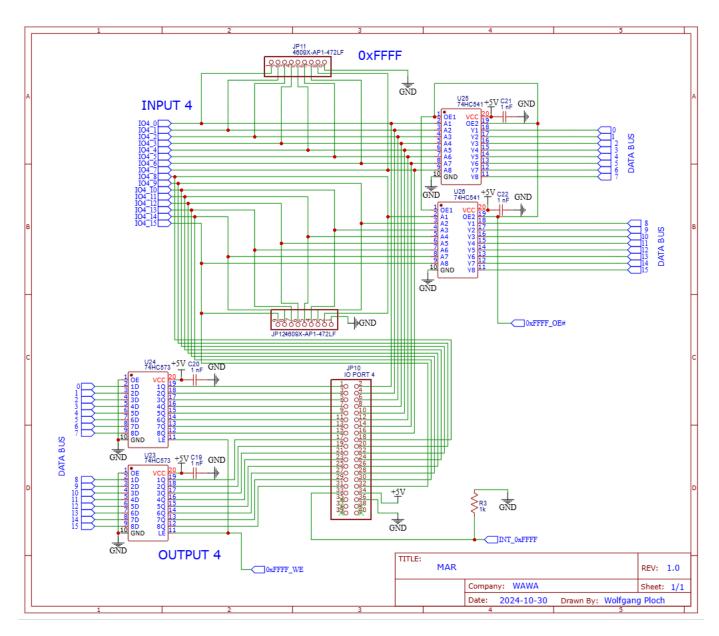

- 4) Mapped IO Port: The four mapped IO ports are identical. They resemble the other registers used in the computer, the difference being they have an IO port instead of LEDs. The output of the two 74HC573s [9] connect directly to the IO port and function as outputs. The inputs of the two 74HC541s [10] are pulled to ground through 4.7  $k\Omega$  resistor arrays. This ensures that the pins do not float when a device is not plugged into them, These function as the inputs to the computer. "Writing" to this memory address causes the value to appear on the 16 output pins while "reading" from this address stores the value of the 16 input pins. Because of this, information "stored" in this address cannot be read from it. Each of the 2x20 pin connectors is wired to the input and output bits. Each connector also has a power and ground pin as well as an interrupt pin. This pin is pulled to ground through a 1  $k\Omega$  resistor. The four interrupts from the four IO slots are ORed together and this creates the INT IN signal used by board 5. The schematic of the 0xFFFF IO slot can be seen below in Figure 21, the other three are identical.

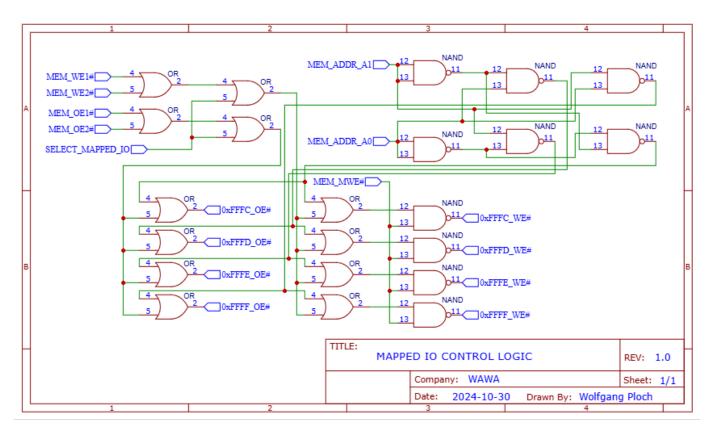

- 5) Mapped IO Port Control Signal Logic: Logic is required to control the different write enables and read enables of the different mapped IO slots. Coming into the board, there are five signals which match the convent seen elsewhere in the computer: MEM WE1#, MEM WE2#, MEM OE1#, MEM OE2#, and FSM CE#. When the MAR holds an address value that belongs to one of the IO slots, logic further decodes that and the input signals to determine which mapped IO port is being selected and whether to write to it or read from it. This portion of the circuit can be seen in Figure 22. The MWE# input is used to write all of the IO ports at once during a reset.

Fig. 18. Full Schematic of the Memory and Mapped IO Board

6) Memory SRAM and Supporting Circuitry: The SRAM chips chosen are the AS6C1008s [16]. They are 128k chips with 17 address pins. Two are used as each only stores one byte (8 bits). Because the computer is only capable of addressing 16 bits, the highest order bit on each chip (A16) is grounded. The IO pins of the chips are connected to the corresponding bits on the data bus. The address bits of the two chips are connected to each other (i.e. chip 1 A0 connected to chip 2 A0 etc.). These pairs are then attached directly to the MAR. The same timing procedure with WE, OE, and CE described in the description of board 2 is used here. On top of the regular timing logic, some needed to be designed to block the signals from the SRAM when the memory mapped IO ports are being

used. The SRAM chips and their supporting circuitry can be seen in Figure 23.

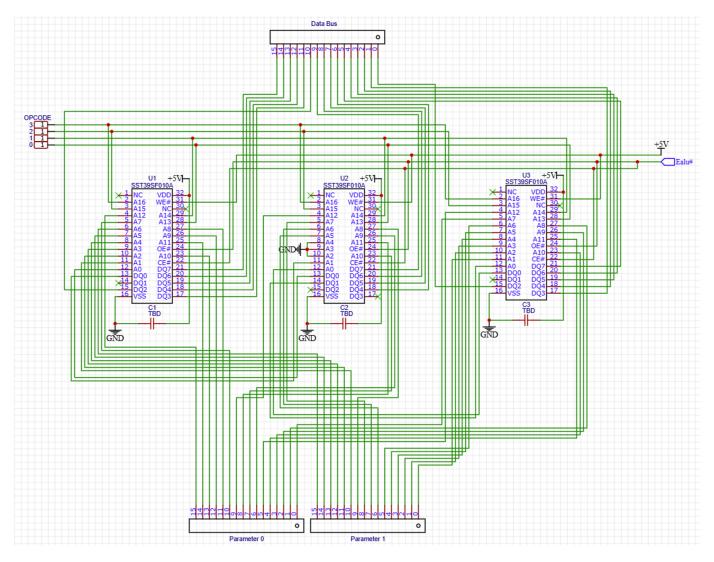

## D. Board 4

1) Arithmetic and Logic Unit (ALU): The ALU is the part of the computer that does all of the arithmetic and logic operations (hence the name "arithmetic and logic unit"). It handles bitwise AND, NOT, OR, and XOR, as well as logical NOT, logical shift right, addition, and subtraction. When one or two parameters are loaded into the "Parameter 0" and "Parameter 1" registers at the bottom of the board and the opcode is sent to the ALU, it immediately calculates the correct answer and, when its output is enabled, places it onto the data bus. The schematic for the ALU in Figure 24.

Fig. 19. Memory Address Register (MAR) Circuitry

Fig. 20. Logic Used to Create SELECT Outputs

We decided to make the ALU out of flash chips (SST39SF010A) [11] instead of with logic gates because it takes up less physical space on the printed circuit board. It works like a lookup table, with the address bits as the inputs and the data bits as the outputs. We had to use three chips because we needed enough address (input) bits for two 16-bit parameters and a 4-bit opcode, and since each SST39SF010A chip only has 17 address bits, we needed three chips to have enough. Table VI shows which pins are used for what values

on each chip.

2) Instruction Register (IR): The instruction register stores, in bitcode, the current instruction being executed by the computer. Many things are taken from the instruction: the four most significant bits of the instruction (bits 15-12) are the opcode, bit 7 is the sub-opcode used for push and pop, and the four least significant bits (bits 3-0) are used as flags to determine which comparison to make in the jump-compare instruction. Additionally, bits 11-8, 7-4, and 3-0 are used as addresses to the register file to determine which registers to

Fig. 21. Sample Memory Mapped IO Port

TABLE VI PIN TO VALUE MAPPING FOR THE ALU. GND MEANS THE PIN IS CONNECTED TO GROUND, NC MEANS THE PIN IS NOT CONNECTED.

| U1: Mos | t significant | U2: N            | Middle      | U3: Least | significant |

|---------|---------------|------------------|-------------|-----------|-------------|

| Pins    | Value         | Value Pins Value |             | Pins      | Value       |

| A16-A13 | Opcode        | A16-A13          | Opcode      | A16-A13   | Opcode      |

| A12-A7  | P0[15:10]     | A12-A9           | P0[9:6]     | A12-A7    | P0[5:0]     |

| A6-A1   | P1[15:10]     | A8-A5            | P1[9:6]     | A6-A1     | P1[5:0]     |

| A0      | Carry in      | A4-A2            | N/A (GND)   | A0        | Borrow in   |

|         |               | A1               | Borrow in   |           |             |

|         |               | A0               | Carry in    |           |             |

| DQ7-DQ2 | result[15:10] | DQ7-DQ4          | result[9:6] | DQ7-DQ2   | result[5:0] |

| DQ1     | N/A (NC)      | DQ3-DQ2          | N/A (NC)    | DQ1       | N/A (NC)    |

| DQ0     | Borrow out    | DQ1              | Borrow out  | DQ0       | Carry out   |

|         |               | DQ0              | Carry out   |           |             |

Fig. 22. Mapped IO Port Control Signal Logic

read and write from. Because these signals and values are so important, the IR always outputs its stored value, that is, its output enable is always active. The opcode, sub-opcode, and flags go directly to the control signals board as inputs to the finite state machine. The three groupings of four bits used for register addressing go through a multiplexer to the register file. The control signals outputs "sel1" and "sel0" are used to determine which portion of the value stored in the IR is used for the register file address: both low sends the first set of four bits, 11-8 (labeled as "Ra" in the instruction set), sel0 high sends the second set, 7-4 (labeled as "Rb"), and sel1 high sends the third set, 3-0 (labeled as "Ry"). Both sel0 and sel1 being high should never occur with our current control signals design, but should this happen erroneously, or should the FSM be changed to allow this to occur, the value 0 will be sent as the address. This multiplexer allows the correct register to be read or written to at the proper time.

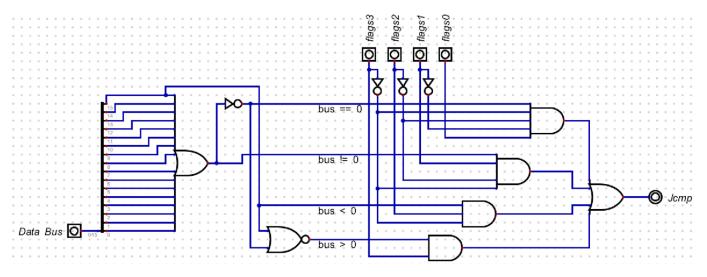

3) Compare Logic: The compare logic uses the value on the bus as well as the flags from the IR to tell the control signals FSM whether or not to jump from a jump-compare instruction. It can do four different comparisons: bus == 0, bus != 0, bus ; 0, and bus ; 0. It computes all four at once, then selects which result (1 for true, 0 for false) to store in the D-latch at the end using the flags. Then the signal from the D-latch goes straight to the FSM. A simplified schematic for the compare logic is in Figure 26.

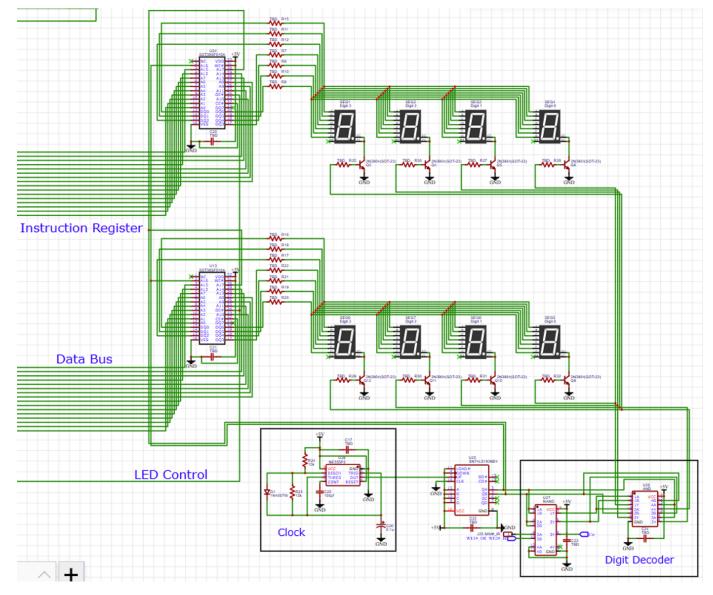

4) 7-Segment Hex Displays: The two sets of 7-segment displays on the board show what is in the instruction register and on the data bus. In a similar way to the ALU, they use flash chips (SST39SF020A) [18] as lookup tables, this time to convert the binary value on the data bus or in the IR to the signals corresponding to the correct segments on each display. The circuit also has a high-speed clock, a counter, and a decoder to quickly cycle between the four digits. Only one digit is on at a time, which lets us save on power and flash chips (since we only have to send data to one digit at a time as well, meaning we need fewer output pins), but because the clock cycles between them so quickly, it is impossible for your eyes to see the flickering, and it appears as though all four are on at once. The schematic for the two displays is in figure ??.

## E. Board 5

- 1) Overview: This board will be referred to as board 5. It houses the stack and instruction RAM, the program counter (PC), the stack pointer counter (CSP), the dip switches used to set the interrupt handler location, the 40-pin programmer interface, and interrupt handling logic. It receives it control signals from board 2. The entire schematic can be seen in Figure 27.

- 2) Program Counter: The PC is a 16-bit value that needs to be able to be incremented, decremented, and loaded to. It stores the current address of the instruction RAM. The ideal

Fig. 23. Memory RAM and Supporting Circuitry