# Circuit Solutions and Tool Flow of Ultra-Low-Power FPGAs

A Dissertation

Presented to

the faculty of the School of Engineering and

**Applied Science**

University of Virginia

in partial fulfillment of the requirements for the degree

Doctor of Philosophy

by

He Qi

December 2017

# **APPROVAL SHEET**

This Dissertation

is submitted in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

Author Signature:

This Dissertation has been read and approved by the examining committee:

Advisor: Benton H. Calhoun

Committee Member: Ronald Williams

Committee Member: Gabriel Robins

Committee Member: Steven Bowers

Committee Member: Kamin Whitehouse

Committee Member: Benton H. Calhoun

Accepted for the School of Engineering and Applied Science:

CB

Craig H. Benson, School of Engineering and Applied Science

December 2017

#### Abstract

Low-power miniature systems for ubiquitous computing such as wireless sensor networks have been developing rapidly in the past years. The growing demand on collecting and analyzing information from surrounding environment drives researchers and engineers to develop Internet-of-Things (IoT). This trend requires future integrated circuits for IoT devices to be ultra-low-power (ULP), flexible, and low-cost. Existing circuit solutions of IoT devices are either too costly such as sub-threshold ASICs, or too power-consuming such as sub-threshold microprocessors. ULP FPGAs operating in near/sub-threshold region, flexible and much lower-power than sub-threshold microprocessors, become a promising hardware solution for IoT applications. In this dissertation, circuit/architecture and tool flow of a custom ULP FPGA are explored and developed.

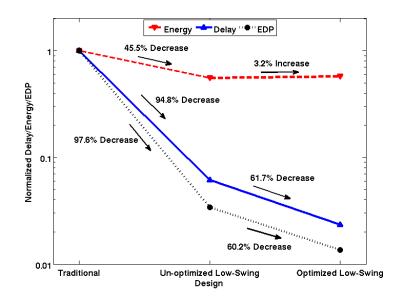

#### 1) Energy Efficient FPGA Interconnect

The global interconnect is the major power consumer of the core fabric of FPGAs. Studies have shown that over 65% of power is dissipated in the interconnection fabric. The same conclusion applies to delay and area. The strict requirements on both speed and energy of IoT applications make energy reduction and energy-efficiency improvement of FPGA routing fabrics a driving challenge. In this dissertation, an energy-efficient low-swing interconnect is modeled, optimized, and evaluated in near/sub-threshold region. When implementing Microelectronics Center of North Carolina (MCNC) benchmarks, the proposed interconnect leads to 68.4% delay reduction and 47.5% energy reduction compared to prior works.

#### 2) Per-Path Voltage Scaling and Power-Gating

Per-path voltage scaling is a technique to reduce FPGA energy to just the minimum while maintaining the overall FPGA speed by reducing the supply voltage on non-critical paths. However, no existing work applied it to FPGA interconnect due to large area overhead. In this dissertation, this problem is solved by using the low-swing interconnect. When using this technique along with power-gating, a 22.3% - 56.5% energy reduction is observed. A custom low-power FPGA is fabricated and measured. When implementing a 4-bit adder, it consumes 277x lower power and 3.4x lower energy than Microsemi IGLOO, which is the most low-power FPGA in the market today.

3) Low-Power FPGA Evaluation Platform

To evaluate custom FPGAs, full tool flow and benchmark support are needed. However, existing commonly used FPGA benchmarks are either too large for ULP FPGAs or too simple to fully utilize ULP FPGA resources. Also, the existing benchmark synthesis tools either only support commercial FPGA architectures, or have crucial limitations on the syntax of input Verilog. In addition, the existing power estimation tools do not accurate for low-power FPGAs and the embedded accelerators/IPs. Solutions to those problems are addressed in this dissertation. The functionality of the custom flows has been verified using a custom low-power application suite. Compared to Microsemi IGLOO, the custom FPGA on average consumes 315x less power and 75x less energy when implementing the custom low-power FPGA application suite.

# Acknowledgement

I firstly want to thank my parents, who give me their utmost support and trust. When I make decisions that I think will surprise them, they always choose to support me with smiles and jokes. Research life is both enjoyable and hard. They completely understand me when I struggled with my research progress. I can't remember how many time they said "we don't expect you to be excellent, but just wish you could happy". I did fell warm and got back to my fighting mode. Thank you! Now we video chat on the phone to share each other's life, but I really miss them.

During my second year of PhD, I met Xiaoyu. She is beautiful, smart, kind, and she is my wife now. These years, I spent a big portion of my spare time on research and learning new skills. I very much appreciate her support and understanding on this. As a PhD of electrical engineering, Xiaoyu supports me not only in the way of family, but also technically. When I have troubles with my research, I am always inspired by talking to her. Xiaoyu and I raised a cute golden retriever Candy. We both amused by her when we disappointed about unexpected failures in research, and finally get pumped again.

I want to thank professor Benton Calhoun, who is my research adviser at UVa. Ben is always generous at giving chance to students who interested in his research. I joined UVa as a teaching assistant. Back then, I was a bad English speaker and not good at expressing my thoughts. Ben encouraged me and agreed to let me join Bengroup. I was so glad to have this opportunity to prove myself and become a research assistant in Bengroup to work on the interesting projects. I learnt a lot from Ben, especially research methodology and project management. I was focused on detailed research questions, but Ben trained me to think broader on the high level. This exercise is so valuable that I can benefit from it for my entire life. I very much appreciate for everything.

When I applied to UVa PhD program, I was attracted by Bengroup website, which made me think this is a professional, friendly, and energetic group. It turned out I was wrong. The fact is Bengroup is even better! The team is very like to share and help each other. I especially want to thank Dr. Oluseyi Ayorinde. Seyi and I worked on the same project, but he joined the group one year before me, which means he knows everything I don't know and have to know. Seyi never hesitates to help and always provide more than my expectation. Even years later, Seyi still always come to my cubic to check if I need any support. It's my pleasure to work with you! Other current and former students (Yousef, Yanqing, Aatmesh, Kyle, Peter, Jim, Alicia, Yu, Patricia, Manula, Farah, Chris, Dilip, Kevin, Arijit, Divya, Abhishek, Harsh, Ningxi, Shuo, Daniel, Jacob, Henry, Rishika, Sumanth, etc.) are also very kind and friendly. I want to thank all of you for the help and being around these years. I am so glad to know you. I also want to thank other faculty, Staff, and my friends who helped me and shared time with me at UVa.

# List of Figures

| 1  | Basic architecture of the core fabric of FPGAs                                                                                   | 3  |

|----|----------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Active energy, leakage energy, and total energy of a FIR filter when                                                             |    |

|    | sweeping its supply voltage $V_{DD}$ [5]                                                                                         | 4  |

| 3  | FPGA Core Fabric Energy Breakdown                                                                                                | 7  |

| 4  | (a) Bi-directional switch box (b) uni-directional switch box                                                                     | 10 |

| 5  | Basic structure of low-swing interconnect                                                                                        | 11 |

| 6  | Diagram of the global interconnect path model                                                                                    | 14 |

| 7  | Path length distribution (a) segment length $= 1$ (b) segment length $= 4$                                                       | 15 |

| 8  | Abstracted Path and branch distribution                                                                                          | 16 |

| 9  | Details of path distribution of MCNC benchmarks                                                                                  | 17 |

| 10 | Table of the Equivalent Capacitance and Resistance of a Wire Segment                                                             | 18 |

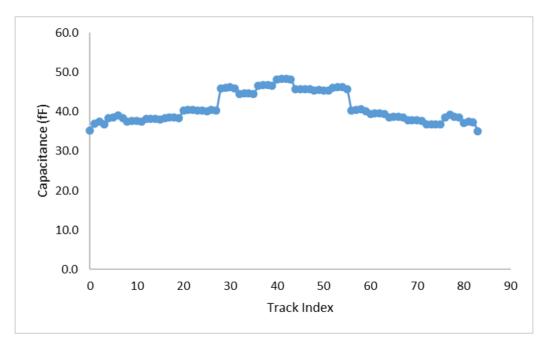

| 11 | Total Capacitance of Wire Segments in a 84-Track Channel                                                                         | 19 |

| 12 | Routing Switch Modeling                                                                                                          | 20 |

| 13 | Knobs of Interconnect Optimization                                                                                               | 22 |

| 14 | The layout photo of the characterization chip $\ldots \ldots \ldots \ldots \ldots$                                               | 23 |

| 15 | Measurement results of the energy and EDP of a path when sweeping                                                                |    |

|    | (a) $V_{DD}$ (b) and $V_{DDC}$ in 130nm CMOS (Path Length = 10)                                                                  | 24 |

| 16 | ED curves of interconnect paths at different $V_{DD}$ in 32nm SOI (path                                                          |    |

|    | $length = 40) \dots \dots$ | 25 |

| 17 | The optimal $V_{DDC}$ value results in minimum EDP of interconnect paths                                                         |    |

|    | with different lengths in 32nm SOI @ $V_{DD}$ =0.4V                                                                              | 26 |

| 18 | The process variation of paths at different voltage                                                                              | 27 |

| 19 | Schematic of different CB topologies: (a) full multiplexer (b) 1-stage                                                           |    |

|    | multiplexer (c) 2-stage multiplexer                                                                                              | 27 |

| 20 | Measured energy and EDP of paths with varying (a) switch size (b)                                                          |    |

|----|----------------------------------------------------------------------------------------------------------------------------|----|

|    | driver size @ $V_{DD}$ =0.4V in 130nm CMOS (Path Length = 10)                                                              | 29 |

| 21 | ED curves of interconnect paths with different switch box topologies                                                       |    |

|    | and sizes @ $V_{DD}=0.4$ V in 32nm SOI (a) path length = 5 (b) path                                                        |    |

|    | $length = 40 \dots $ | 30 |

| 22 | ED curves of interconnect paths with different driver sizes @ $V_{DD}$ =0.4V                                               |    |

|    | in 32nm SOI (a) path length = 5 (b) path length = 40 $\dots \dots \dots$                                                   | 31 |

| 23 | The process variation of paths with different circuit parameters $\ldots$                                                  | 31 |

| 24 | Comparison of the normalized delay, energy, and EDP of buffer-based,                                                       |    |

|    | minimum-sized low-swing, and optimized low-swing interconnect $@$                                                          |    |

|    | $V_{DD}=0.4$ V                                                                                                             | 32 |

| 25 | The energy reduction of MCNC benchmarks when utilizing the opti-                                                           |    |

|    | mized low-swing interconnect in 130nm CMOS                                                                                 | 33 |

| 26 | Signal Degradation along Low-Swing Interconnect Paths                                                                      | 34 |

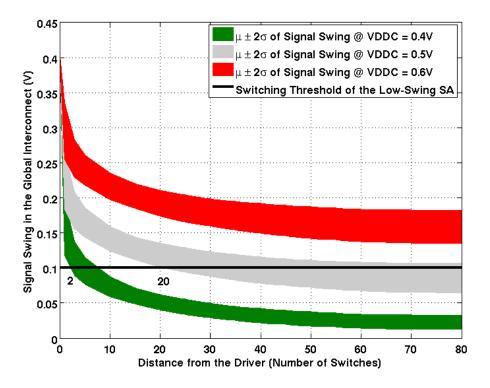

| 27 | The signal swing of low-swing paths with varying length and the switch-                                                    |    |

|    | ing threshold of the level shifter @ $V_{DD} = 0.4 \mathrm{V}$ in 130nm CMOS                                               | 35 |

| 28 | Measured shmoo plot of signal degradation @ $V_{DD} = 0.4$ V in 130nm                                                      |    |

|    | CMOS                                                                                                                       | 36 |

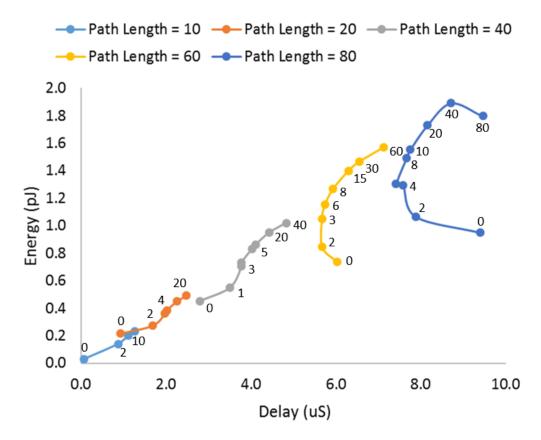

| 29 | Measured ED curves of paths with different numbers of inserted level                                                       |    |

|    | shifters @ $V_{DD} = 0.4$ V in 130nm CMOS                                                                                  | 37 |

| 30 | Simulated ED curves of paths with different numbers of inserted level                                                      |    |

|    | shifters @ $V_{DD} = 0.4$ V in 32nm SOI                                                                                    | 38 |

| 31 | The diagram of traditional subset switch box (left) and the proposed                                                       |    |

|    | folded-subset switch box (right)                                                                                           | 39 |

| 32 | Layout of a 7-switch-points cluster                                                                                        | 40 |

| 33 | Layout of an 84-track switch box                                                                                           | 41 |

|    |                                                                                                                            |    |

| 34 | Area Comparisons of traditional Subset and the proposed Folded-Subset               |    |

|----|-------------------------------------------------------------------------------------|----|

|    | SBs in 130nm CMOS                                                                   | 42 |

| 35 | The diagram of a 10-track Wilton switch box                                         | 42 |

| 36 | The interconnect area of FPGAs implementing MCNC benchmarks .                       | 43 |

| 37 | The energy efficiency improvement by using folded-subset switch box                 | 45 |

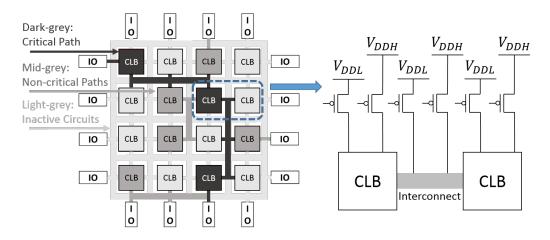

| 38 | The concept diagram of applying per-path voltage scaling and power-                 |    |

|    | gating techniques to FPGA interconnect                                              | 52 |

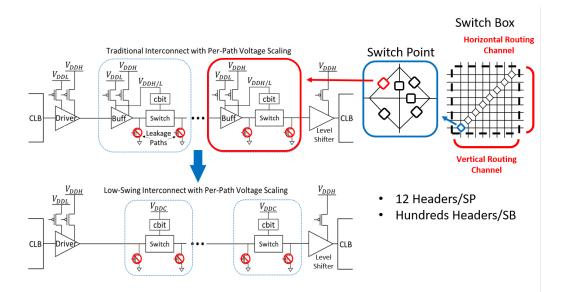

| 39 | The comparison of applying per-path voltage scaling on the traditional              |    |

|    | interconnect and the low-swing interconnect                                         | 53 |

| 40 | The area overhead of headers introduced when using per-path voltage                 |    |

|    | scaling                                                                             | 54 |

| 41 | The percentage of interconnect energy from level shifters under differ-             |    |

|    | ent conditions                                                                      | 54 |

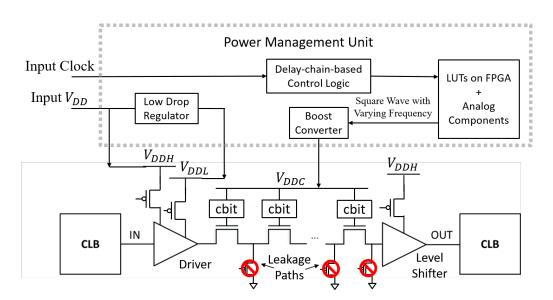

| 42 | The concept diagram of the proposed architecture and the power man-                 |    |

|    | agement unit                                                                        | 55 |

| 43 | The concept diagram of the delay chain circuit and the proposed delay               |    |

|    | detector and voltage controller architecture                                        | 56 |

| 44 | The flow chart of the custom multi- $V_{DD}$ assignment tool $\ldots \ldots \ldots$ | 58 |

| 45 | The energy reductions of the low-swing interconnect implementing                    |    |

|    | MCNC benchmarks using per-path voltage scaling @ $0.6\mathrm{V}$ in 130nm           |    |

|    | CMOS                                                                                | 61 |

| 46 | The affects of cross-talk and power noise on the energy reduction of                |    |

|    | interconnect implementing alu<br>4 $@$ 0.6V in 130nm CMOS $\ .$                     | 62 |

| 47 | The adjustable range of delay and energy of the interconnect imple-                 |    |

|    | menting MCNC benchmarks when using DVS @ $0.6\mathrm{V}$ in 130nm CMOS              | 63 |

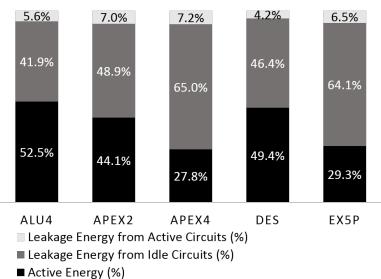

| 48 | Energy breakdown of the low-swing FPGA interconnect implementing                  |    |

|----|-----------------------------------------------------------------------------------|----|

|    | MCNC benchmarks @ 0.6V in 130nm CMOS                                              | 64 |

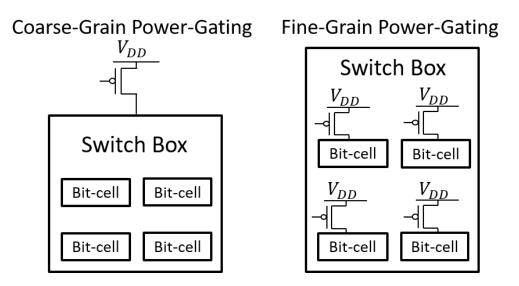

| 49 | The coarse-grain power-gating and fine-grain power-gating architectures           | 65 |

| 50 | Characterization of the headers for power-gating                                  | 66 |

| 51 | The energy reduction of the low-swing interconnect after using power-             |    |

|    | gating and per-path voltage scaling @ 0.6V in 130nm CMOS $\ .$                    | 67 |

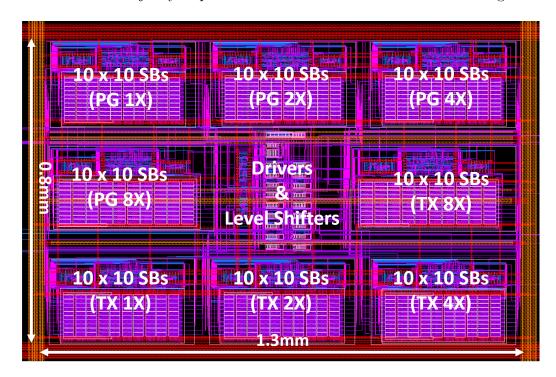

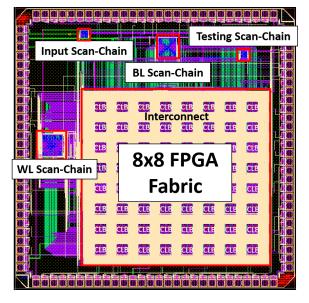

| 52 | Architectural and Circuit-Level Parameters for taped-out FPGA chip                | 68 |

| 53 | The annotated layout of the of the custom FPGA chip $\ . \ . \ . \ .$             | 69 |

| 54 | The measurement results of leakage energy reduction of the custom                 |    |

|    | FPGA chip before and after using power-gating                                     | 70 |

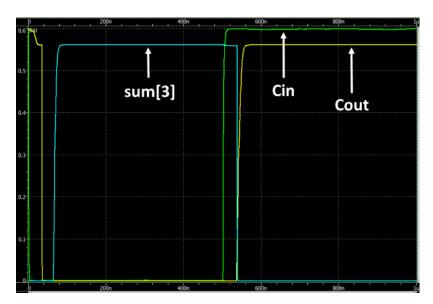

| 55 | Simulated waveforms of a 4bit-adder                                               | 71 |

| 56 | Comparisons of the custom FPGA and existing low-power FPGAs                       | 72 |

| 57 | The flow chart of FGC                                                             | 79 |

| 58 | VTR Applications Characterizations                                                | 80 |

| 59 | Commercial Applications Characterizations                                         | 81 |

| 60 | Ubiquitous Computing Applications Characterizations                               | 83 |

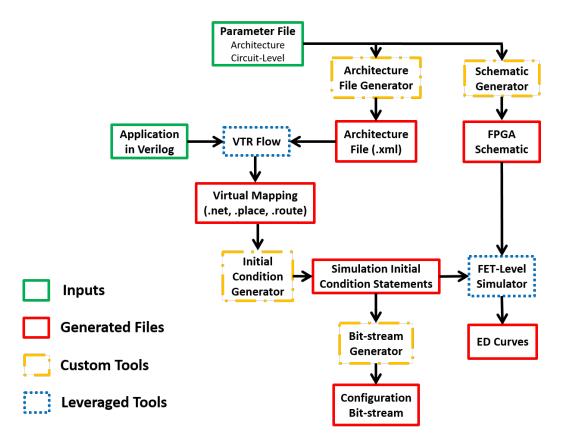

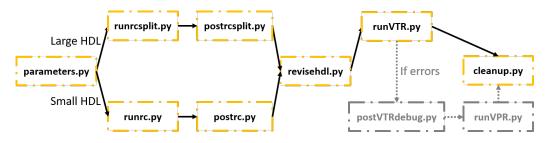

| 61 | The Custom Benchmark Synthesis Flow                                               | 84 |

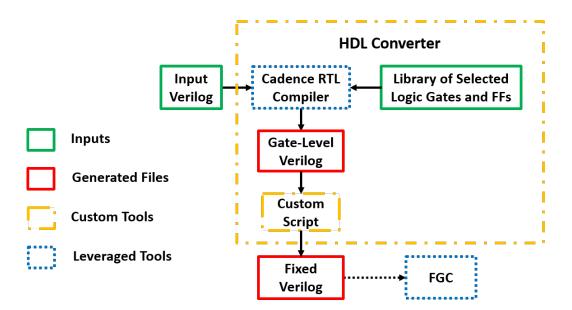

| 62 | Flow Chart of "HDL Converter" in the Synthesis Tool                               | 86 |

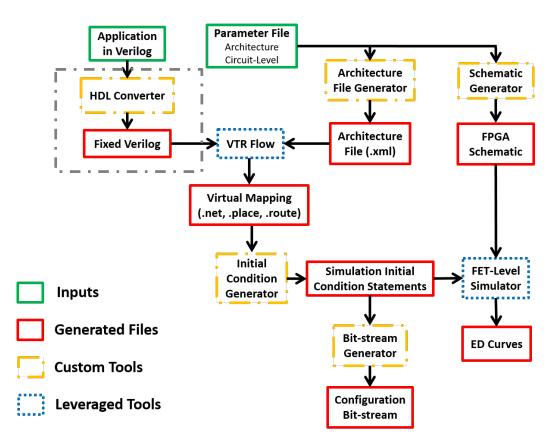

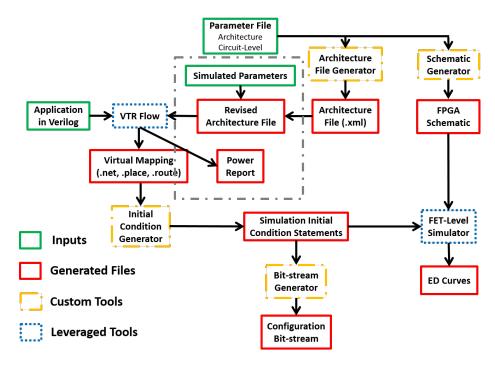

| 63 | Integration of the Synthesis Flow and FGC                                         | 88 |

| 64 | The Fast Power Estimation Flow of the Custom Low-Power FPGA $$ .                  | 89 |

| 65 | Table of parameters of sub-circuits of the custom low-power FPGA                  |    |

|    | used for fast power estimation @ 0.6V in 130nm CMOS                               | 92 |

| 66 | Table of parameters of the custom interconnect used for fast power                |    |

|    | estimation @ $0.6V$ in 130nm CMOS                                                 | 93 |

| 67 | Table of parameters of the embedded memory blocks used for fast                   |    |

|    | power estimation @ 0.6V in 130nm CMOS $\ldots \ldots \ldots \ldots \ldots \ldots$ | 93 |

| 68 | Table of parameters of embedded multipliers used for fast power esti-        |     |

|----|------------------------------------------------------------------------------|-----|

|    | mation @ $0.6V$ in 130nm CMOS                                                | 94  |

| 69 | Comparisons of the measurement result and the estimated result of a          |     |

|    | 4-bit adder                                                                  | 95  |

| 70 | Integration of the Power Estimation Flow to FGC Flow                         | 95  |

| 71 | Comparisons of the Custom Low-Power FPGA with and without Hard               |     |

|    | IPs                                                                          | 97  |

| 72 | Comparisons of the custom low-power FPGA and ASICs when imple-               |     |

|    | menting the custom low-power application suite $\ldots \ldots \ldots \ldots$ | 99  |

| 73 | Comparisons of the custom low-power FPGA and Microsemi IGLOO                 |     |

|    | when implementing the custom low-power application suite                     | 100 |

|    |                                                                              |     |

# Contents

| 1        | Intr | roduct  | ion                                                 | 1  |

|----------|------|---------|-----------------------------------------------------|----|

|          | 1.1  | Motiv   | ation of Low-Power FPGAs                            | 1  |

|          | 1.2  | Thesis  | Statement                                           | 2  |

|          | 1.3  | Goals   |                                                     | 2  |

| <b>2</b> | Bac  | kgrou   | nd                                                  | 3  |

|          | 2.1  | Gener   | al FPGA Architecture                                | 3  |

|          | 2.2  | Sub-tl  | nreshold Operation                                  | 5  |

|          | 2.3  | Existi  | ng Low-Power FPGAs                                  | 6  |

| 3        | Ene  | ergy Ef | ficient FPGA Interconnect                           | 7  |

|          | 3.1  | Motiv   | ation                                               | 7  |

|          | 3.2  | Prior   | Art                                                 | 8  |

|          | 3.3  | Low-S   | wing Interconnect                                   | 10 |

|          |      | 3.3.1   | Overview                                            | 10 |

|          |      | 3.3.2   | Delay and Energy Trade-Off                          | 12 |

|          |      | 3.3.3   | Applicable Conditions of the Low-Swing Interconnect | 13 |

|          | 3.4  | Interc  | onnect Modeling                                     | 13 |

|          |      | 3.4.1   | Overview                                            | 13 |

|          |      | 3.4.2   | Path Length and Branch Distribution                 | 15 |

|          |      | 3.4.3   | Detailed Circuit Modeling                           | 18 |

|          | 3.5  | Circui  | t and Supply Voltage Optimization                   | 21 |

|          |      | 3.5.1   | Overview                                            | 21 |

|          |      | 3.5.2   | Supply Voltage Optimization                         | 22 |

|          |      | 3.5.3   | Circuit Optimization                                | 27 |

|   | 3.6 | Level   | Shifter Insertion                | 34 |

|---|-----|---------|----------------------------------|----|

|   |     | 3.6.1   | Overview                         | 34 |

|   |     | 3.6.2   | Impact to Signal Swing           | 35 |

|   |     | 3.6.3   | Impact to Energy Efficiency      | 37 |

|   | 3.7 | Switch  | n Box Layout                     | 39 |

|   |     | 3.7.1   | Overview                         | 39 |

|   |     | 3.7.2   | Subset Switch Box Area Reduction | 39 |

|   |     | 3.7.3   | Wilton Switch Box Area Reduction | 42 |

|   |     | 3.7.4   | Energy Efficiency Improvement    | 44 |

|   |     | 3.7.5   | Cross Talk                       | 45 |

|   | 3.8 | Future  | e Research                       | 46 |

| 4 | Per | -Path   | Voltage Scaling and Power-Gating | 48 |

|   | 4.1 | Motiva  | ation                            | 48 |

|   | 4.2 | Prior . | Art                              | 49 |

|   |     | 4.2.1   | Per-Path Voltage Scaling & DVS   | 49 |

|   |     | 4.2.2   | Power-Gating                     | 51 |

|   | 4.3 | Per-Pa  | ath Dynamic Voltage Scaling      | 51 |

|   |     | 4.3.1   | Architecture Overview            | 51 |

|   |     | 4.3.2   | Level Conversion                 | 54 |

|   |     | 4.3.3   | Voltage Regulation               | 55 |

|   |     | 4.3.4   | CAD Flow for VDD Assignment      | 57 |

|   |     | 4.3.5   | Energy Reduction Results         | 60 |

|   | 4.4 | Power   | -Gating                          | 63 |

|   |     | 4.4.1   | Architecture Overview            | 63 |

|   |     | 4.4.2   | Header Design for Power-Gating   | 66 |

|   |     | 4.4.3   | Energy Reduction Results                     | 66 |

|---|-----|---------|----------------------------------------------|----|

|   | 4.5 | A Cus   | stom FPGA Chip                               | 68 |

|   |     | 4.5.1   | Chip Description                             | 68 |

|   |     | 4.5.2   | Measurement Results                          | 71 |

|   | 4.6 | Future  | e Research                                   | 73 |

| 5 | Low | -Powe   | er FPGA Evaluation Platform                  | 74 |

|   | 5.1 | Motiva  | ation                                        | 74 |

|   |     | 5.1.1   | Low-Power Application Suite                  | 74 |

|   |     | 5.1.2   | Application Synthesis                        | 74 |

|   |     | 5.1.3   | Fast Power Estimation of the Custom FPGA     | 75 |

|   | 5.2 | Prior . | Art                                          | 76 |

|   |     | 5.2.1   | Low-Power Application Suite                  | 76 |

|   |     | 5.2.2   | Application Synthesis                        | 77 |

|   |     | 5.2.3   | Fast Power Estimation of the Custom FPGA     | 77 |

|   |     | 5.2.4   | FPGA Generation and Configuration            | 78 |

|   | 5.3 | Applie  | cation Suite                                 | 79 |

|   |     | 5.3.1   | Selected VTR Applications                    | 80 |

|   |     | 5.3.2   | Selected Commercial Applications             | 81 |

|   |     | 5.3.3   | Additional Ubiquitous Computing Applications | 82 |

|   | 5.4 | Bench   | mark Synthesis Flow                          | 84 |

|   |     | 5.4.1   | Overview                                     | 84 |

|   |     | 5.4.2   | Description of the Flow                      | 84 |

|   |     | 5.4.3   | Integration of the Synthesis Flow and FGC    | 88 |

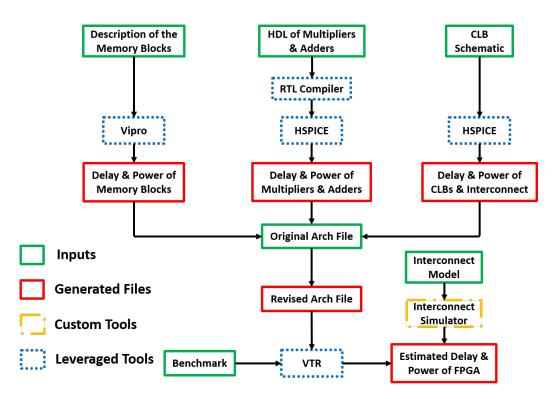

|   | 5.5 | Fast F  | Power Estimation Flow of the Custom FPGA     | 89 |

|                  |                                               | 5.5.1                                                 | Description of the Fast Power Estimation Flow of the Custom |                                                                             |

|------------------|-----------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|

|                  |                                               |                                                       | Low-Power FPGA                                              | 89                                                                          |

|                  |                                               | 5.5.2                                                 | Parameters Used in the Flow                                 | 92                                                                          |

|                  |                                               | 5.5.3                                                 | Accuracy of the Flow                                        | 94                                                                          |

|                  |                                               | 5.5.4                                                 | Integration to FGC                                          | 95                                                                          |

|                  | 5.6                                           | IP Inte                                               | egration                                                    | 96                                                                          |

|                  |                                               | 5.6.1                                                 | Overview                                                    | 96                                                                          |

|                  |                                               | 5.6.2                                                 | Results                                                     | 97                                                                          |

|                  | 5.7                                           | Result                                                | s                                                           | 98                                                                          |

|                  | 5.8                                           | Future                                                | e Research                                                  | 100                                                                         |

|                  |                                               |                                                       |                                                             |                                                                             |

| 6                | Cor                                           | clusio                                                |                                                             | 103                                                                         |

| 6                | Con                                           | clusio                                                |                                                             | 103                                                                         |

| 6                | <b>Cor</b><br>6.1                             |                                                       | <b>n</b><br>y Efficient FPGA Interconnect                   | <b>103</b><br>103                                                           |

| 6                |                                               | Energy                                                |                                                             |                                                                             |

| 6                | 6.1                                           | Energy<br>Per-Pa                                      | y Efficient FPGA Interconnect                               | 103                                                                         |

| _                | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Energy<br>Per-Pa                                      | y Efficient FPGA Interconnect                               | 103<br>104                                                                  |

| $\mathbf{A}_{]}$ | 6.1<br>6.2<br>6.3<br>ppen                     | Energy<br>Per-Pa<br>Low-P<br>dices                    | y Efficient FPGA Interconnect                               | 103<br>104<br>105                                                           |

| $\mathbf{A}_{]}$ | 6.1<br>6.2<br>6.3<br>ppen                     | Energy<br>Per-Pa<br>Low-P<br>dices<br>dix A           | y Efficient FPGA Interconnect                               | <ol> <li>103</li> <li>104</li> <li>105</li> <li>107</li> </ol>              |

| $\mathbf{A}_{]}$ | 6.1<br>6.2<br>6.3<br>ppen<br>A.1              | Energy<br>Per-Pa<br>Low-P<br>dices<br>dix A<br>Public | y Efficient FPGA Interconnect                               | <ol> <li>103</li> <li>104</li> <li>105</li> <li>107</li> <li>107</li> </ol> |

# 1 Introduction

## 1.1 Motivation of Low-Power FPGAs

Low-power miniature systems for ubiquitous computing such as wireless sensor networks have been developing rapidly in the past years. The growing demand on collecting and analyzing information from surrounding environment drives researchers and engineers to develop internet of things (IoT). This trend leads to new requirements on integrated circuits. Firstly, due to the potential large number of IoT devices in the future, frequently changing battery for all of them becomes unfeasible. Furthermore, many sensors such as the ones equipped on human or deployed in the environment desire light weight, high portability, and wireless communication ability. All these demands require hardware used in IoT applications to be ultra-low-power (ULP). Secondly, due to the rapidly changing demands and technologies today, these hardware needs computational flexibility for regularly algorithm upgrade or functionality change. Finally, since the cost is potentially high to design sensors using in tons of different applications, low-cost hardware is highly recommended.

Existing hardware solutions for ubiquitous computing include ULP ASICs and ULP microprocessors working in sub-threshold region. However, the development of sub-threshold ASICs for IoT applications is costly and time-consuming due to high design complexity. On the other hand, sub-threshold microprocessors are too power-consuming. FPGAs operating in near/sub-threshold region, flexible and much lower-power than sub-threshold microprocessors, become a highly desired hardware solution for IoT applications. However, comparing to functionality equivalent ASICs, FPGA implementations consume 7x - 14x more power, and 4x slower [4]. This gap makes it not easy for FPGAs to meet energy and performance requirements of IoT applications at the same time. To widely use FPGAs in IoT, energy reduction and energy-efficiency improvement are critical.

## **1.2** Thesis Statement

By scaling the supply voltage down to near/sub-threshold region, optimizing the circuit and architecture of the interconnect fabric, and applying per-path voltage scaling and power-gating to the interconnect, the ULP FPGAs become an energy-efficient hardware solution for IoT devices or other low-power applications that require well-balanced flexibility, cost, and energy-efficiency. The custom tool set and application suite enable fast and effective evaluation of ULP FPGAs.

# 1.3 Goals

The major research goals of this dissertation include:

- Optimize ULP FPGA interconnect circuit, supply voltage, and physical implementation towards maximum energy-efficiency

- Apply per-path voltage scaling and power-gating to the interconnect of ULP FPGAs

- Develop an ULP FPGA evaluation platform (including a low-power application suite, a Verilog synthesis flow, and a fast power estimation flow)

- Enable the tool support of evaluating the effects of using embedded hard IPs on ULP FPGAs

# 2 Background

### 2.1 General FPGA Architecture

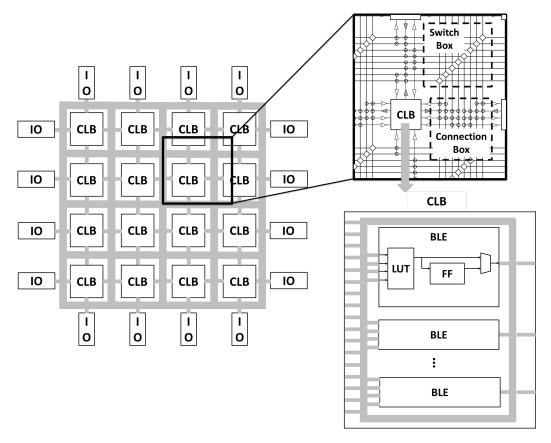

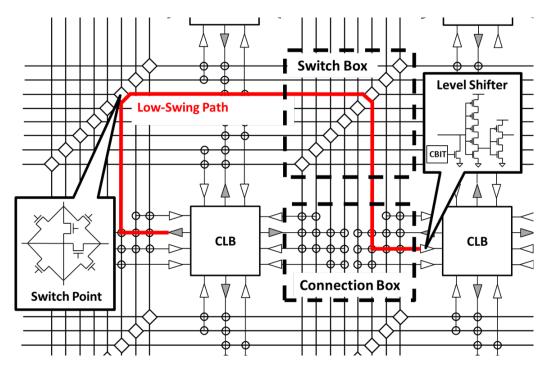

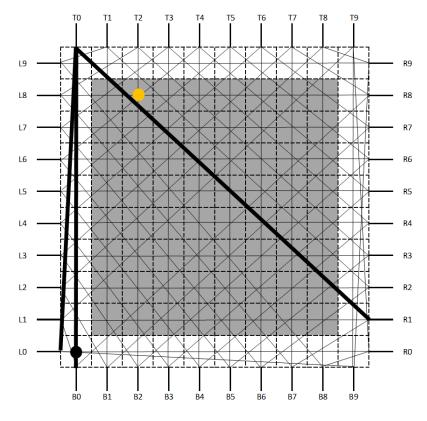

Figure 1: Basic architecture of the core fabric of FPGAs

FPGAs are integrated circuits that can be configured to different logic functions as needed after manufacturer. The basic structure of the core fabric of FPGAs includes Configurable Logic Blocks (CLB), global interconnect, and IO blocks. Each CLB consists of multiple Look-Up-Tables (LUT), Flip-Flops (FF), and multiplexers (MUX), while all CLBs and IO blocks are connected by the global interconnect. By changing the values in configuration bits that distributed all over the FPGA, users can determine the logic function of CLBs, the connectivity pattern between CLBs, and whether the IOs are inputs or outputs.

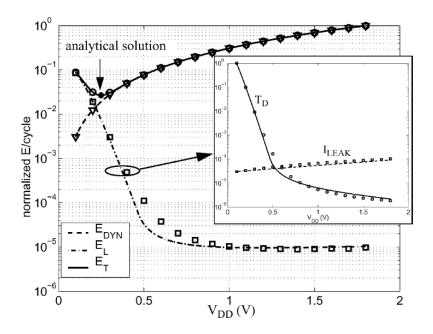

Figure 2: Active energy, leakage energy, and total energy of a FIR filter when sweeping its supply voltage  $V_{DD}$  [5]

The detailed architecture illustrated above is shown in figure 1. There are multiple Basic Logic Elements (BLE) in each CLB. Each BLE includes one LUT, one FF, and one MUX. The output of the LUT is connected to the input of the FF and one of the inputs of the MUX, while the MUX is used to determine whether the BLE is implementing combinational or sequential logic by selecting between the outputs of the LUT and the FF. The BLE outputs are connected to the CLB outputs through buffers. The CLB local interconnect plays a role to help communication between BLEs inside a CLB, by connecting the output of each BLE to the input of other BLEs and providing feed back loops to its own inputs. Also, there are large MUXes placed at the input of each BLE to select the BLE inputs from all the CLB inputs and BLE outputs. The FPGA global interconnect is used to make connections between CLBs and IOs. The multi-track interconnect includes Connection Boxes (CB) and Switch Boxes (SB), where CBs are used to connect CLB inputs and outputs from/to the global interconnect, and SBs are used to route the signals from the original CLB to the destination CLBs. Both CBs and SBs are made of buffers and switches, while configuration bits are connected to these switches. CBs are located at each input/output of the CLBs. By turning on specific switches, the signal can be detected or directed to specific tracks of the global interconnect. This multi-track architecture provides high flexibility of FPGAs. SBs are located at the intersections of vertical tracks and horizontal tracks. By turning on the corresponding switches, signals inside the global interconnect can be directed to the destinations.

## 2.2 Sub-threshold Operation

While many applications today pay more attention to high performance, the ubiquitous computing applications such as wearable sensors require extremely low energy consumption to support long battery life or even energy harvesting technology. Since active energy is quadratically proportional to the supply voltage  $V_{DD}$  at nominal voltage, the method of reducing  $V_{DD}$  is widely used in low-power-oriented designs [6]. Sub-threshold operation is a technique to reduce  $V_{DD}$  to lower than the threshold voltage of transistors. In sub-threshold, current is exponentially proportional to  $V_{DD}$ as shown in (1).

$$I_{subV_T} = I_0 e^{\frac{(V_{GS} - V_T)}{nV_{th}}} \tag{1}$$

Reducing  $V_{DD}$  down to sub-threshold makes it possible to decrease energy consumption to extremely low level. Although active energy reduces with  $V_{DD}$ , the leakage energy increases rapidly in sub-threshold due to the exponentially increased delay. At nominal voltage, leakage energy can be ignored, but becomes the major energy contributor in sub-threshold. Figure 2 shows the energy of a FIR filter when sweeping the supply voltage  $V_{DD}$  [5]. As shown, the lowest-energy-point is reached around 0.25V, where leakage energy and active energy are equal.

Obviously, near/sub-threshold operation is a very effective technique used to reduce energy. Although many works are done in this area, they mainly focus on ASIC and processor designs. FPGAs can also benefit from this technique when designed for ultra-low-power applications.

#### 2.3 Existing Low-Power FPGAs

Researchers and engineers from both commercial and academic fields spend time on developing low-power FPGAs. As the largest FPGA vendors, however, Xilinx and Altera's expertise is more on the high-performance end, and currently have no public products for ultra-low-power applications. Their FPGAs consumes power in the range of 10s of Watts, which is too high for IoT applications. There are also commercial FPGAs designed towards low-power. The Lattice iCE40 [7] has a standby power of 71uW, while the Microsemi IGLOO [8] has a standby power as low as 10uW by using Flash-based configuration bits. However, the power of these products keeps in the range of uW only in sleep mode. When implementing applications, their power raises to several mW. In academic field, [9] presents a 4-CLB FPGA, which consumes as little as 40 w total power. However, this design is too small to implement meaningful low-power applications. In [10], a full FPGA fabric with over 2000 logic blocks, block RAMs, and DSPs is introduced. By using a hierarchical interconnect, this design reduces power by 4x-5x comparing to Xilinx Virtex products, while keeping competitive speed. However, since not targeting at ultra-low-power applications, this design consumes power in the range of several tens of mW, which is too high for IoT.

# 3 Energy Efficient FPGA Interconnect

## 3.1 Motivation

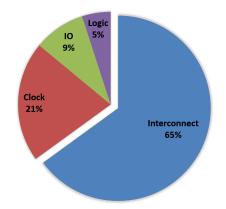

Figure 3: FPGA Core Fabric Energy Breakdown

Interconnect traditionally contributes a big portion of delay and power in circuits. As the size of logic blocks shrinks with technology node scaling, the interconnect cannot scale at the same rate due to physical limitations, such like electromigration and cross-talk. Thus, the interconnect becomes consuming even more delay and power in modern sub-micron electronic systems. In low-power system development, a research focus on reducing interconnect power is crucial.

Unlike interconnect on SoCs and CPUs, FPGA interconnect consists not only wires and buffers, but also tens even hundreds of switches in series along paths with similar amounts of branches. This leads to huge fanout of the drivers and buffers in the interconnect, as well as the capacitance load. In low-power FPGAs, as the supply voltage is low, the capacitance load on the interconnect becomes even more dominant. As shown in figure 3, the specialty of FPGA interconnect makes it contribute 65% or more power of FPGA core fabric, which consists of only CLBs and interconnect [1] [2] [3]. Modern mainstream FPGAs integrated processors, transceivers/receivers, and other high-power hard IPs on chip to support more high-performance applications, such as machine learning, 5G network, data-centers, etc. As a result, the core fabric itself no longer the major power consumer of modern FPGAs on the market, and the interconnect power becomes not as important as before. However, in low-power FPGAs that have no much power budget for hard IPs, reducing interconnect power is still the most effective way to improve the overall FPGA power efficiency.

## 3.2 Prior Art

Researchers reduce FPGA interconnect power in three ways: 1) technology scaling 2) circuit and architecture optimization 3) place and route (P&R) algorithm improvement

All computing platforms benefit from technology node scaling in terms of speed, power, and area. As the dimension of devices shrink to sub-14nm in 2017, the FPGA core fabric power is reduced by hundred even thousands time compared to ten years ago. FinFet and SOI devices also enables ultra-low-power applications by reducing leakage power effectively. However, the emerging low-power applications also bring more and more strict power budget on the hardware. For example, personal health care applications need ultra-long battery-life of the sensors to enable circuit-on-skin. In [11], a self-powered body sensor node SoC is proposed with a full chip power as low as 6.45uW. Other low-power applications have similar power budget on the hardware. FPGAs usually consumes 14x more power compared to ASICs due the design for flexibility [4]. Keeping FPGA power low enough to meet the requirements of health care applications is even harder. In this scenario, simply switching to newer technology node cannot solve the problem. As technology scaling is reaching the physical limit, circuit/architecture/algorithm level low-power techniques are needed to apply to FPGA interconnect at the same time.

Typical circuit and architecture level power reduction techniques include 1) using multi/high- $V_T$  devices 2) using reversed body bias 3) reducing supply voltage 4) inserting power-gating headers. All of these techniques have been applied to FPGA interconnect in exsiting work. Researchers in [12] and [13] exploited multi- $V_T$  scheme, which allowed mixed usage of low and high threshold transistors in routing switches in order to reduce leakage current. In [12], researchers reduced FPGA leakage power by 1.7x - 2.5x by using reversed body bias, a technique of reducing transistor body voltage to increase threshold voltage. In [14], a new FPGA routing switch design that is programmable to operate in three different modes is introduced. In low-power mode, the supply voltage is lowered to just maintain the minimum function requirement, and the leakage power is reduced by up to 52% and active power is reduced by up to 31% comparing to in high-speed mode. Similarly, in [15] and [16], researchers applied a multi- $V_{DD}$  scheme in FPGA interconnect and saved up to 61% of power. However, although these works reduced interconnect power effectively, they are at a high cost of speed degradation. As a result, the power efficiency is not improved.

Another research direction of FPGA interconnect power reduction is P&R algorithms. A smart algorithm can pack logic blocks in a minimum number of CLBs and minimize the total length of global interconnect. The power of FPGAs with shorter interconnect routing wires is much more efficient than FPGAs with long wires. In addition, since better P&R algorithms use less routing resources to implement applications, FPGAs could be made smaller to achieve lower power while still meet the speed requirement. There are many works have been done in this area. In [17], a "path finder" algorithm reduces routing delay by 11x. In [18], the channel width of FPGA interconnect is reduced by 22%. Algorithm level improvement is beyond the scope of this dissertation, but it is important to point out its importance in power reduction.

## 3.3 Low-Swing Interconnect

#### 3.3.1 Overview

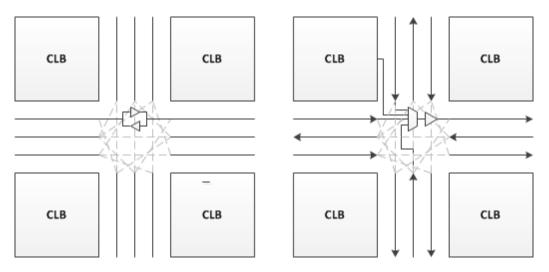

Figure 4: (a) Bi-directional switch box (b) uni-directional switch box

While power is the energy consumption of circuits in unit time, energy itself is a more important metric to evaluate hardware used in battery-life-oriented applications. As discussed in chapter 2, the total energy consists of dynamic energy and leakage energy. The dynamic energy of FPGA interconnect is calculated by

$$Dynamic \quad Energy = C * V_{DD} * VDD_{swing} \tag{2}$$

where C denotes the total lumped capacitance of wires/switches/buffers,  $V_{DD}$  is the main supply voltage on interconnect drivers/buffers, and  $VDD_{swing}$  is the swing of the signal transmitting through the interconnect channel. Typically,  $VDD_{swing}$  has a value equal to  $V_{DD}$ . However, in some special designed circuits, such as the low-swing interconnect that will be discussed in this chapter, their values could be different. To minimize dynamic energy, all of the three terms in the equation need to be minimized as long as the FPGA speed is in the acceptable range given by low-power applications. Reducing supply voltage  $V_{DD}$  to near/sub-threshold region is the most effective method to reduce dynamic energy because of the near quadratic correlation. However, as indicated in figure 2, the leakage energy increases with  $V_{DD}$  decrease, and finally becomes the major portion of system energy. Thus, the value of  $V_{DD}$  needs to be carefully selected to achieve overall minimum FPGA interconnect energy.

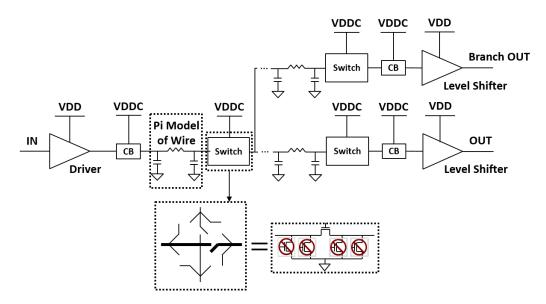

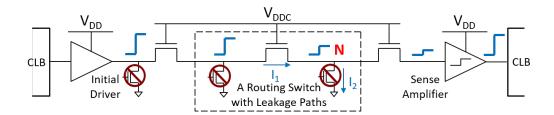

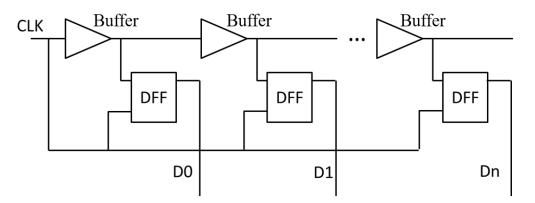

Figure 5: Basic structure of low-swing interconnect

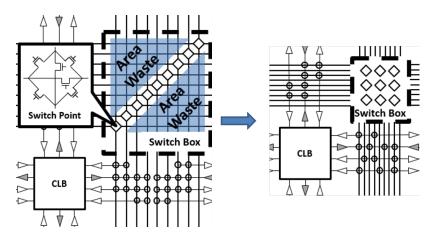

The routing fabric in FPGAs is defined as the electrical connectivity hardware between CLBs. It is comprised of connection boxes that connect CLBs to the routing channel, switch boxes that form the connectivity of routing paths, and wire segments. The traditional bi-directional and uni-directional SBs are shown in figure 4 (a) and (b) respectively. Each bi-directional routing switch is comprised of 2 tri-state buffers, while each unidirectional switch is comprised of an N-input multiplexer followed by

a buffer, where N represents the number of tracks that can connect to the track that this switch drives [19] [20] [21]. As shown in the figure, no matter uni-directional or bi-directional, traditional FPGA interconnect uses multiplexers and buffers to implement routing switches to achieve high speed, but it suffers from high energy cost. Reducing supply voltage for conventional interconnect to near/sub-threshold helps solving this problem. However, since driver and buffer current decreases exponentially in sub-threshold, delay is increased exponentially as well. Although speed is not the major metric for low-power applications, the FPGAs still need to be fast enough to accomplish tasks. Simply upsizing drivers and buffers does not help, since speed depends linearly on device size but exponentially on  $V_{DD}$  in sub-threshold. The low-swing interconnect replaces the multiplexers and buffers structure with passgates [22] [23]. Its basic structure is shown figure 5. This topology reduces "C" by removing buffers. Also, the " $VDD_{swing}$ " is also reduced due to the natural voltage drop across pass-gates. Furthermore, the novel level shifter (developed by Dr. Joseph Ryan) that receives the reduced swing signals at the input to the CLBs reduces delay by detecting the signal earlier in its transition than traditional receivers or level shifters [22] [23].

#### 3.3.2 Delay and Energy Trade-Off

Although the design goal of this FPGA is to meet the requirements of low-power applications, the speed and energy requirements may vary with different applications. The simplest way to obtain this flexibility is to adjust the supply voltage of the FPGA. This means increasing  $V_{DD}$  when higher speed is needed, or decreasing  $V_{DD}$ when a lower power budget is set. However, since speed and energy are very sensitive (quadratic relation) to  $V_{DD}$  change in near/sub-threshold, adjusting  $V_{DD}$  requires highly accurate voltage control, which is not realistic on a small low-power chip. An alternative solution is instead of adjusting the main  $V_{DD}$  of the FPGA, just change the gate voltage of the routing switches in the interconnect. Since the routing switches in low-swing interconnect are pass-gates, changing their gate voltage can adjust the delay and signal swing of the interconnect with the overhead of a separate voltage rail and very small gate leakage energy penalty. Since changing gate voltage does not affect  $V_{DD}$ , but only " $VDD_{swing}$ ", the requirement on voltage control accuracy is dramatically reduced. This idea will be further discussed later in this chapter.

#### 3.3.3 Applicable Conditions of the Low-Swing Interconnect

Although the low-swing design reduces interconnect energy effectively, the benefit is achieved with a price on reduced robustness. Since the signal swing is too small, the PVT variations and voltage/ground noises can easily make a logic high signal to logic low, especially in near/sub-threshold where  $V_{DD}$  is small. Thus, the low-swing interconnect is suitable for high performance systems with a need of power saving or ultra-low-power systems with signal degradation solutions, while will be discussed later in this chapter.

#### 3.4 Interconnect Modeling

#### 3.4.1 Overview

To implement meaningful applications, a low-power FPGA should include a large number of CLBs and a wide interconnect channel built with over a hundred of tracks. Simulating such a large system for only one cycle can take from tens of hours to several days. To make things worse, sweeping circuit parameters towards minimum energy and lower variation requires hundred/thousand times of runs in the design phase. All the subsequent work such as chip tapeouts need to pulse for months to wait the simulation results to be done. This is unreasonable and unacceptable. Thus, a circuit model of the low-swing interconnect is needed for design purpose. This model should be accurate enough to represent the complicated environment of the interconnect, and also should be simple enough to finish simulations in short time.

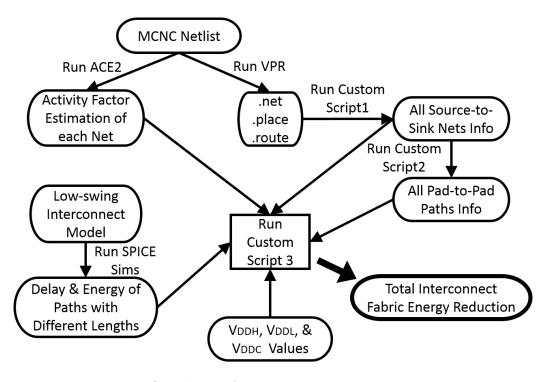

Figure 6: Diagram of the global interconnect path model

The architecture of low-swing interconnect has been shown in figure 5. As mentioned earlier in this chapter, a FPGA interconnect path is defined as the circuit starting from the driver at an output of a CLB, passing CBs and switches, then ending at a level shifter of the destination CLB. The function of level shifter is to regenerate the signal to full swing to avoid short-circuit current in the destination CLB as well as improving noise margin. Figure 6 shows the diagram of the abstraction of figure 5, which is the interconnect model used in this work. Each wire segment is modeled as a Pi structure to represent the highly capacitive long wires. Each routing switch is modeled as one turned-on switch and four turned-off switches connected to ground, representing the signal path and the leakage paths respectively. Each CB is modeled as a multiplexer. A separate  $V_{DDC}$  voltage is applied to routing switches and CBs by high- $V_T$  config bits to provide flexibility in delay and energy. Level shifters can be inserted either between two switches when regeneration is needed or at the end of a path. Branches are added based on the path distribution analysis. To optimize the circuit, parameters including the value of  $V_{DD}$ ,  $V_{DDC}$ , the topology and size of CBs and switches, and the number of inserted level shifters will be varied and the corresponding influence on energy efficiency will be evaluated and discussed in the remaining part of this chapter.

#### 3.4.2 Path Length and Branch Distribution

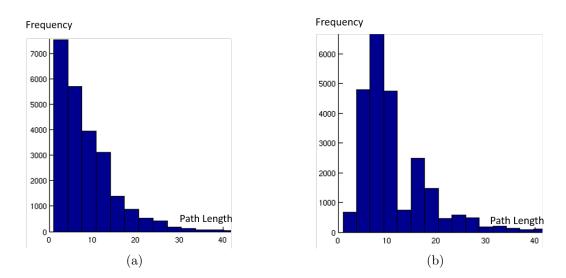

Figure 7: Path length distribution (a) segment length = 1 (b) segment length = 4

The length of an interconnect path in this dissertation is defined as the number of routing switch on the path from the origin CLB to the destination CLB. The length of paths varies from 1 to over 80 and is not equally distributed. To optimize the interconnect circuit, we ideally want to look at all interconnect paths when implementing all target applications. However, doing so is too time consuming and does not necessary. We can archive a near-optimal design by looking into a carefully selected collection of interconnect paths that can represent the majority scenarios. Since the optimal circuit of the interconnect highly depends on the length of the paths, we firstly need to set a range of path length to aim at.

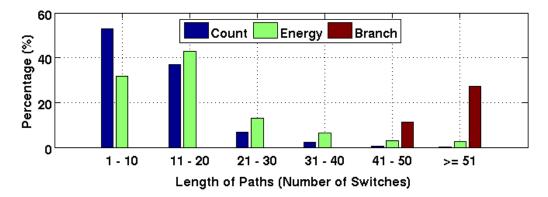

Figure 8: Abstracted Path and branch distribution

The path length distribution depends on the FPGA architecture, the P&R tool, and the benchmarks selected to map to the FPGA. In this chapter, an open source FPGA P&R tool called VTR [24] is used to run a general-accepted Microelectronics Center of North Carolina (MCNC) benchmark suite [25] to investigate the FPGA path distribution. A basic FPGA architecture, which has a logic cluster size of 8 and a look-up-table input number of 4, is selected as the target fabric to map the benchmarks. The path length distribution is shown in Fig. 7. For some express interconnect wires, the routing switch does not appear at every horizontal and vertical track intersections. The number of intersections they skipped affects the path length. To obtain a comprehensive path length distribution that considers all the cases, Fig. 7 shows two histograms present different segment lengths accordingly, which represent the number of CLBs each wire segment spans without routing switches in the middle. As a result, the histograms indicate no matter which architecture is used, the majority of paths are less than 40 routing switches. However, while most of the paths are less than 5 when segment length equal to 1, the length of most paths is around 10 when segment length is 4. This is because longer segment is harder to route to adjacent logic blocks when the applications are small and compact, especially for low-power applications.

| Benchmark | Total Switch | Length of    | Average     |

|-----------|--------------|--------------|-------------|

| вепсптагк | Count        | Longest Path | Path Length |

| alu4      | 8078         | 41           | 7.06        |

| apex2     | 11459        | 24           | 5.98        |

| apex4     | 8039         | 24           | 6.53        |

| bigkey    | 6191         | 19           | 4.48        |

| clma      | 68031        | 53           | 8.87        |

| des       | 8327         | 27           | 5.85        |

| diffeq    | 6734         | 34           | 5.14        |

| dsip      | 5944         | 19           | 5.92        |

| elliptic  | 21405        | 44           | 7.37        |

| ex5p      | 7313         | 25           | 6.68        |

| ex1010    | 32109        | 50           | 6.80        |

| frisc     | 26985        | 54           | 9.12        |

| misex     | 7624         | 21           | 5.87        |

| pdc       | 41282        | 39           | 9.14        |

| s298      | 7075         | 25           | 6.06        |

| s38417    | 29246        | 62           | 5.77        |

| s38584.1  | 31219        | 68           | 6.22        |

| seq       | 10867        | 25           | 6.53        |

| spla      | 27362        | 42           | 7.73        |

| tseng     | 3667         | 22           | 4.36        |

| Average   | 18448        | 36           | 6.57        |

| Largest   | 68031        | 68           | 9.14        |

Figure 9: Details of path distribution of MCNC benchmarks

The path length distribution cannot represent the energy distribution. Although most of the paths are short (less than 10), the longer paths consume much higher energy. As energy linearly depends on the total capacitance in the interconnect, the branch distribution is also worth to look at. In Fig. 8, the path length, energy and branch distributions are all shown in one plot for comparison. In the plot, paths are divided into 6 categories based on path length. The blue and green bars represent the path count distribution and the energy distribution. The red bar represents the average percentage of switches from the path that fall on branches rather than the main path. As indicated in Fig. 8, paths shorter than length 40 take about 98% of the total path count and consume about 94% of the total global interconnect energy. Although branches are very common in the FPGA interconnect network, there are few branches on paths shorter than 40. Such analysis indicates that in order to increase energy efficiency of FPGA interconnect, circuit level optimization should mainly focus on paths shorter than 40 without branches. However, the results highly depend on how the P&R tool operates. For that reason, paths less than 68 are all considered in this chapter. The details of path distribution of the largest 20 MCNC benchmarks are shown in Fig. 9.

| Technology | Metal Layer | Segment Length | Wire Length (um) | Total C/Segment<br>(fF) | Total R/Segment<br>(Ohm) |

|------------|-------------|----------------|------------------|-------------------------|--------------------------|

|            |             | 1              | 250              | 65.5                    | 129.5                    |

|            | M1          | 2              | 500              | 131.0                   | 259.0                    |

|            |             | 4              | 1000             | 261.9                   | 518.0                    |

|            |             | 1              | 250              | 58.5                    | 80.0                     |

|            | M2          | 2              | 500              | 117.1                   | 160.0                    |

|            |             | 4              | 1000             | 234.1                   | 320.0                    |

|            |             | 1              | 250              | 58.5                    | 80.0                     |

| IBM130     | M3          | 2              | 500              | 117.1                   | 160.0                    |

|            |             | 4              | 1000             | 234.1                   | 320.0                    |

|            |             | 1              | 250              | 41.0                    | 26.3                     |

|            | M4          | 2              | 500              | 107.0                   | 52.5                     |

|            |             | 4              | 1000             | 213.9                   | 105.0                    |

|            |             | 1              | 250              | 41.0                    | 26.3                     |

|            | M5          | 2              | 500              | 107.0                   | 52.5                     |

|            |             | 4              | 1000             | 213.9                   | 105.0                    |

|            | M1          | 1              | 80               | 19.2                    | 628.8                    |

|            |             | 2              | 160              | 38.4                    | 2515.2                   |

|            |             | 4              | 320              | 76.8                    | 10060.8                  |

|            | M2          | 1              | 80               | 18.4                    | 629.6                    |

|            |             | 2              | 160              | 36.8                    | 2518.4                   |

|            |             | 4              | 320              | 73.6                    | 10073.6                  |

|            |             | 1              | 80               | 18.4                    | 629.6                    |

| IBM32SOI   | M3          | 2              | 160              | 36.8                    | 2518.4                   |

|            |             | 4              | 320              | 73.6                    | 10073.6                  |

|            |             | 1              | 80               | 18.4                    | 629.6                    |

|            | M4          | 2              | 160              | 36.8                    | 2518.4                   |

|            |             | 4              | 320              | 73.6                    | 10073.6                  |

|            |             | 1              | 80               | 17.6                    | 629.6                    |

|            | M5          | 2              | 160              | 35.2                    | 2518.4                   |

|            |             | 4              | 320              | 70.4                    | 10073.6                  |

#### 3.4.3 Detailed Circuit Modeling

Figure 10: Table of the Equivalent Capacitance and Resistance of a Wire Segment

The interconnect model is built from a combination of five element sub-circuits: driver, level shifter, wire segment, routing switch, connection box.

Figure 11: Total Capacitance of Wire Segments in a 84-Track Channel

Both the driver and level shifter are modeled as two cascade inverters. However, both inverters in the driver are standard structure with one PMOS and NMOS that have same driving strength, while the level shifter is built of one strong-NMOS interver followed by a strong-PMOS inverter taking advantage of stack effect. The purpose of this design is to detect small signal swings without speed overhead [22] [23]. In this dissertation, the same structure of this level shifter is used with modifications on sizing, and its schematic can be found in Fig. 5. Since the driver locates at the very beginning of interconnect paths, its input signal is always at full swing, so using a basic inverter-based design is fine and can save area. The size optimization of the driver will be discussed in the following contents of this chapter.

Figure 12: Routing Switch Modeling

To model the wire segments, either Pi model or T model can be used. Since both models have equivalent total capacitance/resistance values and no additional circuit parts between adjacent routing switches, either model works for this research. In this dissertation, the Pi model is selected. Three factors affect the value of R and C in the wire model: 1) the length of each wire segment 2) the metal layer used for routing in physical implementation 3) the coupling capacitance between wires in the same channel. As will be explained in 3.7, the length of each wire segment is 250um (segment length = 1)/500um (segment length =2)/1000um (segment length =4) in 130nm CMOS. Based on this, the equivalent capacitance and resistance values of wires implemented by each metal layer in both 130nm CMOS and 32nm SOI technologies are estimated and shown in Fig. 10. The RC values are calculated by reading from the PDK user manuals, then verified in the Cadence Virtuoso parasitic extraction environment. Since the interconnect channel includes a bundle of tens of tracks in parallel close to each other, the coupling capacitors between adjacent tracks can't be ignored. Fig. 11 shows the total capacitance of each track in an interconnect channel. The tracks in the middle have much higher capacitance compared to those at the edge of the channel.

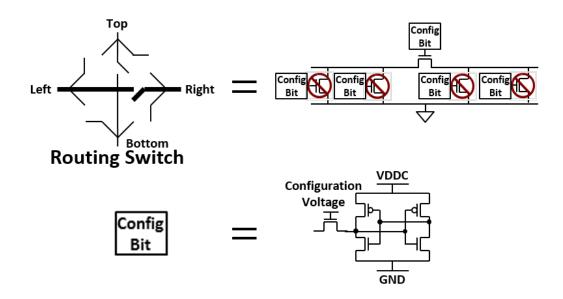

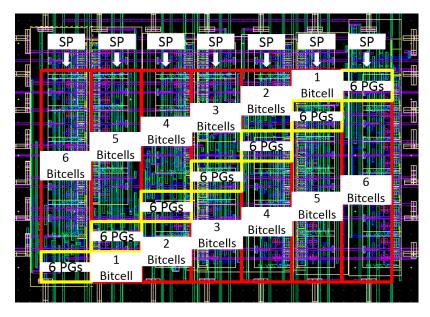

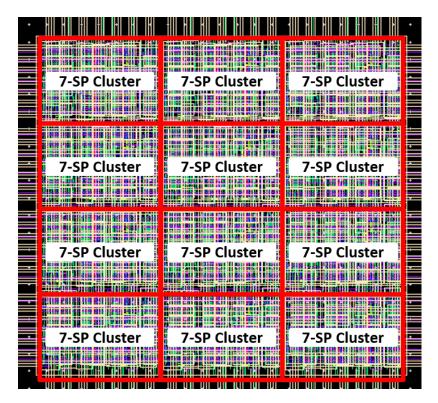

Both the routing switch and connection box are built with pure pass-gates and configuration bit-cells. While the connection box structure is one of the knobs in this research and will be discussed later, the circuit model of the routing switch is shown in Fig. 12. Each routing switch includes six pass-gates to provide potential connectivity of all four directions: Left-to-Right, Left-to-Top, Left-to-Bottom, Rightto-Top, Right-to-Bottom, and Top-to-Bottom. In the case of no branch in a path, one pass-gate will be turned on, four pass-gates will be turned off creating leakage paths, and the last pass-gate is not related to the example path. For example, if a signal is transmitted from left to right in Fig. 12, the Top-to-Bottom pass-gate is unrelated. In FPGA interconnect, if a switch is turned off, a floating net might be created and causes short-circuit current. To avoid this situation, all potential floating nets will be either pull up to  $V_{DD}$  or pull down to ground. In this research, ground is selected as the default. For the reasons described above, the routing switch model is a pass-gate with 4 parallel turned-off pass-gates to ground. The voltage to the passgates are not directly given by supplies, but through a configuration bit made of a 5T SRAM bit-cell. Since these memory cells are not in an array and are configured once without value changes thereafter, 6T or more complicated structures are unnecessary and minimum size high-VT transistors are used to minimize leakage.

## 3.5 Circuit and Supply Voltage Optimization

#### 3.5.1 Overview

The goal of this research is to improve the energy efficiency of the interconnect while maintaining the robustness of it at a certain level. This goal results in many circuit design trade-offs. For example, the requirement of high energy efficiency indicated both low energy/operation and adequate speed. To reduce energy, we can 1) reduce transistor size of routing switches/CBs/drivers 2) decrease  $V_{DD}/V_{DDC}$  3) using transmission-gates instead of pass-gates to implement routing switches. However, all of these methods decrease system speed, which is already very low in near/subthreshold. There is a sweet point to balance speed and energy for each design knob. The energy-delay-product (EDP) and the energy-delay (ED) curve of the interconnect are widely used metrics to evaluate energy efficiency of circuits, and are also used in this research. Another trade-off example is about circuit robustness. While reducing  $V_{DDC}$  or using smaller size of pass-gates decreases energy, the signal swing is also decreased and worsen robustness. All of these trade-offs are explored and explained in this chapter.

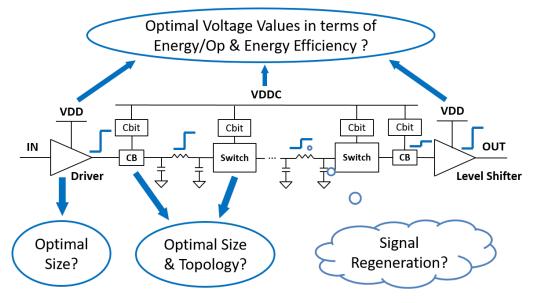

Figure 13: Knobs of Interconnect Optimization

# 3.5.2 Supply Voltage Optimization

Supply voltage  $V_{DD}$  is a dominant knob for EDP. There are three components contributing to EDP: delay, active energy, and leakage energy.  $V_{DD}$  affects all of the

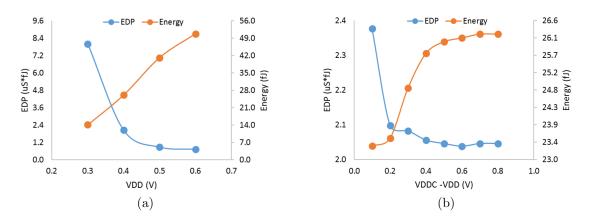

important parameters for energy efficient FPGAs. Path delay decreases exponentially in sub-threshold, while it only decreases quadratically in the above-threshold region. Energy is lower in the sub-threshold region and is dominated by leakage energy, while dynamic energy, which decreases quadratically with  $V_{DD}$ , dominates total energy for above-threshold operation [26]. In this research,  $V_{DD}$  is swept from 0.3V to 0.6V for paths with length of 5, 10, 20, and 40.  $V_{DDC}$  is swept from 0 to 0.8V above  $V_{DD}$ . The minimum EDP is obtained at  $V_{DD} = 0.5$ V. Increasing  $V_{DD}$  from 0.5V to higher cannot further decrease EDP, but increases energy. On the other hand, reducing  $V_{DD}$  to 0.4V is very beneficial when energy is more important than energy efficiency, because much smaller energy can be achieved with small EDP overhead. However, reducing  $V_{DD}$  to 0.3V results in rapidly increased EDP but relatively smaller energy reduction. This conclusion applies to path with a length of 5, 10, 20, and 40 indicating it is a general conclusion for the majority of paths involved in MCNC benchmark routing.

Figure 14: The layout photo of the characterization chip

Besides  $V_{DD}$ , energy and delay also depend on  $V_{DDC}$ . As explained earlier, the dynamic energy of a path equals to  $C^*V_{DD}^*VDD_{swing}$ . For smaller  $V_{DDC}$ , the equivalent resistance of switches is large due to sub-threshold operation. Larger resistance leads to increased voltage drop and decreased signal swing. Consequently, dynamic energy and speed are both low. Applying a higher  $V_{DDC}$ , on the other hand, results in higher dynamic energy but substantially reduced delay. As a result, the delay decreases sharply as  $V_{DDC}$  increases in the range of  $V_{DD} \leq V_{DDC} \leq V_{DD} + 0.2V$ . Keeping increasing  $V_{DDC}$  to above  $V_{DD} + 0.2V$  can no longer reduce delay as significantly as before. On the other hand, energy increases slowly as  $V_{DDC}$  increases when  $V_{DD} \leq V_{DDC} \leq V_{DD} + 0.2V$ , while it experiences a much faster increase when  $V_{DDC} \geq V_{DD} + 0.2V$ . Similar to delay, the EDP decreases sharply at low  $V_{DDC}$  and slowly at high  $V_{DDC}$ . This transition point is discovered at 0.2V higher than  $V_{DD}$ . However, this value varies with path length. It can reach 0.3V above  $V_{DD}$  for paths longer than 40 and 0.1V for paths shorter than 10.

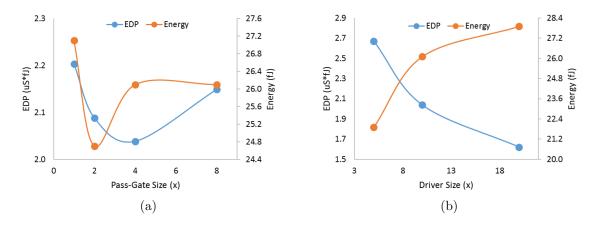

Figure 15: Measurement results of the energy and EDP of a path when sweeping (a)  $V_{DD}$  (b) and  $V_{DDC}$  in 130nm CMOS (Path Length = 10)

To verify the above conclusions, a chip is designed to implement eight low-swing FPGA interconnect meshes with different circuit topology (pass-gates/transmission-gates) and transistor sizes (1x, 2x, 4x, and 8x) of routing switches in 130nm CMOS.

Each mesh is a 10-by-10 routing switch structure interconnected by wire segments, which are intentionally inserted between switches to imitate the RC of long wires in real FPGA fabrics. The meshes are driven by a driver block on the die. The driver block comprises drivers with different sizes followed by connection boxes that can be configured to be turned on or off. The annotated layout of the test chip is shown in Fig. 14. Each mesh on the chip is configured to signal paths with all branches and leakage paths. The measured normalized energy and EDP when sweeping  $V_{DD}$ and  $V_{DDC}$  are shown on the left and right plot respectively in Fig. 15. The chip measurement results indicate conclusions the same as simulation. This chip will be used again in circuit optimization later in this chapter.

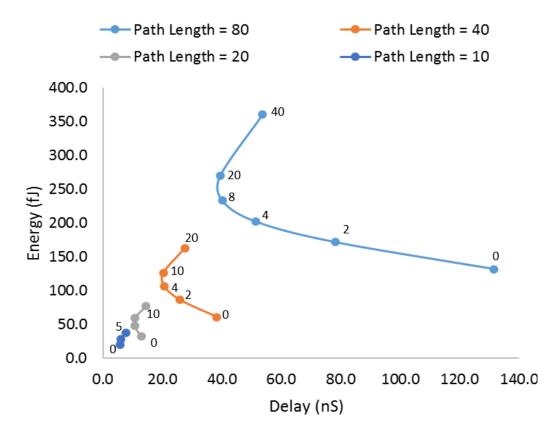

Figure 16: ED curves of interconnect paths at different  $V_{DD}$  in 32nm SOI (path length = 40)

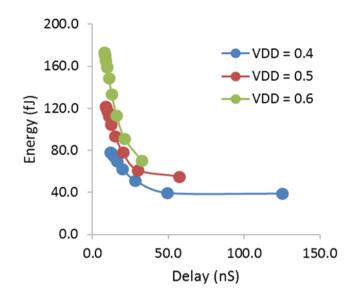

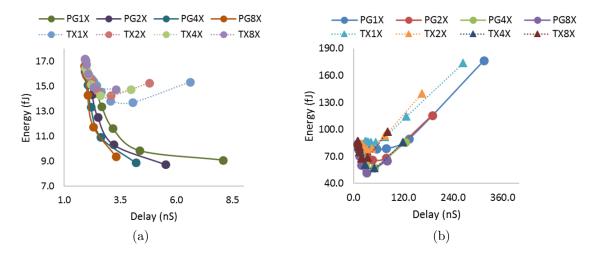

In case the conclusions above vary from technology to technology, I also ran the same simulations in 32nm SOI, which is a more advanced technology in leakage reduction. Fig. 16 shows the ED curves of two paths (left: length 5; right: length 40) at different  $V_{DD}$  by sweeping  $V_{DDC}$  from the right end of each curve to its left end.

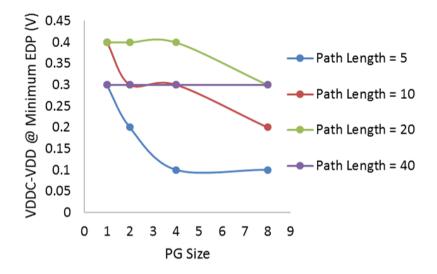

On the way of sweeping  $V_{DDC}$ , there is always a combination of delay and energy on the ED curve results in the lowest EDP. Higher  $V_{DD}$  always leads to higher energy, while usually leads to smaller delay. However, for paths longer than 40, path delay at different  $V_{DD}$  are almost same. Thus, using a lower  $V_{DD}$  for higher energy efficiency is recommended. In Fig. 17, the  $V_{DDC}$ - $V_{DD}$  values lead to these minimum EDPs are also shown. The optimal  $V_{DDC}$  values decrease as the size of pass-gates increases for all paths. Furthermore, the optimal  $V_{DDC}$  values for longer paths are higher than shorter paths. To be more specific, when using 4x pass-gates as the routing switches, the optimal value of  $V_{DDC}$  is 0.1V higher than  $V_{DD}$  for paths with length of 5, and is 0.3 0.4V higher than  $V_{DD}$  for longer paths.

Figure 17: The optimal  $V_{DDC}$  value results in minimum EDP of interconnect paths with different lengths in 32nm SOI @  $V_{DD}=0.4$ V

In near/sub-threshold operations, the process variation is significant. Fig. 18 shows the average delay and the standard deviation of a length 10 path at different voltages. The data was obtained by running Monte Carlo simulation in both 130nm CMOS and 32nm SOI technology nodes. The variation is estimated by  $\sigma/\mu$ . As a result, the 32nm SOI is better in reducing variation in general. Variation in 32nm SOI is only have of that in 130nm CMOS. For each technology node, increasing  $V_{DDC}$  effectively reduces variation when  $V_{DDC}$  is low. When 0.3V higher than  $V_{DD}$ , keep increasing  $V_{DDC}$  does not reducing variation further. On the other hand, increasing  $V_{DD}$  always reduces variation in near/sub-threshold.

|         | VDDC - VDD (V) | 130nm CMOS | 32nm SOI |

|---------|----------------|------------|----------|

| VDD (V) |                | σ/μ        | σ/μ      |

|         | 0.1            | 0.48       | 0.21     |

|         | 0.2            | 0.38       | 0.17     |

|         | 0.3            | 0.35       | 0.17     |

| 0.4     | 0.4            | 0.34       | 0.18     |

| 0.4     | 0.5            | 0.34       | 0.18     |

|         | 0.6            | 0.34       | 0.19     |

|         | 0.7            | 0.35       | 0.19     |

|         | 0.8            | 0.35       | 0.19     |

| 0.4     |                | 0.38       | 0.17     |

| 0.5     | 0.2            | 0.30       | 0.12     |

| 0.6     |                | 0.20       | 0.10     |

Figure 18: The process variation of paths at different voltage

# 3.5.3 Circuit Optimization

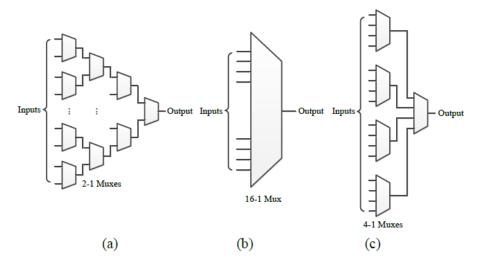

Figure 19: Schematic of different CB topologies: (a) full multiplexer (b) 1-stage multiplexer (c) 2-stage multiplexer

In this section, circuit optimization is performed on 1) connection box topology 2) routing switch implementation topology 3) routing switch transistor sizing 4) driver transistor sizing.

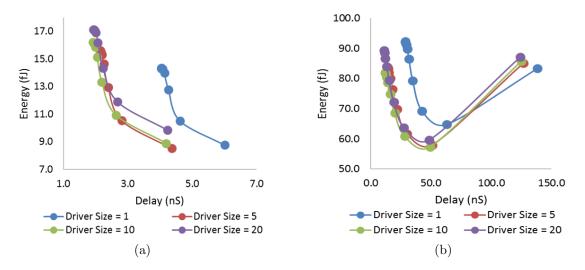

The connection boxes in FPGAs targeting at high performance operations are implemented by multiplexers with buffers to make connections between the routing fabric and the CLBs. In this research, the buffers are removed for low-power operations. According to SPICE simulation results, the connection boxes contribute 13.4%of total delay and 2.6% of total energy to a low-swing path. Only removing the buffers from the existing connection boxes without re-sizing and revisiting typologies results in un-minimized delay and energy. Fig. 19 shows three candidate connection box topologies for near/sub-threshold operations. The 1-stage design has the smallest delay because it adds only one transistor delay to the interconnect path. However, the capacitance load of this design is the sum of all drain/source capacitance of N transistors, where N represents the number of inputs of the multiplexer. In addition, the signal swing is also large. As a result, the 1-stage design suffers from high energy. In contrast, the full multiplexer benefits from both low active and leakage energy, but suffers from slow speed. Both of the two designs cannot guarantee the maximum energy efficiency in sub-threshold. The 2-stage multiplexer is a good alternative to balance energy and delay. The simulation result shows that the delay of the 2-stage multiplexer is 16% smaller than the full multiplexer, while the energy of the 2-stage multiplexer is 5% lower than the 1-stage design. In addition, the 2-stage design has the smallest variation among the 3 candidates. The overhead of using a 2- stage design is area (2.6x larger than a full multiplexer when N = 40). Considering energy efficiency and variation, the 2-stage design is optimal. This conclusion applies to paths with length of 5, 10, 20, and 40.

Since no buffers in the routing switches, drivers are the only consumer of the

dynamic energy in low-swing interconnect. To achieve low energy, large drivers are not acceptable. However, simply reducing energy by decreasing driver size as much as possible is also not a good choice when delay is already large in the sub-threshold region. Under these circumstances, finding a driver size to balance energy and delay becomes a problem. As a result, increasing the size of drivers from 5x to 20x reduces delay by 55% with a 39% energy overhead. This result implies that a larger driver may result in a smaller EDP.

Figure 20: Measured energy and EDP of paths with varying (a) switch size (b) driver size (a)  $V_{DD}=0.4$ V in 130nm CMOS (Path Length = 10)