## Rethinking the Architecture of Warehouse-Scale Computers

#### A Dissertation

#### Presented to

In Partial Fulfillment of the requirements for the Degree Doctor of Philosophy

Computer Science

by

**Jason Mars**

May 2012

### Approvals

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

Jason Mars Approved: Him Hazelwood Mary Lou Soffa (Advisor) Kim Hazelwood (Chair) David August

Jack Davidson

John Lach

Accepted by the School of Engineering and Applied Science:

Dean, School of Engineering and Applied Science

#### Abstract

As the world's computation continues to move into the massive datacenter infrastructures recently coined as "warehouse-scale computers" (WSCs), developing highly efficient systems for these computing platforms has become increasingly critical.

The architecture of modern WSCs remains in its relative infancy. In designing modern WSCs, architects start with commodity off-the-shelf components including commodity processors and open source system software components. These components are then stitched together to design a simple and cost effective WSC. While this approach has been effective for producing systems that are functional and can scale the delivery of web-services as demand increases, efficiency has suffered. The commodity components and system software used have not been designed and refined with the unique characteristics of WSCs in mind, and these characteristics may be critical for a highly efficient WSC design. As such, we must rethink the architecture of modern WSCs.

This dissertation argues that one such characteristic has been overlooked: the diversity in execution environments in modern WSCs. We define a given task's execution environment as the coupling of the machine configuration and the co-running tasks simultaneously executing alongside the given task. At any given time in a WSC, we have a high degree of diversity across these execution environments. This dissertation argues that acknowledging, exploiting, and adapting to the diversity in execution environments are critical for the design of a highly efficient WSC. When ignoring this diversity, three critical design problems arise, including 1) the homogeneous assumption, where all machines and cores in a WSC are assumed to be equal and managed accordingly, 2) the rigidness of applications, where application binaries can not adapt to changes across and within execution environments, and 3) the oblivion of interference, where interference between tasks within an execution

environment can not be measured or managed.

This dissertation addresses each of these three design problems. First, we address the homogeneous assumption at the cluster level by redesigning the task manager in the WSC to learn which execution environments tasks prefer and map them accordingly. Second, we address the rigidness of applications at the machine level by providing a mechanism to allow applications to adapt to their execution environment, then leverage this mechanism to solve pressing problems in WSCs. Lastly, we address the oblivion of interference at both the cluster and machine levels by providing novel metrics and techniques for measuring and managing interference to improve the utilization of WSCs.

By incorporating an awareness of the diversity in execution environments in these three key design areas, we produce a WSC design that is significantly more efficient in both the performance of the applications that live in this domain and the utilization of compute resources in the WSC. By improving efficiency for these two metrics, we effectively require a smaller WSC for some fixed workload, which has implications on reducing not only the cost of these systems, but also their environmental footprint.

## Acknowledgements

My life has been impacted by a number of extraordinary people. Where does one begin?

First and foremost, I would like to thank Mary Lou Soffa for being one of the most important people in my life. Her contribution to me as a person goes beyond our professional relationship. She has been a second mother, wise teacher, and dear friend to me through the 10 years I have known her. She was the first mentor of mine to believe in me and see real talent and potential, when most would have ruled me out. I could never thank her enough for the impact she's had on my life.

I'd also like to thank Robert Hundt, whom I met during my first internship at Google. Robert is one of the most amazing and rare people I know. He has been a close mentor and friend of mine. I have absorbed a great amount of wisdom and knowledge from him. Not just technical knowledge, but also how to challenge myself to have the courage to persue goals that others may talk themselves out of. I look forward to a life-long friendship with him.

Naveen Kumar was my first research colleague. Now he is one of my closest friends. I met him as a sophomore immediately after joining Mary Lou Soffa's group at the University of Pittsburgh. I thank him for taking an interest in me early on and teaching me the ropes. I also thank him for being there for me every moment since meeting him, and I look forward to an epic future of collaborating on world class research.

I also would like to thank my wife, Lingjia Tang, who has been a positive and extraordinary force in my life in every way imaginable. When we are together, we are not additive, we are multiplicative. No, we are exponential... power set of R... second order power set of R cross R... you get my point. Like the song says, "I'm a movement by myself, but I'm a force when we're together..." My best friends Songbin Gong, Christian Lim, and Jevan Shanghai, in no particular order, has been there for me all along the way, and I cannot word how important that has been for my overall happiness and well being. Thanks you guys. I have a true bromance with each one of you.

My mom, Joan Mars, dad, Perry Mars, and brother Perry Mars Jr., has been a major source of inspiration to me and key for helping me maintain my sanity. Their reminders that I need to sleep, eat the right foods, and not over exert myself, has been critical in my not self-destructing. One of the biggest rewards of accomplishing this piece of work is in making them proud. I love you mom, dad, and bro!

Other major influences in my life I'd like to thank include, but is not limited to, Dick Sites, Kunle Olukotun, David August, Neil Vachharajani, Vijay Reddi, Kevin Skadron, Kim Hazelwood, Sudhanva Gurumurthi, Tao Xie, Jing Yang, Davidson Young, all of my graduate colleagues I chat with on a regular basis, and many others. I would also like to thank my committee and those mystery people at Google who have supported my career along the way. THANK YOU ALL!

## Contents

| 1 | Int | roduct | tion                                                  | 1  |

|---|-----|--------|-------------------------------------------------------|----|

|   | 1.1 | Ramp   | ant Inefficiency in WSCs                              | 2  |

|   | 1.2 | Divers | sity of Execution Environment in WSCs                 | 4  |

|   | 1.3 | Three  | Design Problems                                       | 5  |

|   |     | 1.3.1  | The Homogeneous Assumption                            | 6  |

|   |     | 1.3.2  | Rigidness of Applications                             | 7  |

|   |     | 1.3.3  | The Oblivion of Interference                          | 8  |

|   | 1.4 | Summ   | nary of Contributions                                 | 10 |

|   |     | 1.4.1  | Analyzing EE Diversity in Production WSCs             | 10 |

|   |     | 1.4.2  | Intelligently Mapping Jobs at the Cluster Level       | 10 |

|   |     | 1.4.3  | Online Adaptation at the Machine Level                | 11 |

|   |     | 1.4.4  | Mitigating Interference at Cluster and Machine Levels | 12 |

| 2 | Ba  | ckgrou | and Related Work                                      | 14 |

|   | 2.1 | Task I | Placement in Modern WSCs                              | 14 |

|   | 2.2 | Qualit | ty of Service                                         | 15 |

|   | 2.3 | Co-loc | cation                                                | 15 |

|   | 2.4 | QoS F  | Elexibility                                           | 16 |

|   | 2.5 | Relate | ed Work                                               | 16 |

| 3 | Ex  | ecutio | n Environments in WSCs                                | 23 |

|   | 3.1 | Divers | sity in Execution Environments                        | 24 |

|   |     | 3 1 1  | WSC Test Platform                                     | 24 |

|   |                        | 3.1.2  | Microarchitectural Diversity           | 25 |

|---|------------------------|--------|----------------------------------------|----|

|   |                        | 3.1.3  | Co-Runner Diversity                    | 26 |

|   |                        | 3.1.4  | Motivation for Intelligent Mapping     | 28 |

|   |                        | 3.1.5  | Benchmark Testbed                      | 28 |

|   |                        | 3.1.6  | Implications on WSC Design             | 30 |

|   | 3.2                    | An Op  | pportunity Metric for EE Diversity     | 30 |

| 4 | Ma                     | apping | Jobs to Diverse Execution Environments | 32 |

|   | 4.1                    | Oppor  | rtunistic Mapping with SmartyMap       | 33 |

|   |                        | 4.1.1  | Overview of SmartyMap                  | 33 |

|   |                        | 4.1.2  | Mapping an Optimization Problem        | 34 |

|   |                        | 4.1.3  | Map Scoring                            | 36 |

|   | 4.2                    | The B  | Benefit of SmartyMap                   | 37 |

|   |                        | 4.2.1  | Goals and Methodology                  | 38 |

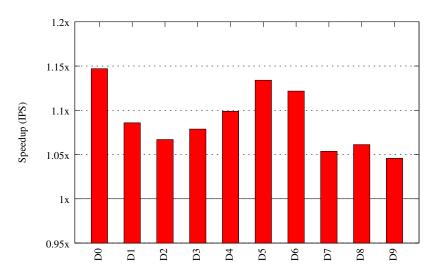

|   |                        | 4.2.2  | Overall IPS                            | 39 |

|   |                        | 4.2.3  | Latency                                | 41 |

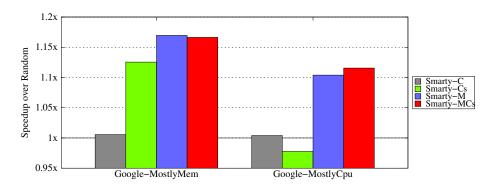

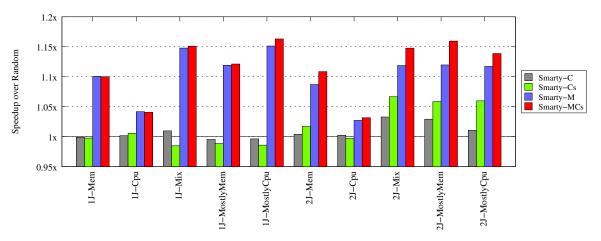

|   |                        | 4.2.4  | Impact at the Application-level        | 42 |

|   |                        | 4.2.5  | SmartyMap in the Wild                  | 45 |

|   | 4.3                    | Factor | rs Impacting EE Diversity              | 46 |

|   |                        | 4.3.1  | Impact of Workload Mix on EE Diversity | 47 |

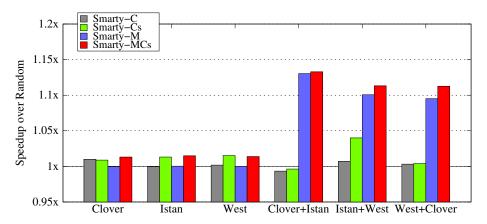

|   |                        | 4.3.2  | Impact of Machine Mix on EE Diversity  | 50 |

|   |                        | 4.3.3  | Which Servers to Purchase?             | 52 |

|   |                        | 4.3.4  | Revisiting Map Scoring                 | 53 |

| 5 | $\mathbf{A}\mathbf{d}$ | aptati | on For Diverse Execution Environments  | 55 |

|   | 5.1                    | A Med  | chanism for Online Adaptation in WSCs  | 56 |

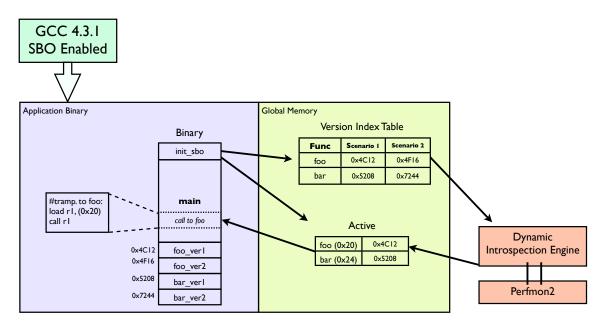

|   |                        | 5.1.1  | An Overview of Loaf                    | 57 |

|   |                        | 5.1.2  | Online Monitoring                      | 59 |

|   |                        | 5.1.3  | Adapting the Application               | 61 |

|   |                        | 5.1.4  | Adapting the Environment               | 65 |

|   |                        | 5.1.5  | Leveraging Loaf                        | 65 |

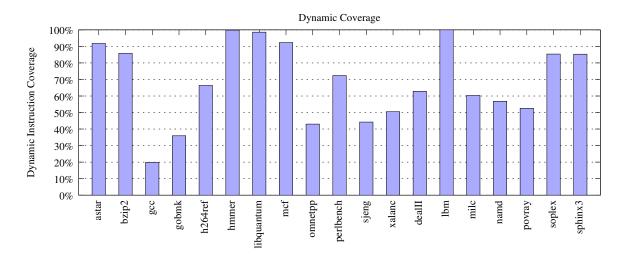

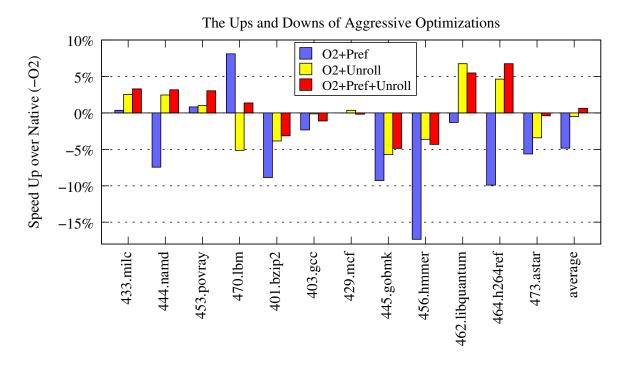

|   | 5.2 | Adapt   | ing the Application: Aggressive Optimization      | 67  |

|---|-----|---------|---------------------------------------------------|-----|

|   |     | 5.2.1   | Motivation: Win Some, Loose Some                  | 67  |

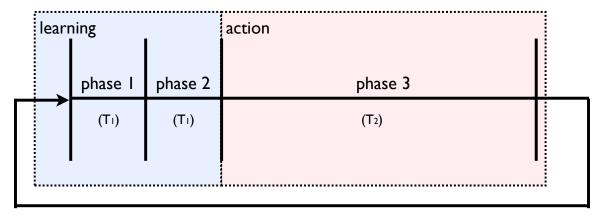

|   |     | 5.2.2   | Three Phase Execution                             | 68  |

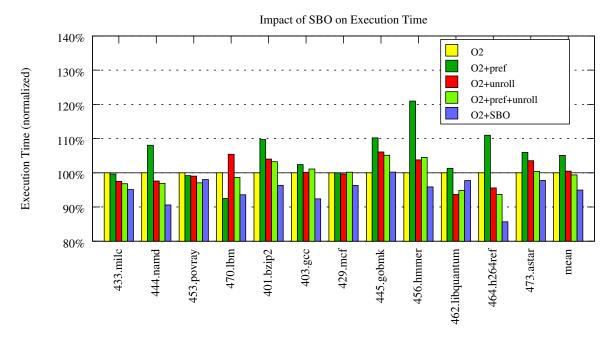

|   |     | 5.2.3   | The Effectiveness of SBO                          | 70  |

|   | 5.3 | Adapt   | ing the Environment: Contention Detection         | 73  |

|   |     | 5.3.1   | Challenge of Interference in WSCs                 | 73  |

|   |     | 5.3.2   | Motivation: Cross-Core Interference               | 74  |

|   |     | 5.3.3   | A Solution with CAER                              | 76  |

|   |     | 5.3.4   | Detecting Contention with CAER                    | 81  |

|   |     | 5.3.5   | The Effectiveness of CAER                         | 84  |

| 6 | Mi  | tigatin | ng Interference in WSCs with Precision            | 92  |

|   | 6.1 | Precis  | ely Predicting CCI Performance Penalty            | 93  |

|   |     | 6.1.1   | The Bubble-Up Methodology                         | 94  |

|   |     | 6.1.2   | Large-Scale WSC Workloads                         | 101 |

|   |     | 6.1.3   | The Effectiveness of Bubble-Up                    | 105 |

|   | 6.2 | Impro   | ving WSC Utilization with Bubble-Up               | 112 |

|   |     | 6.2.1   | Applying Bubble-Up in WSCs                        | 112 |

|   |     | 6.2.2   | Impact of Varying Architecture                    | 115 |

|   | 6.3 | Direct  | ly Quantifying CCI Sensitivity                    | 117 |

|   |     | 6.3.1   | Revisiting the Problem of Cross-Core Interference | 117 |

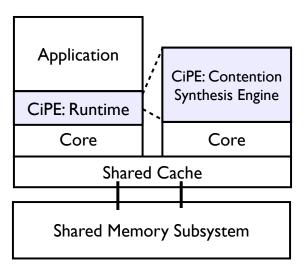

|   |     | 6.3.2   | Overview of CiPE                                  | 119 |

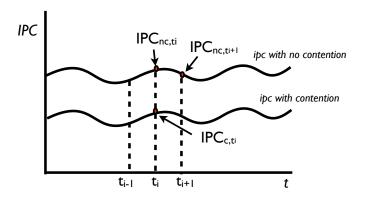

|   |     | 6.3.3   | Quantifying Sensitivity                           | 121 |

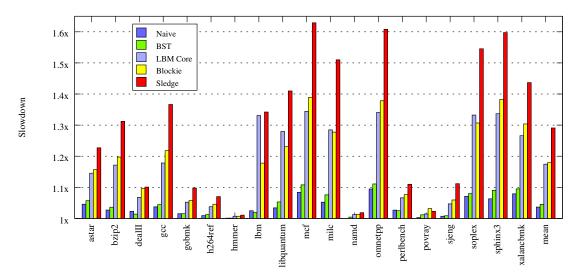

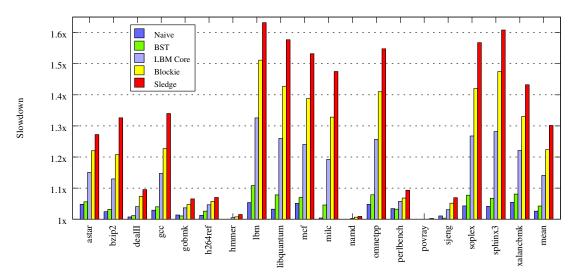

|   |     | 6.3.4   | Contention Synthesis                              | 124 |

|   |     | 6.3.5   | Applying the CiPE Methodology                     | 132 |

| 7 | Co  | nclusio | on and Future Directions                          | 139 |

|   | 7.1 | Summ    | nary of Themes and Results                        | 140 |

|   | 7.2 | Dutim   | Directions                                        | 146 |

| A            | Tec | chnical Details of Loaf-SBM Framework      | 145 |

|--------------|-----|--------------------------------------------|-----|

|              | A.1 | Performance Monitoring                     | 147 |

|              | A.2 | Periodic Probing                           | 148 |

| В            | Co  | ntention Synthesis Kernel Implementations  | 150 |

|              | B.1 | Naive.c                                    | 150 |

|              | B.2 | BST.c                                      | 151 |

|              | B.3 | Blockie.c                                  | 152 |

|              | B.4 | Sledge.c                                   | 153 |

| $\mathbf{C}$ | Co  | ntention Conscious Scheduling with CiPE    | 155 |

| D            | Ide | entifying Sensitive Code Regions with CiPE | 158 |

|              | D.1 | Contentious Code Regions of LBM and MILC   | 161 |

# List of Figures

| 1.1 | The Facets of WSC Efficiency. This Work Focuses on Performance and Uti-      |        |

|-----|------------------------------------------------------------------------------|--------|

|     | lization.                                                                    | 3      |

| 1.2 | Execution Environment of a Task                                              | 4      |

| 1.3 | Diverse Execution Environments in WSCs                                       | 5      |

| 1.4 | The Homogeneous Assumption - The Job Manager's View of a WSC                 | 6      |

| 1.5 | A Single Rigid Binary Executing in Three Contexts                            | 8      |

| 1.6 | Some co-locations violate web-search's 90% QoS threshold. The inability      |        |

|     | to precisely predict this performance interference leads to disallowing co-  |        |

|     | location for web-search and consequently, low machine utilization            | 9      |

| 3.1 | Performance comparison of key Google applications across three microarchi-   |        |

|     | tectures. Each cluster is normalized to poorest performing architecture (the |        |

|     | higher the better)                                                           | 26     |

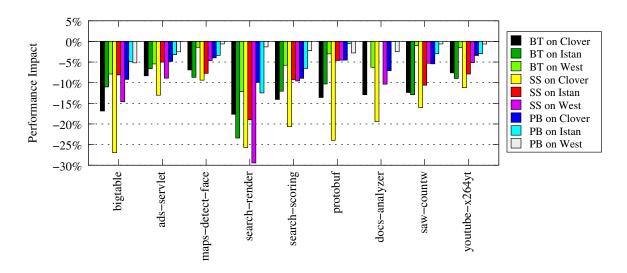

| 3.2 | Google application performance when co-located with bigtable (BT), search-s  | coring |

|     | (SS), and protobuf (PB). Negative indicates slowdown                         | 27     |

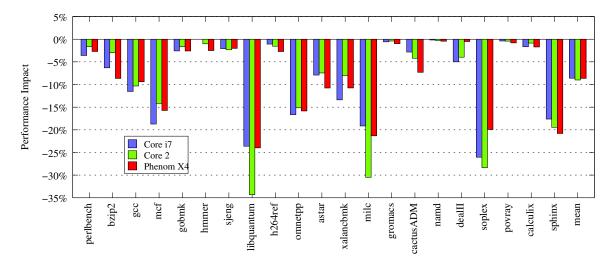

| 3.3 | Performance comparison of benchmark workloads across three microarchitec-    |        |

|     | tures.                                                                       | 29     |

| 3.4 | Benchmark slowdown when co-located with 1bm                                  | 29     |

| 4.1 | The Overview of SmartyMap                                                    | 33     |

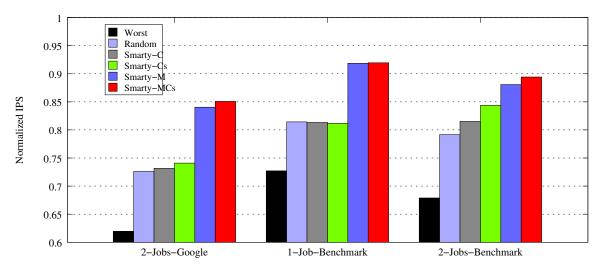

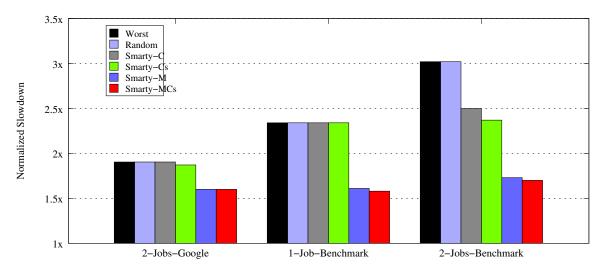

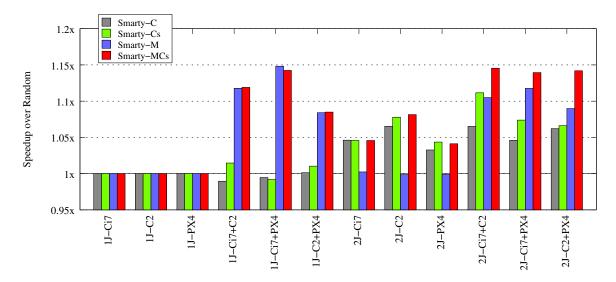

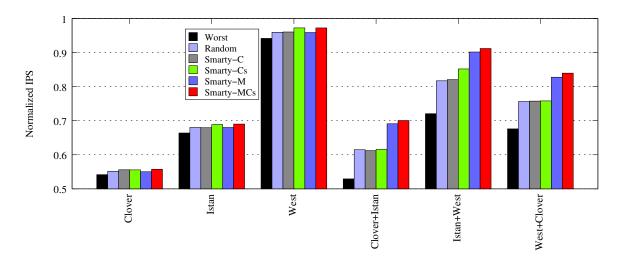

| 4.2 | Opportunistic Mapper compared to random and worst cases. (higher is better)  | 39     |

| 4.3 | Mapping policy's impact on latency to complete all jobs. (lower is better) . | 41     |

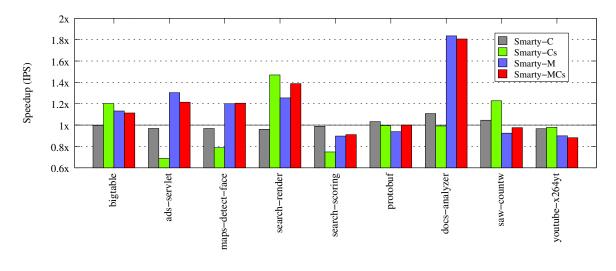

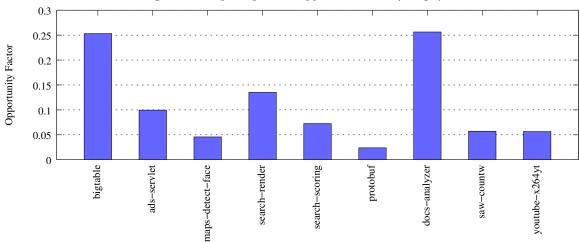

| 4.4 | Speedup at the application level. (Google)                                   | 42     |

| 4.5 | Opportunity factor of each application. (Google)                             | 42     |

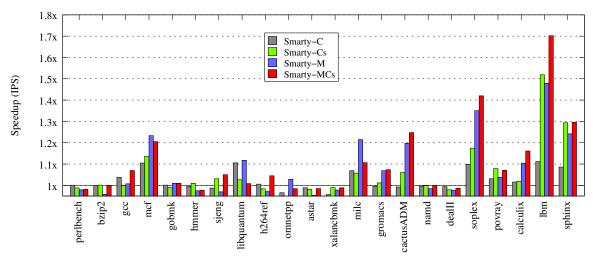

| 4.6  | Speedup at the application level. (Benchmark)                                |

|------|------------------------------------------------------------------------------|

| 4.7  | Opportunity factor of each application. (Benchmark)                          |

| 4.8  | Performance improvement from $SmartyMap$ over the currently deployed map-    |

|      | per in production                                                            |

| 4.9  | Impact of varying workload mix on available EE diversity for Google testbed. |

|      | Performance is normalized to random mapping. (higher is better)              |

| 4.10 | Impact of varying workload mix on available EE diversity for SPEC bench-     |

|      | mark testbed. Performance is normalized to random mapping                    |

| 4.11 | Impact of varying machine mix on EE diversity for Google testbed. Perfor-    |

|      | mance is normalized to random mapping. (higher is better)                    |

| 4.12 | Impact of varying machine mix on EE diversity for SPEC benchmark testbed.    |

|      | Performance is normalized to random mapping                                  |

| 4.13 | Normalized performance of various options of WSC machine composition         |

|      | (higher is better)                                                           |

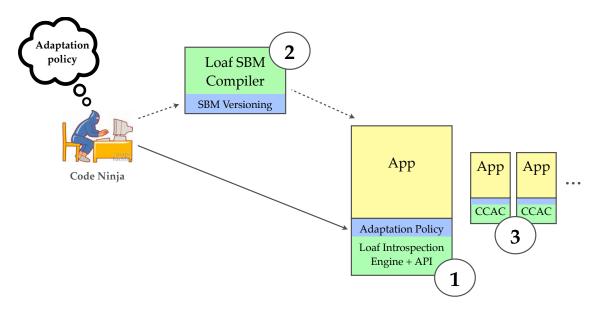

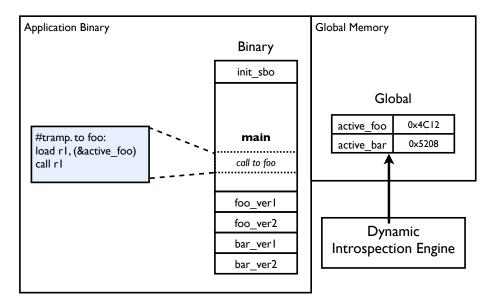

| 5.1  | Loaf Overview. (1) Lightweight Introspection (2) Scenario Based Multiver-    |

|      | sioning (3) Cross-Core Application Cooperation                               |

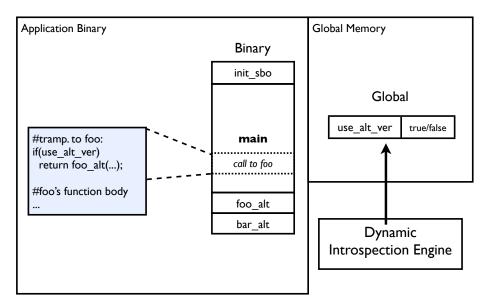

| 5.2  | Alternate Versioning Scheme                                                  |

| 5.3  | N-Version Versioning Scheme                                                  |

| 5.4  | This graph shows the percent of execution time spent executing of the Top    |

|      | 5 hottest functions across SPEC2006 benchmarks                               |

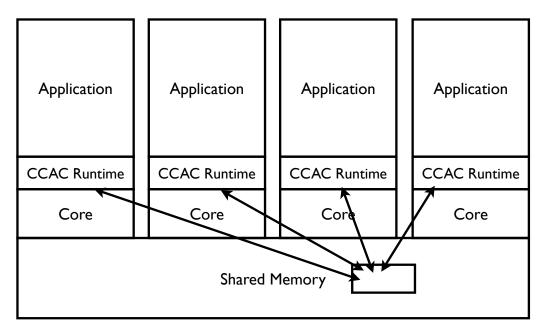

| 5.5  | Cross-Core Application Cooperation Run-time                                  |

| 5.6  | Overview of Scenario Based Optimizations                                     |

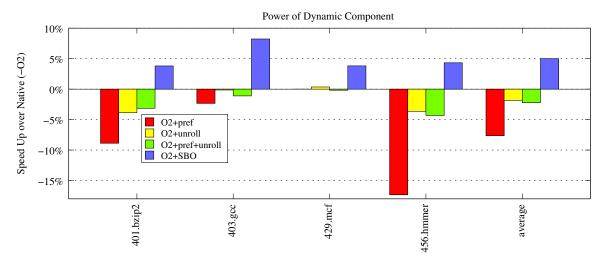

| 5.7  | This graph shows the speedup in execution time when aggressive optimiza-     |

|      | tions are applied. Note that sometimes there is a benefit other times we see |

|      | a degradation.                                                               |

| 5.8  | This represents the three phase execution approach of SBO                    |

| 5.9  | This is the execution time after applying the aggressive optimizations stat- |

|      | ically compared to applying the same optimizations using SBO. (lower is      |

|      | better)                                                                      |

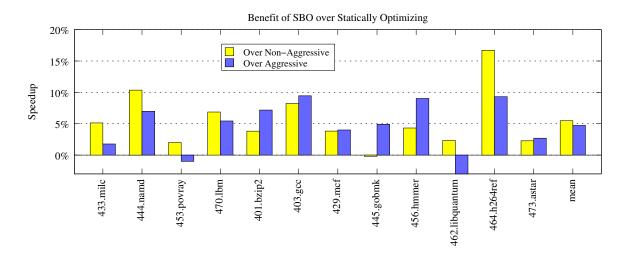

| 5.10 | Here we show the benefit of using SBO to dynamically select the right version     |    |

|------|-----------------------------------------------------------------------------------|----|

|      | for a scenario versus using only the code for either scenario for the entire run. | 71 |

| 5.11 | This graph highlights the power of a Scenario Based dynamic approach.             |    |

|      | These benchmarks all degrade or show no benefit when applying aggressive          |    |

|      | optimizations statically.                                                         | 72 |

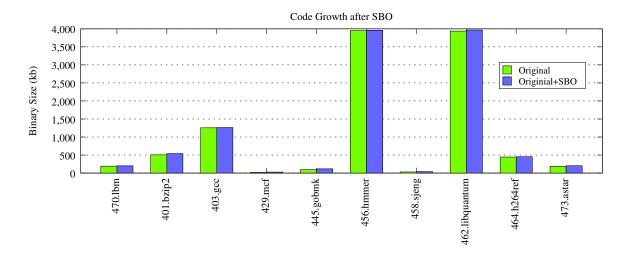

| 5.12 | Here we show what percentage of the binary is occupied by code added by           |    |

|      | prefetching and unrolling in addition to that added by SBO                        | 73 |

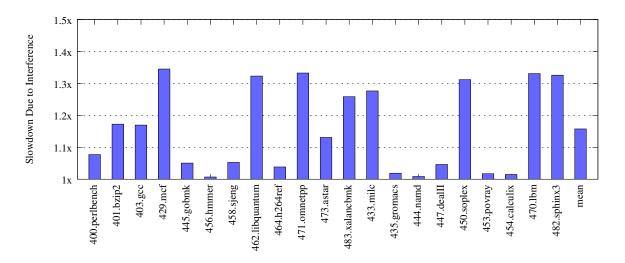

| 5.13 | Performance degradation due to contention for shared last level cache on          |    |

|      | Core i7 (Nehalem) while running alongside lbm                                     | 75 |

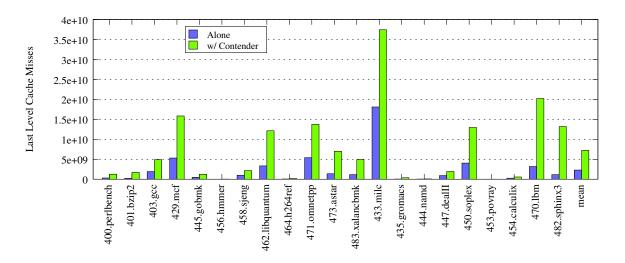

| 5.14 | Increase in last level cache misses when running with contender                   | 76 |

| 5.15 | Correlating last level shared cache misses and reduction in instruction retire-   |    |

|      | ment rate                                                                         | 78 |

| 5.16 | Architecture of our Contention Aware Execution Runtime                            | 79 |

| 5.17 | Basic Detection Response                                                          | 80 |

| 5.18 | Investigating the reduction in cross-core interference penalty                    | 86 |

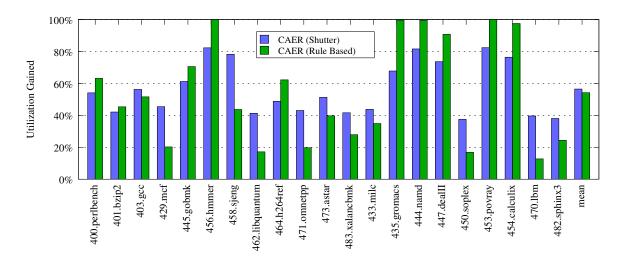

| 5.19 | Maximizing Utilization (Higher is Better)                                         | 87 |

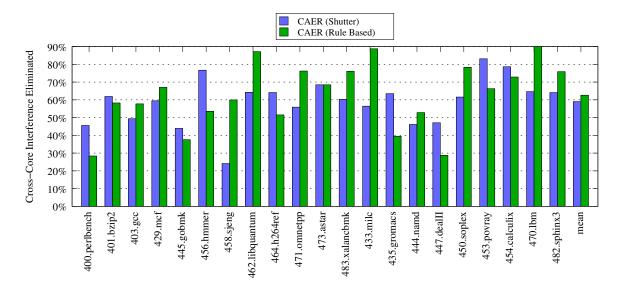

| 5.20 | Minimizing Cross-Core Interference (Slowdown Eliminated, Higher is Better)        | 88 |

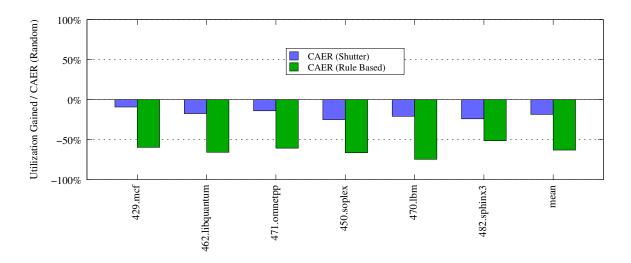

| 5.21 | Utilization gained relative to random for 6 most cross-core interference sen-     |    |

|      | sitive applications.                                                              | 89 |

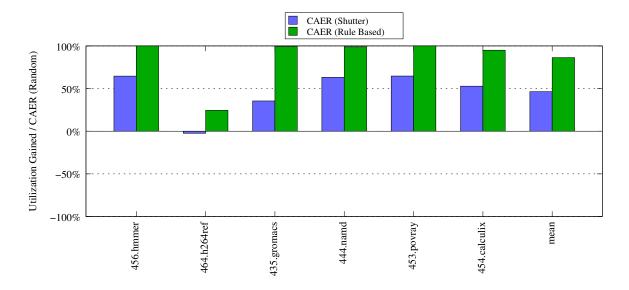

| 5.22 | Utilization gained relative to random for 6 least cross-core interference sen-    |    |

|      | sitive applications.                                                              | 90 |

| 6.1  | Task placement in a cluster. The cluster manager does not co-locate latency-      |    |

|      | sensitive applications with others to protect their QoS from performance          |    |

|      | interference, causing low machine utilization.                                    | 93 |

| 6.2  | Example sensitivity curve for $A$ . Assuming $B$ 's pressure score is 2 we can    |    |

|      | predict $A$ will be performing at 90% of full performance                         | 95 |

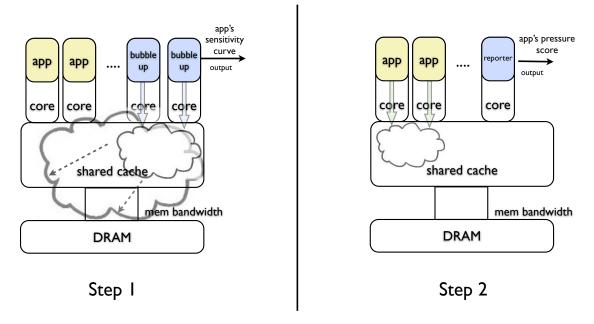

| 6.3  | <b>Bubble-Up</b> Methodology. In Step 1, we characterize the <i>sensitivity</i> of the |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | host application task to pressure in the memory subsystem using a $bubble$ . In        |     |

|      | Step 2, we characterize the <i>contentiousness</i> of the host application in terms    |     |

|      | of the amount of pressure it causes on a reporter                                      | 96  |

| 6.4  | Bubble's LFSR number generator.                                                        | 99  |

| 6.5  | Manual SSA for no dependencies                                                         | 100 |

| 6.6  | Streaming access for bandwidth                                                         | 100 |

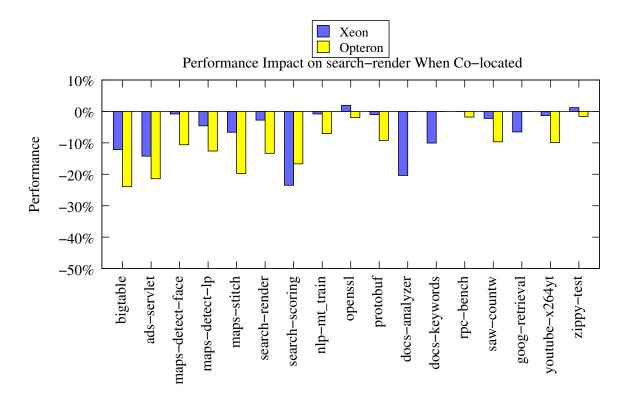

| 6.7  | The performance degradation suffered by search-render when co-located                  |     |

|      | with each of the other WSC applications on Xeon and Opteron                            | 103 |

| 6.8  | For a given working set size, we observe a different amount of interference            |     |

|      | when varying access pattern.                                                           | 106 |

| 6.9  | For a given access patter, we observe a different amount of interference when          |     |

|      | varying working set size                                                               | 106 |

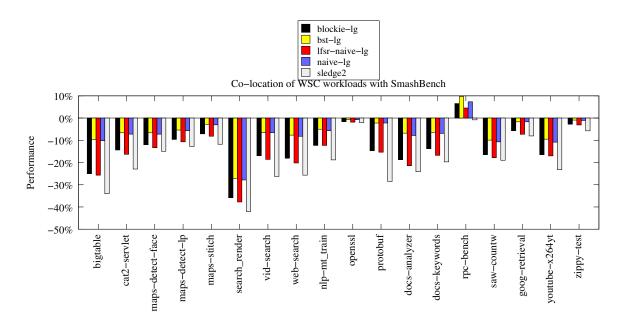

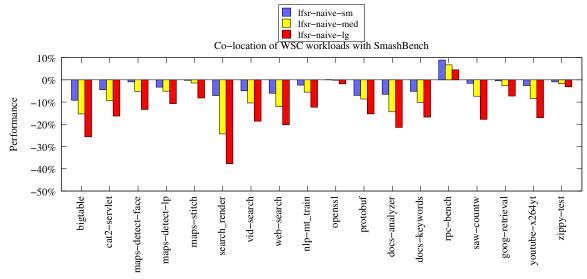

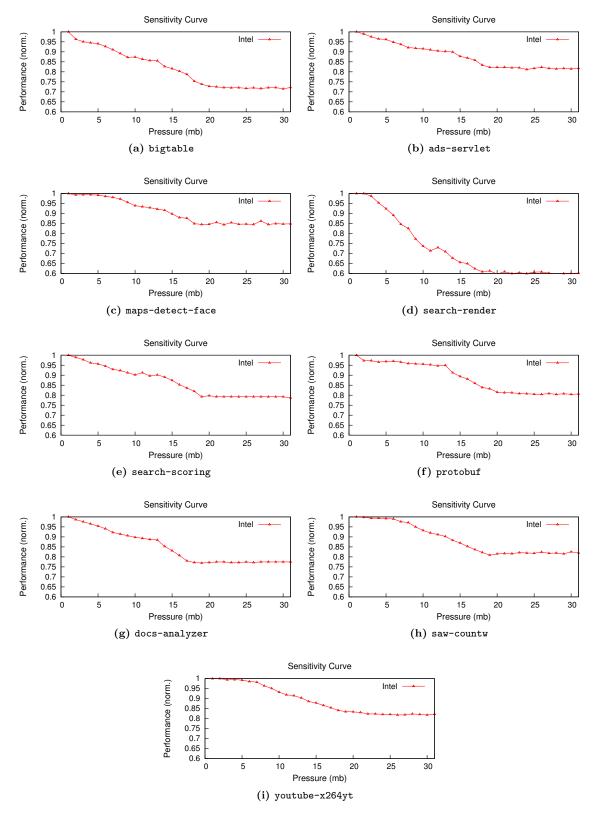

| 6.10 | Bubble-Up Sensitivity Curves for 9 Highly Sensitive Google Workloads                   | 108 |

| 6.11 | The Accuracy of Bubble-Up in Predicting QoS Impact for 9 Highly Sensitive              |     |

|      | Google Workloads.                                                                      | 110 |

| 6.12 | Bubble-Up's predication accuracy for pairwise co-locations of Google appli-            |     |

|      | cations.                                                                               | 111 |

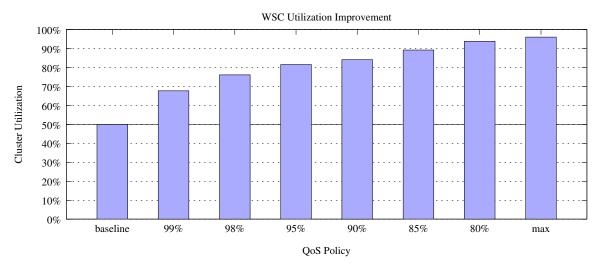

| 6.13 | Improvement in cluster utilization when allowing Bubble-Up co-locations                |     |

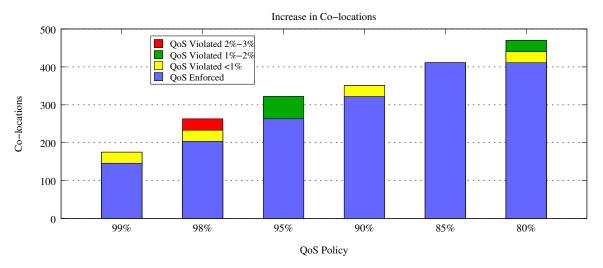

|      | with search-render under each QoS policy                                               | 113 |

| 6.14 | Number of Bubble-Up co-locations under each QoS policy                                 | 113 |

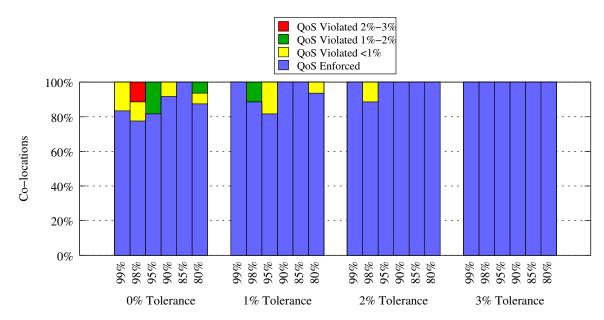

| 6.15 | Reduction in QoS violations when applying a <i>tolerance</i> to each QoS policy.       |     |

|      | Having a tolerance of just a few percent results in no violations                      | 114 |

| 6.16 | QoS violations when allowing all 500 co-locations with search-render under             |     |

|      | each QoS policy. (Random Assignment)                                                   | 115 |

| 6.17 | Improved utilization in a clusters composed of AMD K10 Opteron servers                 |     |

|      | and Intel Core 2 Xeon servers.                                                         | 116 |

| 6.18 | Co-locations allowed in Opteron and Xeon clusters                                      | 116 |

| 6.19 | Performance impact due to contention from co-location with LBM                         | 118 |

| 6.20 | The CiPE Framework                                                                     | 190 |

| 6.21 | IPC Curves                                                                  | 122        |

|------|-----------------------------------------------------------------------------|------------|

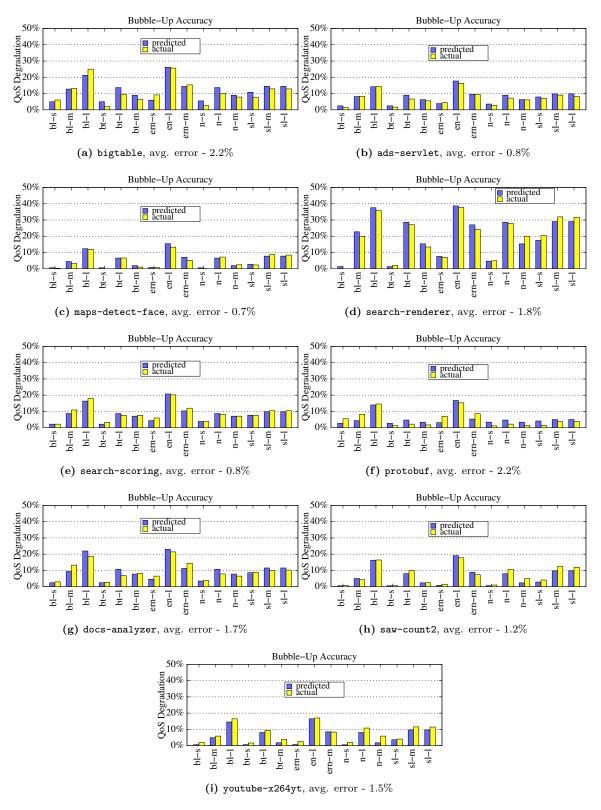

| 6.22 | Slowdown caused by contention synthesis on Intel Core i7                    | 130        |

| 6.23 | Slowdown caused by contention synthesis on AMD Phenom X4                    | 130        |

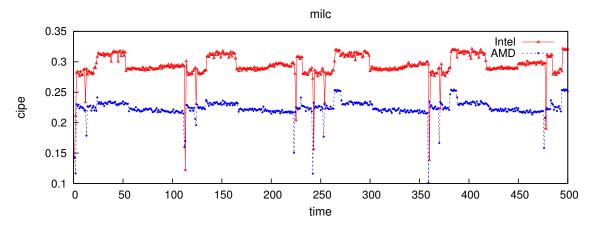

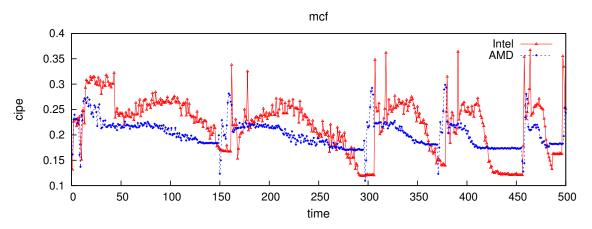

| 6.24 | Contentious phases of milc                                                  | 133        |

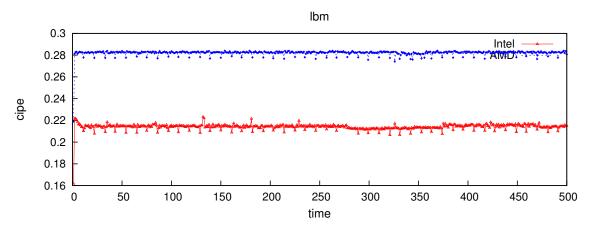

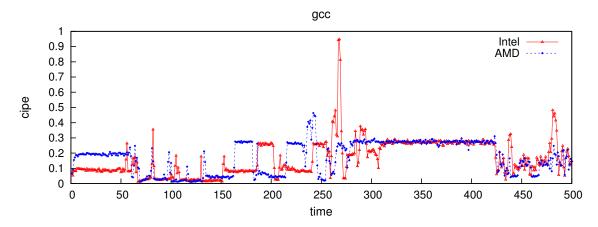

| 6.25 | Contentious phases of lbm                                                   | 133        |

| 6.26 | Contentious phases of mcf                                                   | 133        |

| 6.27 | Contentious phases of gcc                                                   | 134        |

| 6.28 | Contentious phases of sphinx                                                | 134        |

| 6.29 | Contentious phases of bzip                                                  | 134        |

| 6.30 | CIS score and last level cache misses compared to slowdown when contending  |            |

|      | with LBM (Intel Core i7)                                                    | 135        |

| 6.31 | CIS score and last level cache misses compared to slowdown when contending  |            |

|      | with LBM (AMD Phenom X4)                                                    | 136        |

| 6.32 | CiPE Overhead                                                               | 137        |

| A.1  | This is pseudo code for the general dynamic introspection component of sbm. | 147        |

| A.2  | This is the core three phase code to the dynamic component of the SBO       |            |

|      | algorithm.                                                                  | 149        |

| C.1  | Contention Oblivious vs CiPE-based scheduling (lower is better)             | 156        |

| C.2  | Performance Impact due to Co-Scheduling (higher is better)                  | 156        |

| D.1  | lbm Profile Sample                                                          | 158        |

| D.2  | milc Profile Sample                                                         | 159        |

| D.3  | Contention bottleneck in lbm.c                                              | 159        |

| D.4  | Architectural instructions for contention bottleneck in lbm.c               | 159        |

| D.5  | Contention bottleneck in su3_proj.c                                         | 160        |

| D.6  |                                                                             |            |

|      | Architectural instructions for contention bottleneck in su3_proj.c          | 160        |

| D.7  |                                                                             | 160<br>160 |

## List of Tables

| 1.1 | Number of Machine Types in Production WSCs                               | 7   |

|-----|--------------------------------------------------------------------------|-----|

| 3.1 | Production Microarchitecture Mix                                         | 24  |

| 3.2 | Production WSC Applications                                              | 25  |

| 3.3 | Experimental Microarchitecture Mix                                       | 28  |

| 4.1 | Mapping Scoring Policies                                                 | 36  |

| 4.2 | Number of Machine Types in Production WSCs                               | 45  |

| 4.3 | Workload Mixes                                                           | 47  |

| 6.1 | Production WSC Applications                                              | 102 |

| 6.2 | SmashBench Suite (stress point assumes a last level cache size of 6MB to |     |

|     | 12MB)                                                                    | 104 |

## Chapter 1

## Introduction

#### Contents

| 1.1 | Ramj  | pant Inefficiency in WSCs                             | 2  |

|-----|-------|-------------------------------------------------------|----|

| 1.2 | Diver | esity of Execution Environment in WSCs                | 4  |

| 1.3 | Three | e Design Problems                                     | 5  |

|     | 1.3.1 | The Homogeneous Assumption                            | 6  |

|     | 1.3.2 | Rigidness of Applications                             | 7  |

|     | 1.3.3 | The Oblivion of Interference                          | 8  |

| 1.4 | Sumr  | nary of Contributions                                 | 10 |

|     | 1.4.1 | Analyzing EE Diversity in Production WSCs             | 10 |

|     | 1.4.2 | Intelligently Mapping Jobs at the Cluster Level       | 10 |

|     | 1.4.3 | Online Adaptation at the Machine Level                | 11 |

|     | 1.4.4 | Mitigating Interference at Cluster and Machine Levels | 12 |

The landscape of computing is changing. Traditionally, the notion of computing held by users was of desktop computers in their homes that are used to accomplish some task, work or play, and after completing this task, users would return to their daily lives. However, in the recent decade, there has been a tectonic shift in the way end users view computing. With the evolution of the internet and the emergence of mobile devices such as smartphones, tablets, and highly portable laptops, we are now always connected and interface computing continuously throughout the day. Much of the computation cycles consumed by this emerging market lives in massive datacenter infrastructures recently coined "warehouse-

scale computers" (WSCs) [50,79]. The distinction made with this new term is in viewing the entire warehouse itself, not as a collection of many computers, but as a single, massively parallel computer, where the programs run on this computer are large-scale web-services. This emerging computing domain is rapidly expanding. As noted by Forrester Research, cloud computing was a \$40 billion market in 2011 and will grow six fold to \$241 billion market by 2020 [101].

WSCs are massive computers with tens to hunderds of thousands of cores and petabytes of main memory, spread across thousands of machines. The underlying hardware components that comprise the WSC are primarily composed of commodity parts including processors, memory, disk, network, etc. These components are stitched together to compose a warehouse of interconnected machines. The architecture of such a system is largely defined by the middleware and system software stack. These software components provide a single programmatic view of the WSC and organize the underlying hardware infrastructure for efficient and scalable operation. Internet service companies such as Google, Amazon, Yahoo, Microsoft, and Apple spend tens to hundreds of millions of dollars on WSCs to provide web-services such as search, mail, maps, docs, video, voice recognition, etc [1,9,20,58]. This large cost stems from the machines themselves, networking equipment, power distribution and cooling, the power itself, and other infrastructure components [35,45]. Improving the efficiency of WSCs has been identified as one of the top priorities of web-service companies as it improves the total cost of ownership (TCO) of WSCs, and as noted by the Environmental Protection Agency (EPA) [35], improving efficiency is not only important for the cost to companies, but also for the environmental footprint of these WSCs as this computing domain rapidly expands.

However, inefficiency remains rampant in modern WSCs.

### 1.1 Rampant Inefficiency in WSCs

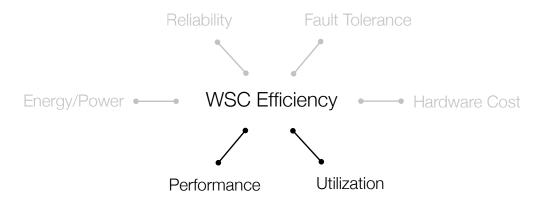

When considering the efficiency of WSCs there are a number of design objectives and metrics to consider. These *facets* of WSC efficiency are illustrated in Figure 1.1. In this work, we focus on software **performance** and machine **utilization** for improving the efficiency of

Figure 1.1: The Facets of WSC Efficiency. This Work Focuses on Performance and Utilization.

WSCs. In addition to these objectives being identified as critical for efficiency in WSCs [50], improvements in both the overall performance of applications running in the WSCs and the utilization of the compute resources in WSCs have beneficial implications across many of the other design objectives.

To understand why WSCs are currently inefficient, its important to reflect on the design of these systems in recent history. Modern WSCs have been evolving for only about a decade now. During this time, the architects of these systems have had a functionality first, efficiency second approach. The first order objective has been to design a WSC system that can deliver web-services and products to the massive user base in such a way that these infrastructures can scale with demand. To build a simple and cost effective system, WSC architects have used commodity off-the-shelf components including commodity x86 processors and open source system software components such as Linux, GCC, and the JVM. These general purpose components are then stitched together to design a simple and cost effective WSC system. As a second order objective, system architects then refine and improve upon these components for efficiency.

The problem with this approach is these commodity components were not built with WSCs in mind, and these massive WSCs do not resemble the traditional computing environments for which many of these commodity components have been initially designed and refined. When starting with these components to design the WSC architecture, system architects may produce a design that overlooks the unique characteristics and properties of WSCs. Thus, we must rethink the architecture of WSCs.

In this dissertation, we argue that one such characteristic is critical for designing a highly efficient system: the diversity of *execution environments* in WSCs.

#### 1.2 Diversity of Execution Environment in WSCs

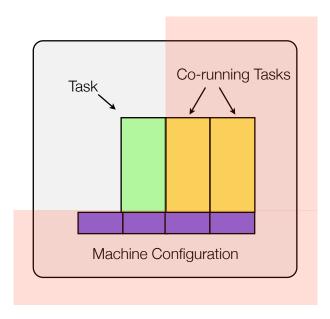

Figure 1.2: Execution Environment of a Task

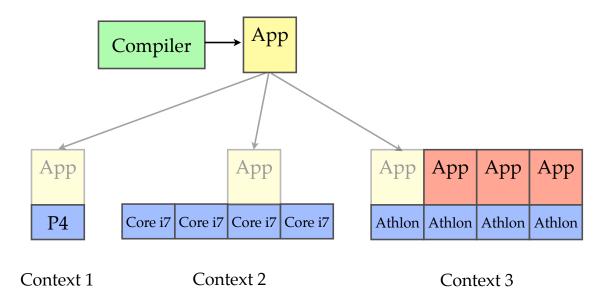

Given a running task in a WSC, its execution environment can be broadly defined as the set of elements in its context that impacts the performance and overall functioning of that task. Throughout the scope of this work, we focus on two of these elements: the machine and its load. As such, the specific definition of execution environment used herein is the coupling of the machine configuration and co-running tasks simultaneously executing alongside the given task. Figure 1.2 provides an illustration of an execution environment. The highlighted regions show the components that comprise the execution environment of a task.

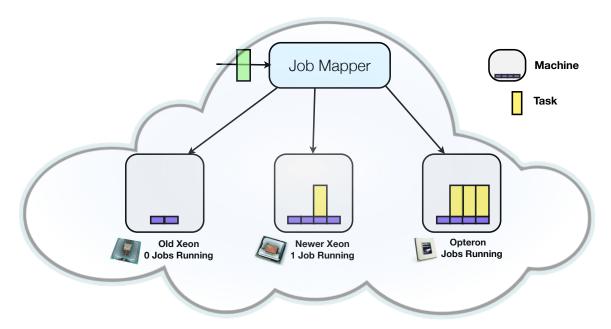

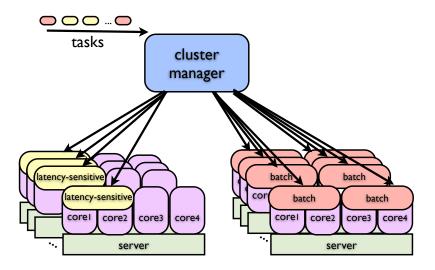

Within modern WSCs, we have a high level of diversity across execution environments. Figure 1.3 provides a simplified illustration of the diversity that is commonly found in production WSCs. Across the machines shown in this WSC, we observe diverse microarchitectural configurations. In the figure, we have an older Xeon architecture with only two cores, a newer Xeon architecture with four cores, and an Opteron architecture with four

Figure 1.3: Diverse Execution Environments in WSCs

cores. These machines, spanning several generations of Intel and AMD architectures, differ not only in their number of cores, but also in their microarchitectural design. In addition to diverse machine configurations, at any time during the lifetime of a WSC, each machine is loaded with different types, and a different number, of tasks. This co-runner diversity is also illustrated in Figure 1.3. Although we see a significant amount of diversity across various execution environments, modern WSC design does not acknowledge this diversity.

This dissertation argues for a WSC design that acknowledges the diversity in execution environments. We claim that incorporating an awareness of, and enabling adaptation to, this diversity is critical for highly efficient WSCs. In this dissertation, we address three design problems that result from overlooking the diversity across execution environments in WSCs.

### 1.3 Three Design Problems

In this section, we discuss the three core problems that arise due to a WSC design that is oblivious to the diversity in execution environments:

1. [Cluster Level] The homogeneity assumption. The heterogeneity of machines that compose a WSC cluster is ignored. Tasks are not placed where they run best.

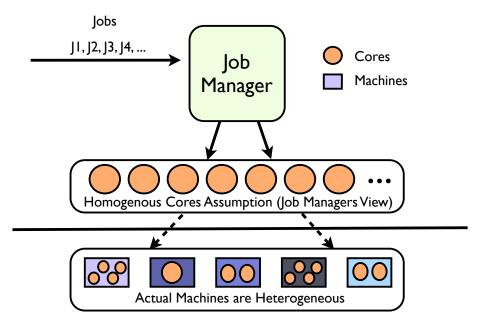

Figure 1.4: The Homogeneous Assumption - The Job Manager's View of a WSC

- 2. [Machine Level] The rigidness of applications. Application tasks do not adapt to changes across and within execution environments. Tasks run inefficiently.

- 3. [Cluster and Machine Level] The oblivion of interference. Interference between the tasks running within an execution environment is not measured or managed. The over-provisioning of compute resources is used for performance isolation leading to lower utilization.

#### 1.3.1 The Homogeneous Assumption

At the cluster level, the homogenous assumption is a source of inefficiency. WSCs have been embraced as homogeneous computing environments [9,50]. However, as previously discussed, this homogeneity is not the case in practice. WSCs are typically composed of cheap and replaceable commodity components. As machines are replaced in these WSCs, new generations of hardware are deployed while older generations continue to operate. This leads to a WSC that is composed of a mix of machine platforms, e.g., a heterogeneous WSC. Table 1.1 shows the amount of distinct machine configurations found in 10 randomly selected anonymized Google WSCs in operation. As shown in the figure, these 10 WSCs house as few as two and as many as five different microarchitectural configurations span-

|   | D0 | D1 | $\mathbf{D2}$ | D3 | D4 | D5 | D6 | D7 | D8 | D9 |

|---|----|----|---------------|----|----|----|----|----|----|----|

| ĺ | 4  | 3  | 2             | 3  | 2  | 3  | 2  | 5  | 2  | 2  |

Table 1.1: Number of Machine Types in Production WSCs

ning Intel and AMD servers from several consecutive generations. Yet, the assumption of homogeneity has been a core design philosophy behind the job management subsystems of modern WSCs [50]. As Figure 1.4 shows, the job manager views the WSC as a collection of tens to hundreds of thousands of cores with the assumption of homogeneity. Each task in the WSC is configured with the number of cores and amount of memory it requires. The job manager then arbitrarily selects a machine with the required cores and memory available to assign the task.

Some types of tasks are very sensitive to changes in execution environment, while others are less affected. However, the diversity across the underlying microarchitectures and application co-runners in the WSC is not explicitly considered by the job management subsystem. As we show in this dissertation, ignoring this diversity in execution environments leads to the inefficient execution of applications in WSCs. We also present an enhanced mapping system that exploits this diversity to improve the performance of the WSC.

#### 1.3.2 Rigidness of Applications

At the machine level, the rigidness of applications is a source of inefficiency. Traditionally, an application program is written by a programmer, then statically compiled to a binary executable file composed of instructions from a targeted instruction set architecture (ISA). This binary can then be run on a range of micro-architectures that conforms to that ISA. The structure and layout of the binary code is determined statically, and consequently, it remains rigid across inputs, micro-architectures and execution environments. It is well known that semantically equivalent variations in the code structure and layout can cause a wide range of variance in its performance and other properties [39, 131]. As a result, programmers and optimizing compilers are faced with the task of statically determining the optimal code layout and structure for application binaries. However, these code structure and layout decisions are impacted by changes across and within execution environments. These changes occur across application runs, and indeed, during a single run.

Figure 1.5: A Single Rigid Binary Executing in Three Contexts

Figure 1.5 shows three execution environments of a single application: in the first context the application runs alone on a single core machine, in the second context the same binary runs on a multicore machine, and in the third context the application's execution environment includes three other co-running processes on a quad core machine. The applications optimal code layout and execution behavior may vary across these contexts. There are a class of problems that requires the dynamic response to events as they occur during execution. To allow this flexibility, *online adaptation* is required. However, we lack a lightweight, deployable mechanism to enable online adaptation in modern WSCs. In this dissertation, we present a new paradigm for online adaptation that allows the adaptation of an application to its environment and the environment to the application. We then leverage this approach to address two pressing problems in WSCs.

#### 1.3.3 The Oblivion of Interference

At the cluster and machine levels, the oblivion of interference is a source of inefficiency. The cost of construction and operation of WSCs ranges from tens to hundreds of millions of dollars. As more computing moves into the cloud, it is becoming exceedingly important to utilize all the resources in WSCs as efficiently as possible. However, the utilization of the computing resources in modern WSCs remains low, often not exceeding 20% [72].

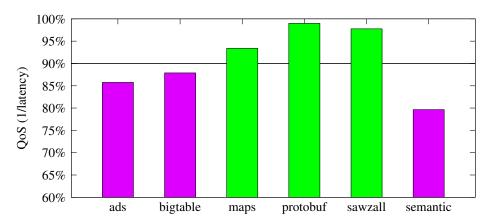

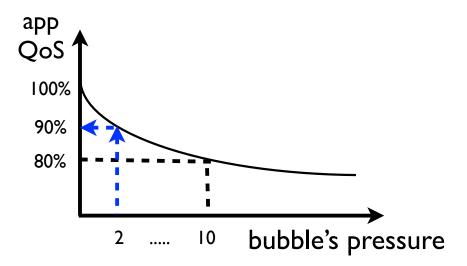

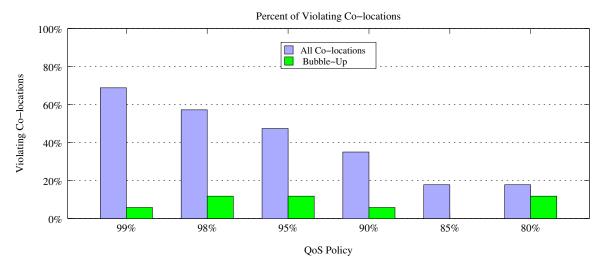

Figure 1.6: Some co-locations violate web-search's 90% QoS threshold. The inability to precisely predict this performance interference leads to disallowing co-location for web-search and consequently, low machine utilization.

Each machine in the WSC houses numerous cores, typically 4 to 8 cores per socket and 2 to 4 sockets per machine. However, in light of the significant potential for parallelism on a single machine, there are a number of resources shared among cores. This sharing can result in performance interference across cores, negatively and unpredictably impacting the performance of user-facing and latency-sensitive application threads [117]. Strictly defined performance requirements can be referred to as quality of service (QoS) requirements. Interference negatively and unpredictably degrades QoS. To avoid the potential for interference on applications with strict QoS requirements, co-location is disallowed for latency-sensitive applications. This policy leaves cores idle, resulting in the overprovisioning of compute resources, and ultimately leading to lower utilization in the WSC.

This overprovisioning is often unnecessary, as co-locations may or may not result in significant performance interference. Figure 1.6 demonstrates the uncertainty of interference in modern WSCs. In this figure, we show the performance  $(\frac{1}{latency})$ , of a key user-facing component of Google's web-search when co-located with other Google workloads on a single socket, normalized to solo execution. The horizontal line shows the maximum allowable performance interference. The co-location of some workloads does not violate this QoS threshold (light bars), while others violate the threshold (dark bars).

The inability to quantify and predict the performance impact of interference between tasks within the execution environment leads to the heavy handed solution of simply disallowing co-location. In this dissertation, we show it is indeed possible to perform this precise prediction using a novel mechanism and provide new metrics for characterizing an application's sensitivity to interference, as well as its aggressiveness.

#### 1.4 Summary of Contributions

This dissertation investigates and exploits the diversity found in execution environments (EE) within production WSCs by first analyzing the diversity found in WSCs and then addressing the three design challenges discussed.

#### 1.4.1 Analyzing EE Diversity in Production WSCs

We first perform a study of the performance impact of the diverse execution environments across machines from Google's production fleet and Google's large-scale commercial WSC workloads. We also replicate this study using an experimental testbed composed of benchmark workloads to provide repeatable experimentation without the need of a commercial production environment. Chapter 3 examines:

- Variability Across Execution Environments: We investigate the performance variability for large-scale web-service applications caused by diversity in machine configuration and application co-runners. This is the first work to investigate this variability in a production commercial WSC. (Section 3.1)

- Opportunity Factor: We introduce a novel metric, the *opportunity factor*, that quantifies the sensitivity of an application to diversity in machine configuration and application co-runners. This metric also indicates an application's potential performance improvement when mapped to execution environments where they run best. (Section 3.2)

#### 1.4.2 Intelligently Mapping Jobs at the Cluster Level

At the cluster level, we provide an intelligent mapping approach where tasks in the WSC are placed in execution environments where they run best. Chapter 4 examines:

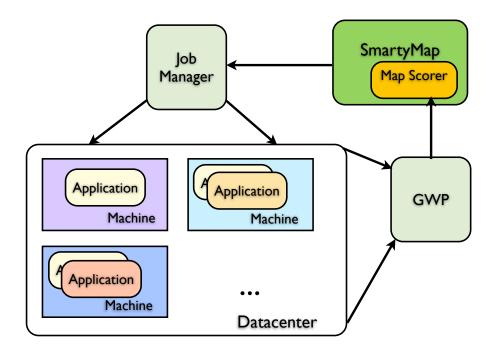

- SmartyMap: We present SmartyMap, an extension to the current WSC architecture to exploit the heterogeneity in WSCs. SmartyMap intelligently maps jobs to machines to improve the overall perfor- mance of a WSC. A required component of such an approach is the ability to score and rank job-to-machine maps. We design map scoring approaches that take advantage of the live monitoring services in modern WSCs. We also provide four map scoring policies and discuss the key trade offs among them. (Section 4.1)

- Benefit of Intelligent Mapping: We investigate the effectiveness of SmartyMap and demonstrate the performance opportunity of exploiting the heterogeneity in those production WSCs. In addition to production datacenters, our study also includes comprehensive experimentation on a Google testbed composed of 9 large-scale production web-service applications and 3 types of production machines, as well as an experimental testbed composed of benchmark applications. (Section 4.2)

- Factors Affecting EE Diversity: We perform a careful study of how varying the diversity in applications and machine types in a WSC affects the "homogeneity" or "heterogeneity" of the WSC. We find that even a slight amount of diversity in these factors can present a significant performance opportunity. Based on our findings, we then discuss the tradeoffs for server purchase decisions and show that heterogeneous WSCs may be more cost-efficient than homogeneous WSCs. (Section 4.3)

#### 1.4.3 Online Adaptation at the Machine Level

At the machine level, we provide a mechanism to allow tasks to adapt to the execution environment in which it runs. Chapter 5 examines:

• Lightweight Online Adaptation: The design of the Lightweight Online Adaptation Framework (Loaf), a novel lightweight online adaptation framework for native binary applications that is both able to adapt an application to its execution environment and also the execution environment to the application. Loaf is composed of three core mechanisms: periodic probing for lightweight introspection, scenario based multiversioning for online code restructuring, and cross core application cooperation for

coordinated adaptation across cores. (Section 5.1)

- Online Adaptation for Aggressive Optimizations: Using our Loaf framework, we provide an approach that enables applications to self-select compiler optimizations based on the execution environment in which it runs. This approach, Scenario Based Optimization, dynamically applies aggressive optimizations (known to either improve or degrade performance) only when these optimizations are detected as beneficial. (Section 5.2)

- Online Adaptation for Contention Detection and Response: We present a Loaf based runtime, the Contention Aware Execution Runtime (CAER) environment, which is capable of instantaneous contention detection and response on real commodity machines. CAER uses two contention detection heuristics: the Burst Shutter and Rule Based techniques. When contention is detected, CAER dynamically adapts low priority applications to minimize the interference caused to higher priority applications. (Section 5.3)

#### 1.4.4 Mitigating Interference at Cluster and Machine Levels

At both the cluster and machine levels, we provide novel capabilities in measuring and managing interference between tasks within an execution environment. Chapter 6 examines:

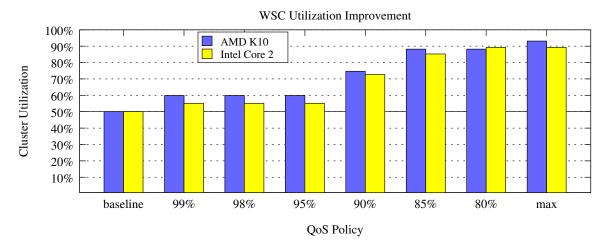

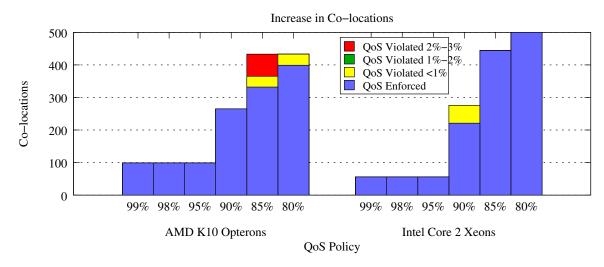

- Precise Interference Prediction: We present the design of Bubble-Up, a general characterization methodology that enables the precise prediction of the performance degradation that results from contention for shared resources in the memory subsystem. A precise prediction is one that provides the expected amount of performance lost when co-located. With this information, co-locations that do not violate the QoS threshold of an application can be allowed, resulting in improved utilization in the WSC. (Section 6.1)

- Improving WSC Utilization with Bubble Up: Using 17 production Google workloads and production machines, we demonstrate how using Bubble-Up to steer co-location decisions can significantly improve the utilization of WSCs. (Section 6.2)

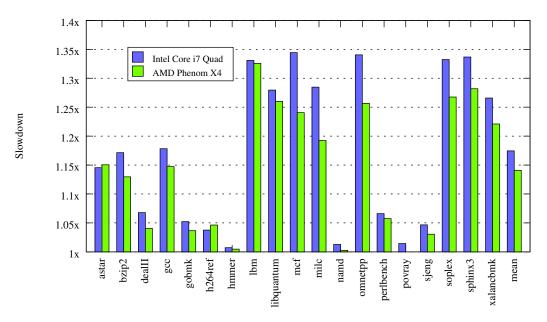

• Direct Methodology to Quantify Interference Sensitivity: We present a general direct measurement technique and metric for quantifying cross-core interference sensitivity at both application and phase levels and the design of CiPE, a framework that employs this measurement technique along with contention synthesis to characterize application sensitivity to cross-core interference. We also design and present four contention synthesis kernels and the core algorithms for each. (Section 6.3)

## Chapter 2

## Background and Related Work

#### Contents

| 2.1 | Task Placement in Modern WSCs | .4 |

|-----|-------------------------------|----|

| 2.2 | Quality of Service            | .5 |

| 2.3 | Co-location                   | .5 |

| 2.4 | QoS Flexibility               | .6 |

| 2.5 | Related Work                  | .6 |

In this chapter, we provide background on how tasks are placed in WSCs, the importance of quality of service (QoS) requirements in WSCs, and the implications of co-locating tasks on machines in modern WSCs. We also present a summary of related works.

#### 2.1 Task Placement in Modern WSCs

In modern warehouse-scale computers, each web-service is composed of one to hundreds of application tasks, and each task runs on a single machine. A task is composed of an application binary, associated data, and a configuration file that specifies the machine level resources required. These resources include the number of cores, amount of memory, and disk space that are to be allocated to the task. The configuration file for a task may also include special rules for the cluster manager such as whether to disallow co-locations with other tasks.

Task placement is conducted by a cluster-level manager that is responsible for a number

of servers. Based on the resource requirement, the cluster manager uses an algorithm similar to bin-packing to place each task in a cluster of machines [82]. After a task is assigned a machine, a machine level manager (in the form of a deamon running in user-mode) uses resource containers [8] to allocate and manage the resources belonging to the task. For the remainder of this work, we use the term application to represent the program binary for a given component of a web-service and application task as an instance of this binary coupled with its execution configuration file. The term job may also be used interchangeably with task.

#### 2.2 Quality of Service

As multicores become widely adopted in datacenters, the cluster manager consolidates multiple disparate tasks on a single server to improve the machine utilization. However, various application tasks in a datacenter often have different quality-of-service (QoS) priorities. User-facing applications for web-search, maps, email and other internet services are latency-sensitive and have high QoS priorities. Applications such as file backup, offline image processing, and video compression are batch applications that often have no QoS constraints. For these, latency requirements are not strictly defined. We define the QoS of a latency-sensitive application in terms of the relevant performance metric specified in its internal service level requirements (SLAs). For example, the QoS of Google's web-search is measured using query latency and queries-per-second, in contrast to Bing's [58,65], which uses the quality of search results provided.

#### 2.3 Co-location

Tasks are co-located when they run simultaneously on a single machine. Managing performance interference and providing task level performance isolation on the machines housed by WSCs have been challenges due to contention for resources shared across the numerous cores on a single machine. When co-locating a latency-sensitive application with other applications on the same server, the latency-sensitive application is at risk of suffering significant QoS degradations when the co-running applications are aggressively contending

for resources such as shared cache space or memory bandwidth. Due to the inability of predicting the amount of this performance interference, the current placement policy in current WSCs is to disallow any co-location of a latency-sensitive task with other tasks on the same machine to guarantee its QoS. This ad-hoc approach is a major contributor to the low utilization we find in modern WSCs.

### 2.4 QoS Flexibility

There is a trade-off between the QoS performance of latency-sensitive applications and the machine utilization in WSCs. When equipped with mechanisms to measure and manage interference, a small amount of QoS degradation can be allowed to increase co-locations and improve the machine utilization. If a co-location is predicted to cause less QoS degradation than a specified threshold, the cluster manager can allow the co-location. We specify the tolerable amount of QoS degradation in a QoS policy. For example, a 95% QoS policy indicates that we are willing to sacrifice 5% of the QoS performance to improve machine utilization. To enforce these QoS policies, the precise prediction for QoS degradation due to co-location is needed. These QoS issues and challenges affecting machine utilization are revisited later in this dissertation (Chapters 5 and 6); the earlier parts of this dissertation addresses software performance.

#### 2.5 Related Work

#### Warehouse-Scale Computing

Much of the related datacenter research have focused specifically on improving energy and power efficiency [1,3,29,46,84,91]. There has also been work on scheduling in the datacenter [51], enabling QoS-aware control in the datacenter [85], and programming the datacenter [14]. Other works developed tools and support for interacting and developing for the datacenter [10,114]. There has been some important work studying web search in WSCs, including the work by Barroso et al. [9], which presents an insightful look at the design and layout of an industry strength web-search datacenter. More recently, Reddi et al. [58] pre-

sented the impact of running an industry-strength search engine on a datacenter composed of Atom chips.

There are prior works that have acknowledged heterogeneity in datacenters [13, 128]. While these works focus on datacenters that provide utility computing and improving MapReduce, our work focuses on the global design and optimization of the emerging space of WSCs. In this work, we focus on WSC efficiency via improving performance and utilization.

There has been a significant amount of research effort applied to the domain of heterogeneous multicore architecture. Some of the seminal works in this area are those by Kumar et al. [66,67]. In these work, Kumar used simulation to investigated the performance benefit of exploiting heterogeneous architectures by evaluating heuristics to dynamically schedule thread workloads based on a speedup factor. This work led to a number of other works on scheduling for the heterogeneous multicore [64, 68, 69, 102, 107]. The work by Winter et al. [121] is related to the numerical optimization techniques used in this dissertation. This work investigated the task of scheduling for "unpredictably" heterogeneous multicore processors due to process variation.

PROPHET provides a goal-oriented provisioning infrastructure and tunes the datacenter to satisfy the needs of particular end users [122]. The work by Kazempour et al. was the first to implement changes to the hypervisor scheduler to incorporate asymmetry-awareness [61]. Another related work discusses a scheduling policy that uses a linear programming approach which maximizes system capacity to map an application across a desktop grid [4]. This work focuses on distributed desktop computers and does not consider the interaction between microarchitectural and co-location diversity.

#### Online Adaptation in Managed Runtimes

Current online dynamic optimization approaches can be separated into two categories: those that deal with managed run-time systems targeting bytecode and those that apply to native application binaries. The majority of online optimization frameworks that target bytecode work at the function granularity [5,90,111]. These optimizers detect frequently executed methods and identify them as hot. These hot methods are then *just-in-time* compiled and recompiled at higher levels of optimization, depending on how often they are executed.

Other bytecode online optimization and adaptation approaches [119,120] address memory and other issues. However our work is concerned with the online adaptation of arbitrary binaries.

#### Online Adaptation at the Binary Level

Our work deals with the class of online optimizers and optimization frameworks that deal with native binaries directly such as Dynamo [7], DynamoRIO [12], and Strata [106]. These current dynamic optimization techniques have had limited success. One of the seminal works that has inspired many future projects was the work by Bala et al. [7] on Dynamo. Dynamo is a binary to binary translator and dynamic optimizer that works at the basic block and trace levels. Dynamo was the only online optimizer of its class to achieve consistent performance gains. This has mostly been attributed to the intricacies of the PA-RISC platform for which it was implemented. Attempts have been made to reproduce this performance benefit on other architectures, but have been largely unsuccessful. Bruening et al. reimplemented the Dynamo infrastructure for x86 with the DynamoRio project [12] and was unable to achieve significant improvement. A similar effort was made with the Strata [106] infrastructure and was also unable to achieve performance gains. One major challenge these three approaches face is the added overhead from virtualizing the application and maintaining control of the executing binary. In fact there has been much work focused on optimizing the dynamic optimizer itself, in particular the handling of indirect branches [49].

Research attention has also been paid to online optimization approaches using multicore architecture and novel hardware techniques. The Adore infrastructure has been proposed by Lu et al. [74] to achieve dynamic software prefetching via the use of helper threads and performance monitoring hardware. A similar technique was also later applied to SUN's UltraSparc Architecture [75]. Zhang et al. proposed Trident [129, 130], a new dynamic optimizer framework that requires hardware support. This work proposes that trace selection occurs entirely in hardware and uses a number of hardware extensions. This work shows promising potential, but currently cannot be applied as it depends on novel microarchitectural features to be developed.

#### **Extracting Run-time Information**

The usefulness of information about an application's run-time behavior and dynamic microarchitectural impact has also shown to be quite important. Profiling has become the cornerstone for understanding an application's behavior and can play an important part in compiler optimizations as shown in the work by Chang et al. [23]. This seminal work introduces compiler support for profile feedback directed compiler optimizations. The compiler executes the application on a number of canned inputs, profiles it, and recompiles the application using this information. Using profiling information has lead to many new kinds of optimizations [44, 92, 97]. However these compiler optimizations remain rigid, and thus tends to be applied conservatively.

Hardware performance counters have been shown to be a great tool to enable low overhead profiling of micro-architectural events. Moreover, these hardware structures are becoming more complex as is seen in the work by Dean et al. [32]. Azimi et al. present a technique to use limited performance counters to simultaneously profile numerous events via sampling [6]. In recent work by Cavazos et al. [18] performance counters and machine learning are used together to find better compiler optimization settings for applications. These performance counters are also being used for more than just profiling. In the works by Chen et al. [24] and our prior work [78] performance monitoring hardware are used to form dynamic hot traces without slowing down the running application. We also see performance counters used in Java VMs and JITs to steer optimization in the works by Schneider et al. [105] and Adl-Tabatabai et al. [2]

#### Function Cloning and Versioning

Function cloning and multiversioning is an inter-procedural code transformation that is used by a number of optimizations dating back to the earliest works on compiler optimization [15–17, 30, 31, 33, 118]. It was originally conceived for classic optimizations such as inter-procedural constant propagation (IPCP) [16]. It has also been been used by Carini et al. for flow insensitive IPCP [17] and Cierniak et al. for inter-procedural array remapping [30].

Multiversioning approaches have also been used by Diniz et al. [33] and Voss et al. [118]. In the work by Diniz et al. multiversioning is used in the context of a parallelizing compiler for object-based languages to provide a mechanism to dynamically switch the implementation of a particular synchronization mechanism online. Although the concept of dynamic feedback is discussed in our work, a general mechanism to achieve online code adaptation using multiversioning is not explored. In addition, the mechanisms used in this work to gather information to steer version switching is significantly limited in comparison to the scenario based multiversioning approach presented in this work. The multiversioning approach provided by Diniz's dynamic feedback relies entirely on a timing approach, only allowing for variants of the sampling/production phase heuristic presented in their work. However our scenario based multiversioning provides much more general monitoring capabilities in that our approach is guided by the ability to identify scenarios based on a collection of the information available through our lightweight introspection interface. In addition the idea of having a number of co-running application adapting in cooperation is also not explored.

The work by Voss et al. [118] discusses the idea of switching regions of executing code dynamically. However, multiversioning is not performed statically. Versions are generated continuously by compiler tools and optimizers running on sockets and machines independent of the executing applications. In addition, users of their system must learn a new domain specific language and the flexibility of potential adaptation policies is limited to what can be expressed in this language. Requiring this new language presents a significant amount of complexity, which is contrary to the goal of Loaf. Also the fact that a new language must be learned to use their system may further deter users from adopting this approach.

More recently mutliversioning has been used in a number of works by Fursin et al. as a mechanism to provide dynamic machine-learning testbeds for evaluating optimization configurations and performing online optimization space pruning [39,40]. In our work, we take advantage of function cloning and multiversioning to provide a general, flexible and lightweight approach to enable online code adaptation.

#### Contention and Interference

When two applications are running on neighboring cores, contention for the shared cache can affect an application's Quality of Service (QoS) and can negatively affect overall throughput and scheduling fairness. QoS and fairness techniques have received much research attention [48, 54, 55, 62, 83, 88, 89, 108]. These works propose QoS and fairness models, as well as hardware and platform improvements to enable the enforcement of application QoS and fairness requirements. Rafique et al. investigate micro-architectural extensions to support the OS for cache management [94]. There has been a number of works aimed at better understanding and modeling cache contention [11, 19] and job co-scheduling [26, 59]. Other hardware techniques to enable cache management have also received research attention [22, 52, 98, 113]. Suhendra [113] proposed partitioning and locking mechanisms to minimize unpredictable cache contention. Cache reconfiguration [98] has also been proposed as a mechanism to enable cache partitioning. Although these works show promising future directions for hardware and system designers to take when addressing these problems, unfortunately current commodity micro-architectures cannot support these solutions as they do not meet the micro-architectural assumptions made these works. Another very promising direction based on what is likely to be future hardware capabilities, is to leverage core specific dynamic voltage scaling as is presented by Herdirch, Illikkal, Iyer, et al [48].

While there has been much work on mitigating the performance interference due to resource contention on multicores, not much work is directly applicable to the datacenter co-location problem. Perhaps the work that is most relevant to our Bubble-Up approach is the Quarta work by Govindan et al. [41]; however this work requires access to physical memory addresses which can only be attained via custom changes to the OS, and as the authors themselves mention, such an approach is not feasible at user-level. One direction that has attracted much research attention is the management of shared cache and bandwidth through techniques such as resource partitioning [22,71,86,87,93,95,96,109,110,112,124], throttling [34] and adaptive cache replacement policies [57]. Previous work has also investigated providing QoS management for different applications on multicores [43,48,56,83]. While demonstrating promising results, the previous work on QoS management and resource

partitioning typically requires changes to the hardware design, which is not applicable to deployed servers. Software resource partitioning has also been proposed [28,70,115]. However, most software partitioning techniques focus on shared cache, while ignoring memory bandwidth contention, which is another main cause of performance interference. In general, our work is complementary to the above resource management research. While previous work focuses on providing resource management for performance isolation or performance optimization for co-running applications, our work focus on predicting which applications can be co-run with a given application without degrading its QoS beyond a certain threshold.

Previous work on scheduling to mitigate contention and to improve cache sharing is closely related to our work [25, 38, 60, 63, 127]. For an application, different co-runners may cause different amounts of performance interference on a CMP. The intuition of many contention-aware scheduling techniques is to classify applications based on how aggressively they are for shared memory resources and intelligently match highly aggressive applications with not aggressive applications to minimize the performance degradation [60,63,132]. However, most previous work has focused on maximizing the overall throughput or maintaining performance fairness. The approaches cannot address challenges when applications have different priorities and a subset of the applications have strict requirements in terms of the tolerable QoS degradation. The challenge for scheduling to provide such QoS guarantee is that the scheduler needs to accurately predict the potential performance degradation for co-running applications. Current classifiers in contention-aware schedulers only indirectly classify or rank applications in terms of their levels of aggressiveness [63, 123, 132] or predict their potential cache misses [19, 60, 76], but cannot provide direct accurate prediction in terms of performance degradation.

# Chapter 3

# **Execution Environments in WSCs**

# Contents

| 3.1 Dive | rsity in Execution Environments     | 24 |

|----------|-------------------------------------|----|

| 3.1.1    | WSC Test Platform                   | 24 |

| 3.1.2    | Microarchitectural Diversity        | 25 |

| 3.1.3    | Co-Runner Diversity                 | 26 |

| 3.1.4    | Motivation for Intelligent Mapping  | 28 |

| 3.1.5    | Benchmark Testbed                   | 28 |

| 3.1.6    | Implications on WSC Design          | 30 |

| 3.2 An ( | Opportunity Metric for EE Diversity | 30 |

In this chapter, we perform a study of EE diversity as it exists in commercial production WSCs and its impact on large-scale commercial web-service workloads. We also replicate this study using benchmark workloads on machines spanning multiple commodity machine configurations to provide repeatable experimentation. Finally, we introduce a metric, opportunity factor, which, given the application mix and machine mix in a WSC, quantifies an application's sensitivity to, and potential performance improvement from, exploiting the heterogeneity in that WSC.

| CPU                   | GHz     | Cores | L2/L3 | Nickname |

|-----------------------|---------|-------|-------|----------|

| Clovertown Xeon E5345 | 2.33ghz | 6     | 8mb   | Clover   |

| Istanbul Opteron 8431 | 2.4ghz  | 6     | 6mb   | Istan    |

| Westmere Xeon X5660   | 2.8ghz  | 6     | 12mb  | West     |

**Table 3.1:** Production Microarchitecture Mix

# 3.1 Diversity in Execution Environments

The potential benefit of exploiting, and adapting to, EE diversity within WSCs can be illustrated by the amount of performance variability suffered by applications due to varying their execution environments. Specifically, this variation includes changes in machine configurations and the set of possible co-running applications. In this section, we investigate this performance variability for large-scale commercial web-services. We focus not only on how sensitive each application's performance is to the EE diversity, but also the variance of this sensitivity across a set of applications. To investigate how our findings generalize to other applications and to provide repeatable experimentation, we also present results using an experimental testbed composed of benchmark applications in addition to the production study.

## 3.1.1 WSC Test Platform

We first conducted our experiments across the three production platform types presented in Table 3.1. These three platforms are commonly found coexisting in a single WSC in Google's production fleet. The applications we use in the study are described in Table 3.2. These applications cover nine large industry-strength workloads that are responsible for a significant portion of the cycles consumed in arguably the largest web-service WSC infrastructure in the world. Table 3.2 also presents a description for each application. Each application corresponds to an actual binary that is run in the WSC. These applications are part of a test infrastructure developed internally at Google composed of a host of Google workloads and machine clusters that have been both laboriously configured by a team of engineers for performance analysis and optimization testing across Google. Each application shown in the table operates on a repeatable log of thousands of queries from actual user

| workload         | description                                          | type        |

|------------------|------------------------------------------------------|-------------|

| bigtable         | A distributed storage system for managing            | user-facing |

|                  | petabytes of structured data                         |             |

| ads-servlet      | Ads sever responsible for selecting and placing tar- | user-facing |

|                  | geted ads on syndication partners sites              |             |

| maps-detect-face | Face detection for streetview automatic face blur-   | batch       |

|                  | ring                                                 |             |

| search-render    | Web-search frontend server, collect results from     | user-facing |

|                  | many backends and assembles html for user.           |             |

| search-scoring   | Web-search scoring and retrieval                     | user-facing |

| protobuf         | Protocol Buffer, a mechanism for describing ex-      | user-facing |

|                  | tensible communication protocols and on-disk         |             |

|                  | structures. One of the most commonly-used pro-       |             |

|                  | gramming abstractions at Google.                     |             |

| docs-analyzer    | Unsupervised Bayesian clustering tool to take key-   | both        |

|                  | words or text documents and "explain" them with      |             |

|                  | meaningful clusters.                                 |             |

| saw-countw       | Sawzall scripting language interpreter benchmark     | both        |

| youtube-x264yt   | x264yt video encoding.                               | batch       |

**Table 3.2:** Production WSC Applications

activity from production. The number of cores used by each application is configured to three for both solo and co-location runs. We also use this test infrastructure in Chapter 4.

# 3.1.2 Microarchitectural Diversity

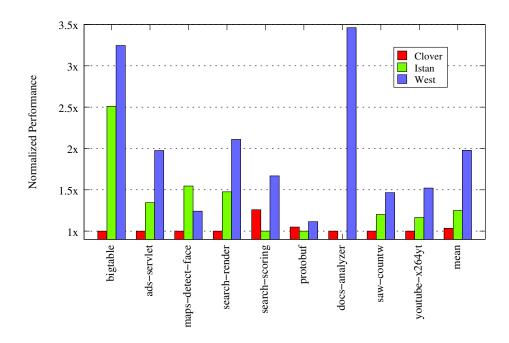

We first characterize the performance variability that arises due to microarchitectural diversity in WSCs. In addition to quantifying the magnitude of the performance variability, our study also aims to investigate firstly, whether microarchitectures consistently outperform others for all applications; and secondly, the differences in how sensitive the performance of each application is to varying platform types. As we discuss later in this section, the variance in performance sensitivity across all applications in a workload is an important indicator of the potential benefit from exploiting, and adapting to, EE diversity.

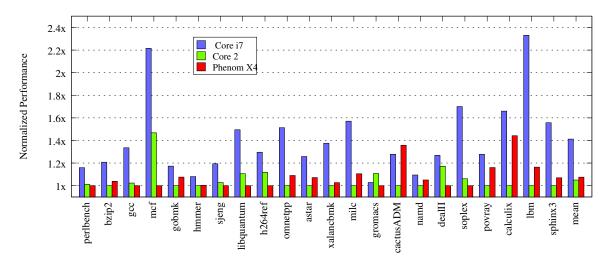

Figure 3.1 presents the experimental results for our Google testbed with 9 key Google applications running on 3 types of production machines. The y-axis shows the performance (average instructions per second) of each application on three types of machines, normalized by the worst performance among the three for each application. As Figure 3.1 shows, even among three architectures that are from competing generations, there is a significant per-

<sup>&</sup>lt;sup>1</sup>Docs-analyzer's data on Istanbul is missing because it is not configured for that particular platform.

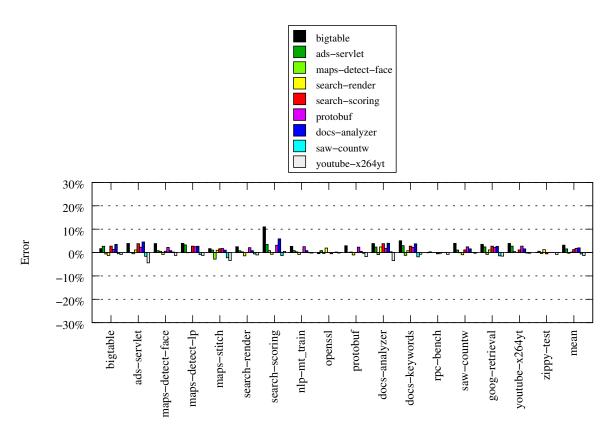

**Figure 3.1:** Performance comparison of key Google applications across three microarchitectures. Each cluster is normalized to poorest performing architecture (the higher the better)

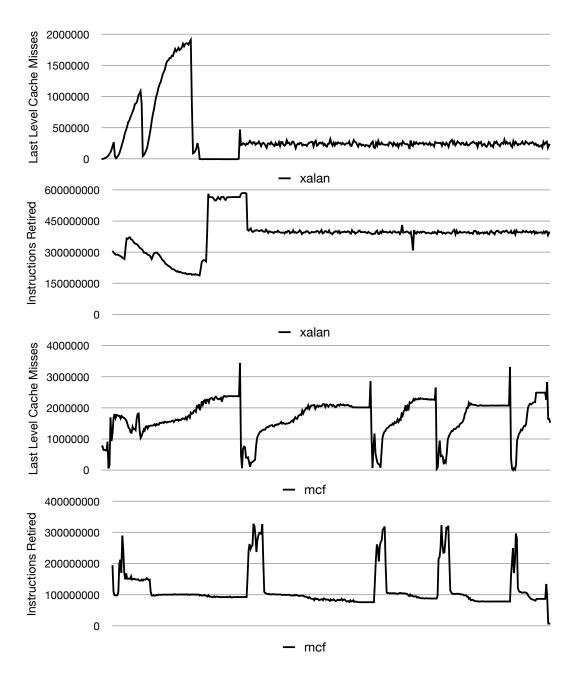

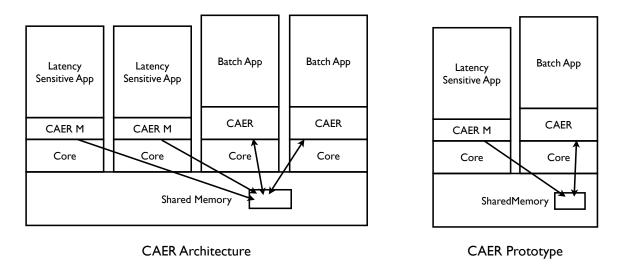

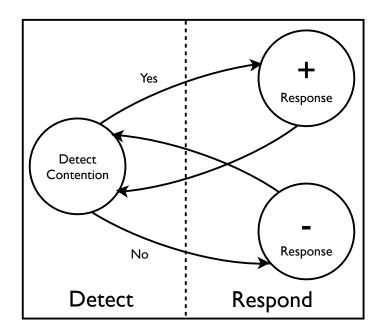

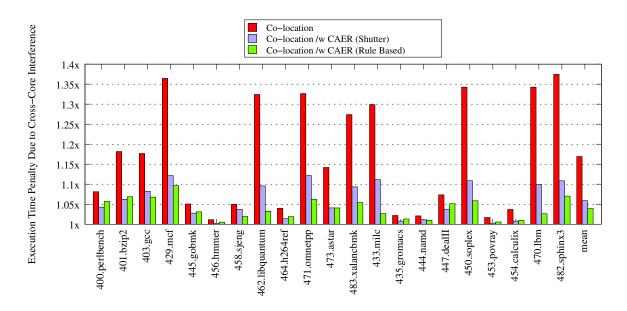

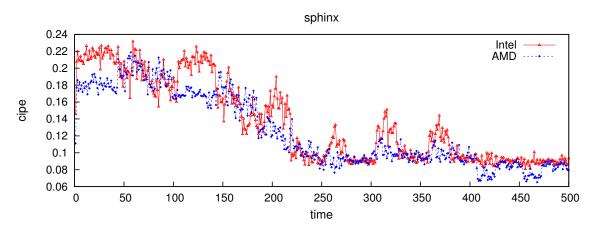

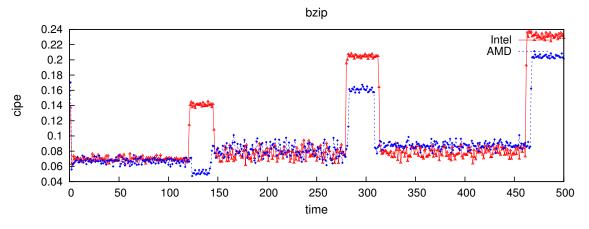

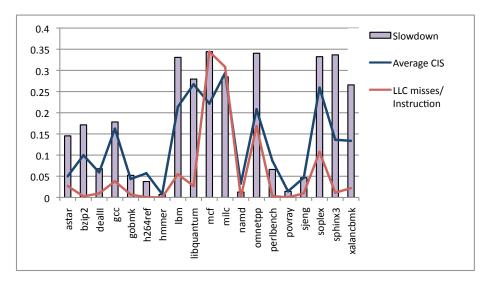

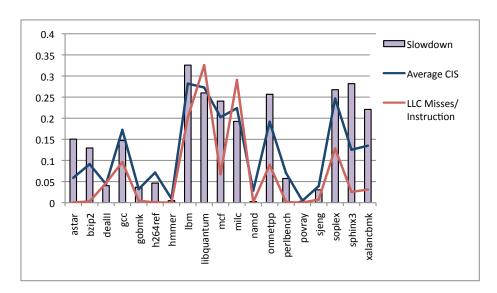

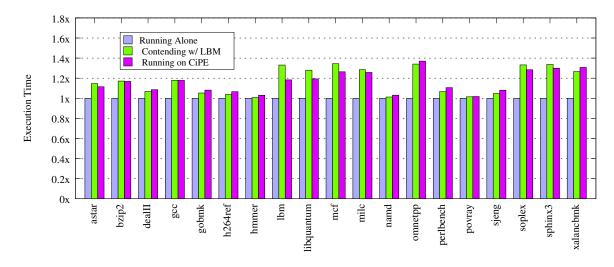

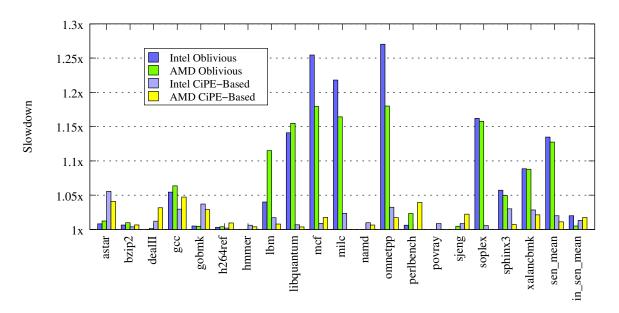

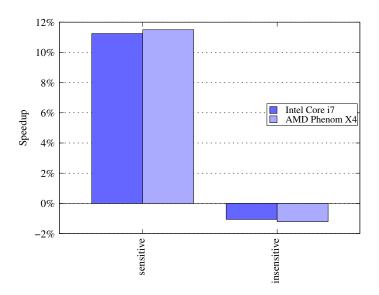

formance variability for Google applications. More interestingly, no platform is consistently better than the others in this experiment. Although the Westmere Xeon outperforms the other platforms for most applications, maps-detect-face running on the Istanbul Opteron outperforms the Westmere Xeon by around 25%. On the other hand, the Clovertown Xeon and Istanbul Opteron compete much more closely.