## First-Order Modeling Frameworks for Power-Efficient and Reliable Multiprocessor Systems

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science

University of Virginia

In Partial Fulfillment

of the requirements for the Degree

Doctor of Philosophy

Computer Science

by

Liang. Wang

May 2016

© Copyright May 2016

Liang Wang

All rights reserved

## **Approvals**

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

| Comp                      | puter Science                    |

|---------------------------|----------------------------------|

|                           |                                  |

| Li                        | ang Wang                         |

| Α                         | approved:                        |

| Kevin Skadron (Advisor)   | Mircea R. Stan                   |

| Gabriel Robins (Chair)    | Pradip Bose                      |

| James Cohoon              |                                  |

| Accepted by the School of | Engineering and Applied Science: |

| Craig H                   | . Benson (Dean)                  |

### **Abstract**

As the semiconductor industry keeps evolving at the pace predicted by Moore's Law, computer system architects are facing increasing challenges from the three major design constraints: performance, power, and reliability. Thermal constraints from a reasonable cooling cost do not scale well as technology evolves. The dwindling scaling on threshold voltage leads to a slower pace of supply voltage scaling. These two effects lead to an increasing power density in current and future technology generations. Reliability has emerged as a primary design constraint due to the smaller feature size and generally lower supply voltage for electronic devices. Transient errors caused by high-energy particle strike and voltage noises are expected to increase significantly in frequency. Performance improvement becomes more challenging for future architectures with limitations set by the power and the resilience constraints.

Integration of accelerators to create heterogeneous processors is becoming more common for both power and performance reasons. However, this adds one more dimension to the design space that is already complex due to technology variants, system organizations, application's variability, and so on. Therefore, high-level models are essential for system designers to explore the design space and make decisions in a timely manner. Additionally, the three design constraints compete with each other. For example, resilience-aware techniques, such as DMR and TMR, are expensive in terms of power and performance, low-power designs usually come with a price of lower speed. Consequently, it requires system designers to make trade-offs by considering all the three design constraints at the same time.

To address these challenges, we (1) propose an analytical modeling framework called Lumos that is capable of modeling power and performance for heterogeneous architectures with hardware

accelerators. Then we (2) use Lumos to explore the design space composed of CPU cores and accelerators, revealing important scaling trend for future heterogeneous architectures. We further (3) propose a rapid modeling framework to characterize resilience across a range of applications in DSP, and image processing domains; And finally we (4) propose an integrated framework to optimize energy-efficiency by trading off design constraints of power, performance and resilience.

## Acknowledgments

First, I would like to thank my advisor Prof. Kevin Skadron for guiding me through my pursue of the Ph.D. degree in the graduate school. He helped me develop my research topic, continuously improve the quality of the work, present and publish the work as an independent researcher. He also influenced me to improve my soft skills, such as professional networking, collaboration and communication with external researchers. Last, but probably the most importantly, he encouraged me to finish and helped me to build a strong mind to survive through those desperate moments on my way to the degree. Without these advising and mentoring, both academic and non-academic, I would never reach where I am right now.

A significant part of this dissertation came from my year-long internship at IBM T. J. Watson Research Center and follow-up collaborations. I would like to express my gratitude to my manager Dr. Pradip Bose and my mentor Dr. Jude A. Rivers. As renowned researchers in computer architecture, they guided me through the whole project from research definition, problem solving, implementation, and presentation to upper management. From their insightful guidance, I have gained exclusive learning experience not only in academic research, but also in the project management, patent application, etc. I would like to thank Dr. Alper Buyuktosunoglu as well, who shed innumerable amount of insightful comments on all projects I worked on at IBM. I would like to thank Dr. Ramon Bertran, Dr. Augusto Vega, Dr. Chen-yong Cher, Dr. Meeta S. Gupta for their various collaborations, and making my internship a remarkable experience. Most importantly, this dissertation would not have been possible without their help.

I would also like to thank my committee, Prof. Mircea R. Stan, Prof. James Cohoon, Prof. Gabriel Robins, and Dr. Pradip Bose, for taking time to review my proposal and dissertation as

well as for giving me many valuable comments about this work.

I am grateful for having so many friends both inside and outside the CS/ECE departments. The members and alumni of Kevin's LAVA lab have helped me in numerous ways. Especially, I thank Dr. Runjie Zhang, Dr. Shuai Che, Dr. Michael Boyer, Dr. Ke Wang, Prof. Brett H. Meyer, Jack Wadden, Deyuan Guo, Chunkun Bo, Elaheh Sadredini, for invaluable discussions on research ideas, and generous sharing of useful information of all kinds. I want to thank Xinfei Guo for his assistant on circuit simulation setup with the latest PTM, which contributed to build Lumos framework. In addition, I want to thank my fellow graduate students Yuchen Zhou, Yanqing Zhang, Wei Wang, Wei Zhang for setting examples of excellent researchers and motivating me with peer-pressure.

I want to thank my parents and in-laws for their unconditional love and support. I thank my wife Xiaohui for her endless love and support. I am grateful for her constant encouragement, advice, and accompany, which leads me through the most stressful, depressing, and even desperate times in my life. I dedicate this dissertation to all of them.

This work was supported by the SRC under GRC task 1972.001, the NSF under grants MCDA-0903471 and CNS-0916908, and Defense Advanced Research Projects Agency (DARPA), Microsystems Technology Office (MTO) under contracts no. HR0011-13-C-0022. The views expressed are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.

## **Contents**

| 1 | Intr | oductio | on .                                                                      | 1  |

|---|------|---------|---------------------------------------------------------------------------|----|

|   | 1.1  | Lumos   | s: An Analytical Modeling Framework for Design Space Exploration on Het-  |    |

|   |      | erogen  | neous Computer Architecture                                               | 3  |

|   | 1.2  | AFI: A  | Application-Level Fault Injection                                         | 5  |

|   | 1.3  | Resilie | ence-aware Optimization for Power-Efficiency with Real-Time Constraints . | 6  |

|   | 1.4  | Summ    | nary                                                                      | 7  |

| 2 | Lun  | nos: An | Analytical Modeling Framework for Multiprocessors                         | 8  |

|   | 2.1  | Relate  | d Work                                                                    | 10 |

|   | 2.2  | Lumos   | s Framework                                                               | 11 |

|   |      | 2.2.1   | Technology Modeling                                                       | 11 |

|   |      | 2.2.2   | Frequency Modeling                                                        | 13 |

|   |      | 2.2.3   | Core Modeling                                                             | 14 |

|   |      |         | 2.2.3.1 Power                                                             | 14 |

|   |      |         | 2.2.3.2 Performance                                                       | 15 |

|   |      |         | 2.2.3.3 Un-core Components                                                | 17 |

|   |      |         | 2.2.3.4 Baseline                                                          | 17 |

|   |      | 2.2.4   | Accelerator Modeling                                                      | 18 |

|   |      | 2.2.5   | Workload Modeling                                                         | 18 |

|   |      | 2.2.6   | System Configuration                                                      | 21 |

|   |      | 2.2.7   | Discussions                                                               | 22 |

| ix |

|----|

|    |

|   |     | 2.2.8   | Lumos Release                                                          | 22 |

|---|-----|---------|------------------------------------------------------------------------|----|

|   | 2.3 | Design  | Space Exploration                                                      | 23 |

|   |     | 2.3.1   | Effectiveness of Dim Silicon with Near-threshold Operation             | 23 |

|   |     | 2.3.2   | Dim Silicon with Reconfigurable Logic                                  | 25 |

|   |     | 2.3.3   | Dim Silicon with ASICs                                                 | 29 |

|   |     | 2.3.4   | Dim Silicon with Accelerators(RL and ASIC) on General-Purpose Workload | 31 |

|   |     | 2.3.5   | Benefit of ASIC Accelerators                                           | 32 |

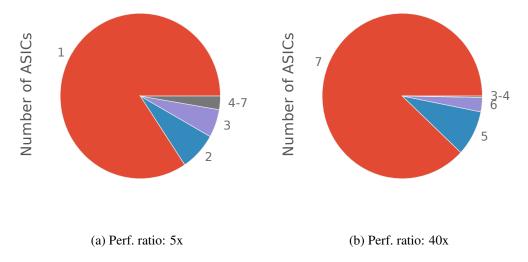

|   |     | 2.3.6   | Sensitivity of ASIC Performance Ratio                                  | 33 |

|   |     | 2.3.7   | Alternative Serial Cores                                               | 35 |

|   | 2.4 | Conclu  | isions                                                                 | 36 |

| 3 | Lum | os+: Do | esign Space Exploration for MPSoCs                                     | 38 |

|   | 3.1 | Related | d Work                                                                 | 39 |

|   | 3.2 | Lumos   | +                                                                      | 40 |

|   |     | 3.2.1   | Technology Scaling Model                                               | 40 |

|   |     | 3.2.2   | Performance Model                                                      | 41 |

|   |     | 3.2.3   | Workload Model                                                         | 42 |

|   |     | 3.2.4   | Reconfiguration Overhead                                               | 43 |

|   | 3.3 | Domai   | n-Specific Applications                                                | 43 |

|   |     | 3.3.1   | BFopt                                                                  | 44 |

|   |     | 3.3.2   | Area Allocations on Accelerators                                       | 45 |

|   |     | 3.3.3   | Number of Dedicated Accelerators                                       | 46 |

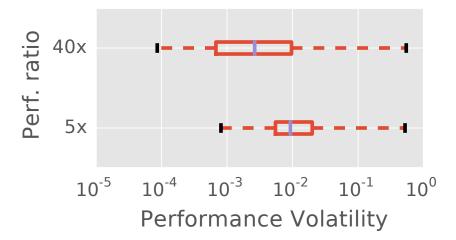

|   |     | 3.3.4   | Performance Volatility                                                 | 47 |

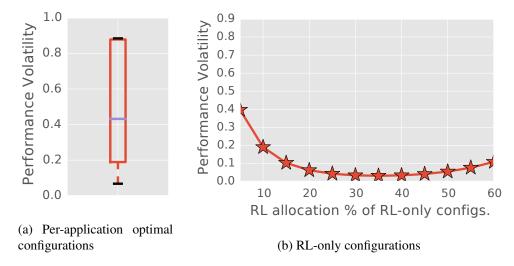

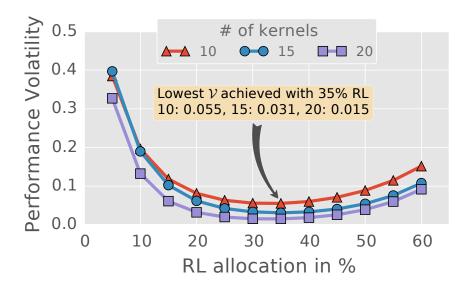

|   | 3.4 | Genera  | al-Purpose Applications                                                | 48 |

|   |     | 3.4.1   | GAopt                                                                  | 49 |

|   |     | 3.4.2   | Importance of Reconfigurable Accelerators                              | 50 |

|   | 3.5 | Reconf  | figuration Overhead                                                    | 53 |

|   | 3.6 | Conclu  | sions                                                                  | 54 |

Contents

| 4 | AFI   | : Applic | cation-Level Fault Injection                                          | 55 |

|---|-------|----------|-----------------------------------------------------------------------|----|

|   | 4.1   | Relate   | d Work                                                                | 56 |

|   | 4.2   | Applic   | cation Level Resilience                                               | 58 |

|   |       | 4.2.1    | SER Taxonomy                                                          | 58 |

|   |       | 4.2.2    | Evaluating a Target System for SER                                    | 60 |

|   | 4.3   | Applic   | cation Fault Injection                                                | 61 |

|   | 4.4   | Experi   | iment Setup                                                           | 64 |

|   |       | 4.4.1    | PERFECT Suite                                                         | 64 |

|   |       |          | 4.4.1.1 PERFECT Application1 (PA1)                                    | 64 |

|   |       |          | 4.4.1.2 Space-Time Adaptive Processing (STAP)                         | 65 |

|   |       |          | 4.4.1.3 Synthetic Aperture Radar (SAR)                                | 66 |

|   |       |          | 4.4.1.4 Wide Area Motion Imagery (WAMI)                               | 66 |

|   |       | 4.4.2    | Statistical Significance                                              | 67 |

|   | 4.5   | Resilie  | ence Characterization                                                 | 68 |

|   |       | 4.5.1    | Case I: Single Bit Errors                                             | 68 |

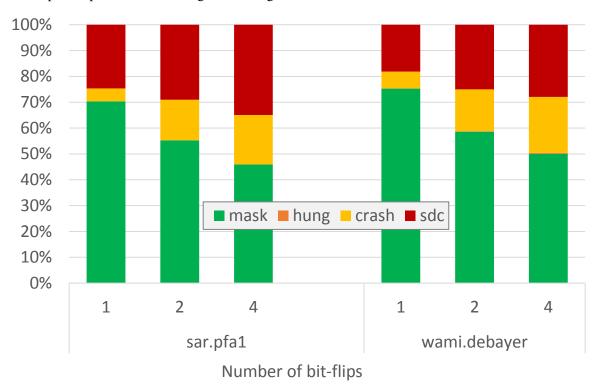

|   |       | 4.5.2    | Case II: Multiple Bit Errors                                          | 71 |

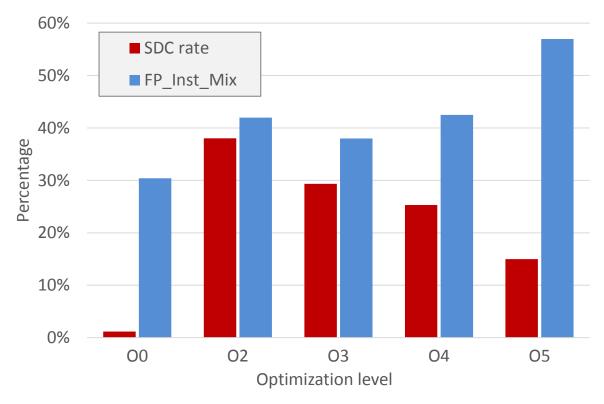

|   |       | 4.5.3    | Case III: Compiler Optimization                                       | 74 |

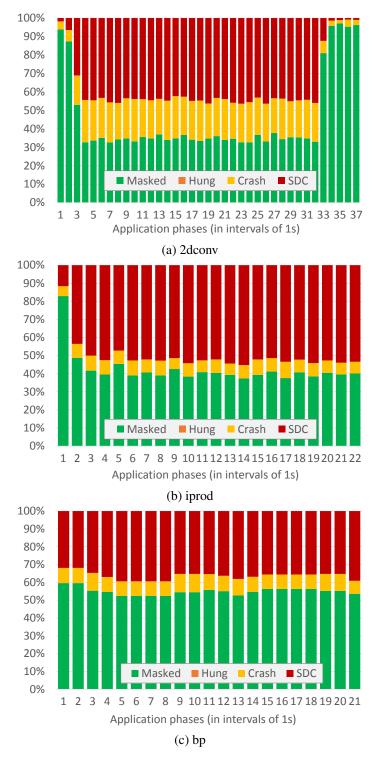

|   |       | 4.5.4    | Case IV: Temporal Vulnerability                                       | 76 |

|   | 4.6   | Discus   | ssion of Characterization Results                                     | 76 |

|   | 4.7   | Conclu   | usions                                                                | 79 |

| 5 | PEA   | RL: Po   | ower-Efficient Embedded Processing with Resilience and Real-Time Con- | _  |

|   | strai | ints     |                                                                       | 80 |

|   | 5.1   | Relate   | ed Work                                                               | 81 |

|   | 5.2   | PEAR     | L Facility and Methodology                                            | 82 |

|   |       | 5.2.1    | Workflow Models                                                       | 82 |

|   |       | 5.2.2    | Individual Application Programs                                       | 83 |

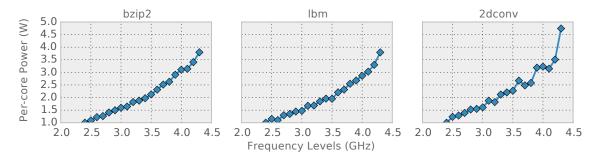

|   |       | 523      | Power and Performance Modeling                                        | 84 |

| Bi | bliogr | aphy     |                                                 | 112 |

|----|--------|----------|-------------------------------------------------|-----|

| A  | Glos   | sary     |                                                 | 110 |

|    |        | 6.2.3    | Resilience-Aware Energy-Efficiency Optimization | 109 |

|    |        | 6.2.2    | Application-Level Resilience                    | 108 |

|    |        | 6.2.1    | Design Space Exploration                        | 107 |

|    | 6.2    | Future   | Directions                                      | 107 |

|    | 6.1    | Dissert  | ation Summary                                   | 106 |

| 6  | Cone   | clusions | and Future Work                                 | 106 |

|    | 5.6    | Conclu   | isions                                          | 104 |

|    |        | 5.5.2    | Evaluation                                      | 103 |

|    |        | 5.5.1    | Dynamic Iterative Approach                      | 99  |

|    | 5.5    | Dynam    | nic, Run-time Efficiency Optimization           | 99  |

|    |        | 5.4.2    | DAGopt Evaluation                               | 97  |

|    |        | 5.4.1    | DAGopt                                          | 96  |

|    | 5.4    | Graph    | Workflow Optimization                           | 96  |

|    |        | 5.3.4    | Impact of Execution Time Scaling                | 95  |

|    |        | 5.3.3    | Impact of Power Variation                       | 93  |

|    |        | 5.3.2    | Energy Efficiency Improvement                   | 91  |

|    |        | 5.3.1    | LinOpt                                          | 90  |

|    | 5.3    | Linear   | Workflow Optimization                           | 89  |

|    |        | 5.2.5    | Workflow Synthesis                              | 88  |

|    |        | 5.2.4    | Resilience Modeling                             | 86  |

# **List of Figures**

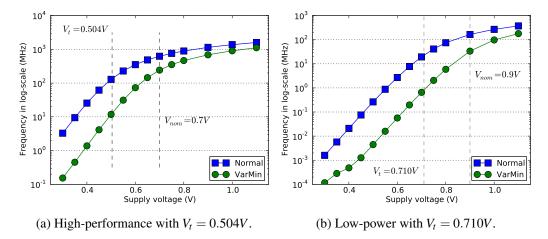

| 2.1 | Voltage-frequency scaling characterization on a 32-bits ripple carry adder (RCA)    |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | simulated at 16nm, subjecting to process variation (VarMin). $V_t$ is the threshold |    |

|     | voltage, and $V_{nom}$ is the nominal supply voltage                                | 14 |

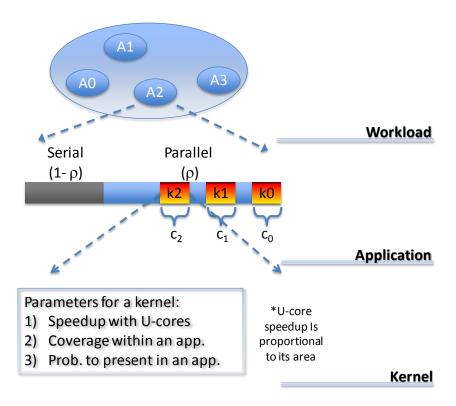

| 2.2 | A workload is composed of applications. An application may have several comput-     |    |

|     | ing kernels, which can be accelerated by many-core parallelization, RL, and ASIC.   | 19 |

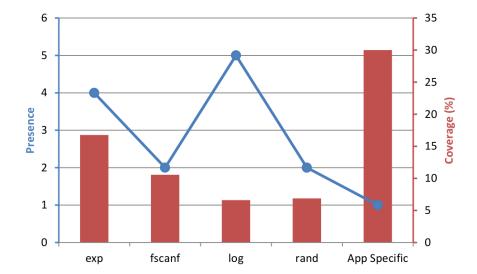

| 2.3 | Kernels coverage and presence. Kernels are extracted from PARSEC applications,      |    |

|     | excluding x264. The coverage percentages of exp, fscanf, log, and rand are aver-    |    |

|     | aged across their all occurrences. The coverage percentage of the "app specific" is |    |

|     | the average of all application-specific kernels                                     | 20 |

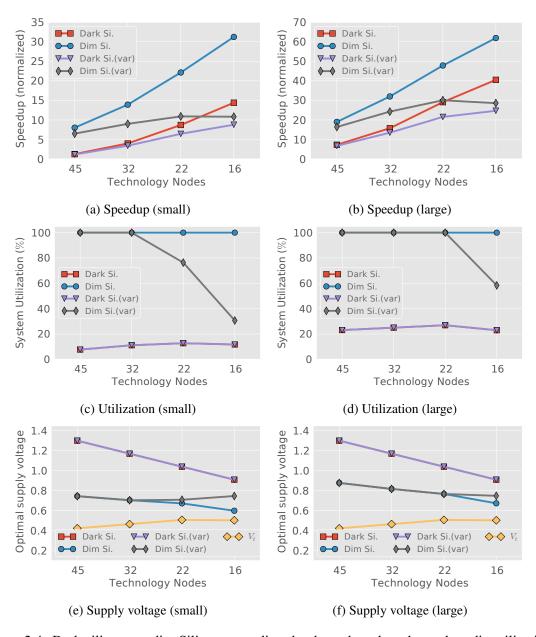

| 2.4 | Dark silicon vs. dim Silicon, regarding the throughput based speedup, die utiliza-  |    |

|     | tion, and the supply voltage with optimal throughput. Two system budgets (see       |    |

|     | Table 2.5) are compared: a small-budget system plotted on the left, and a large-    |    |

|     | budget system plotted on the right                                                  | 24 |

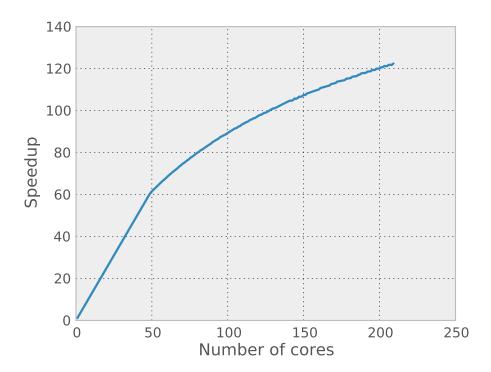

| 2.5 | The overall throughput-based speedup of in-order (IO) cores at 16nm with high-      |    |

|     | performance (HP) process. The system is configured with large budget of $200  mm^2$ |    |

|     | in area and 120 W in TDP. Diminishing returns are observed starting around 50       |    |

|     | active cores                                                                        | 25 |

List of Figures xiii

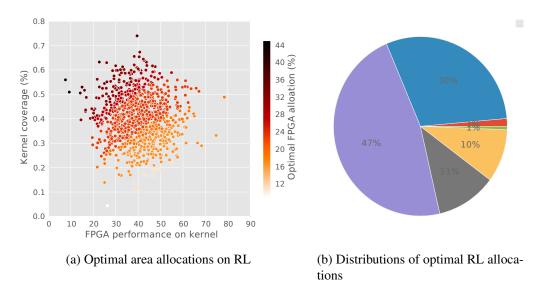

| 2.6 | Optimal area allocations on reconfigurable logic (RL) accelerators. Derived from      |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | exhaustive search, optimal RL allocations for each application are plotted in 2.6a.   |    |

|     | In this plot, each of dots represents an application that has been characterized by   |    |

|     | the coverage of the kernel (Y-axis) and the kernel's u-core performance parameter     |    |

|     | (X-axis). The colors of dots indicate the optimal RL allocation in percentage for     |    |

|     | the given application, the darker the color the higher the optimal allocation. On     |    |

|     | the other hand, the distribution of optimal allocations is illustrated by a pie-chart |    |

|     | in 2.6b. Percentage numbers within the pie-chart suggest the distribution of each     |    |

|     | category, while the percentage numbers around the pie-chart indicate the range of     |    |

|     | optimal RL allocations within each category                                           | 26 |

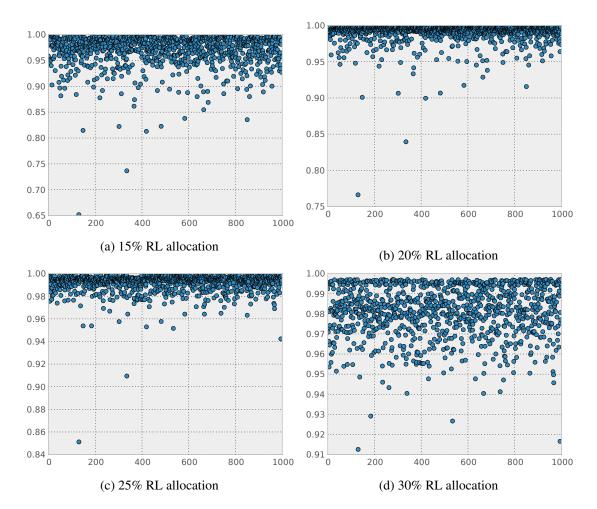

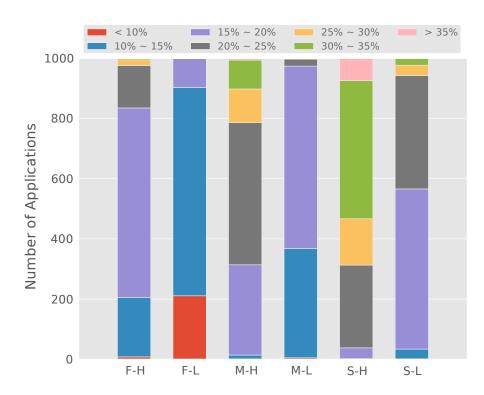

| 2.7 | The performance of systems with reconfigurable logic accelerators. For each ap-       |    |

|     | plication, we plot the performance of the given system relative to the system of the  |    |

|     | optimal RL allocation for the application. Four systems with alternative RL alloca-   |    |

|     | tions are shown at 15% in Figure 2.7a, 20% in Figure 2.7b, 25% in Figure 2.7c, and    |    |

|     | 30% in Figure 2.7d. X-axis is the index number of an application within the work-     |    |

|     | load. Y-axis is the relative performance achieved by the given system configuration   |    |

|     | relative to the performance achieved by the system with the optimal RL allocation.    |    |

|     | Note that each of dots is normalized to different baseline since the optimal RL allo- |    |

|     | cation is application-specific (see Figure 2.6)                                       | 28 |

| 2.8 | Optimal RL allocations with alternative distributions for speedup and coverage.       |    |

|     | Distributions for speedup cover three scenarios from slow to fast, while distribu-    |    |

|     | tions for coverage cover two scenarios from low to high. Parameters for these         |    |

|     | distributions are detailed in Table 2.6                                               | 29 |

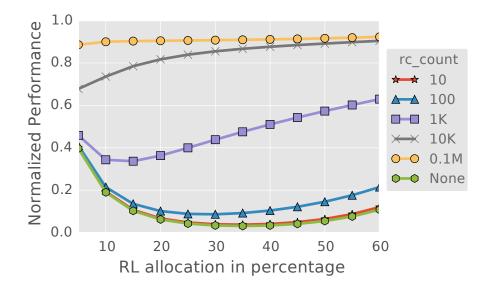

| 2.9 | Speedup of various RL allocations. Optimal performance achieved at around 20%         |    |

|     | RL allocation                                                                         | 30 |

List of Figures xiv

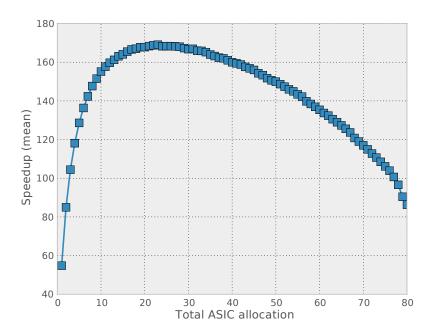

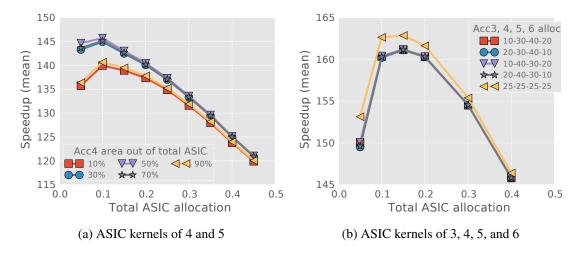

| 2.10 | Speedup of a system composed of dim silicon and ASICs. We show configurations           |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | with tow accelerators 2.10a and four accelerators 2.10b. The X-axis is the total        |    |

|      | allocation to ASIC kernels, relative to the die area budget. The legend labels show     |    |

|      | the allocation of a kernel relative to the total ASIC allocation                        | 30 |

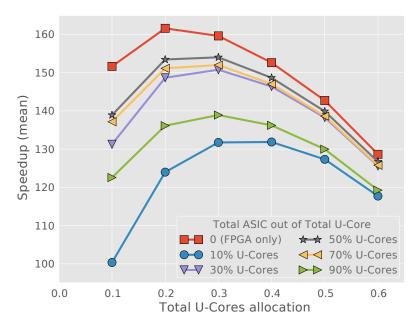

| 2.11 | Speedup of a system composed of dim silicon, RL, and ASICs. The X-axis is the           |    |

|      | total allocation to U-cores, including both RL and ASIC accelerators, relative to the   |    |

|      | die area budget. Legend labels indicate the total allocation of ASIC accelerators,      |    |

|      | relative to the total U-cores allocation. We assume an evenly distributed alloca-       |    |

|      | tion among ASIC accelerators, since it shows the best performance in the previous       |    |

|      | analysis                                                                                | 31 |

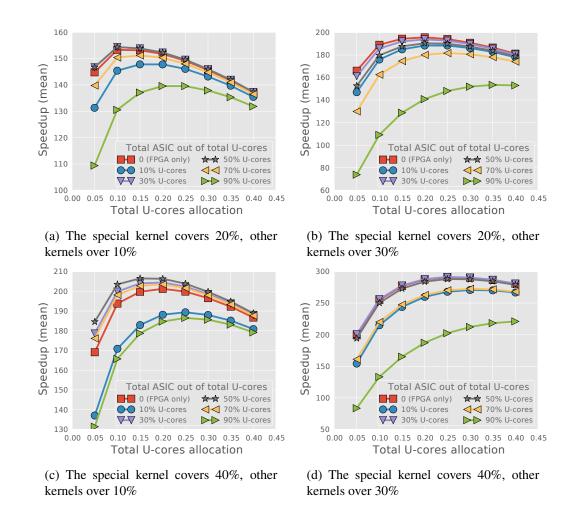

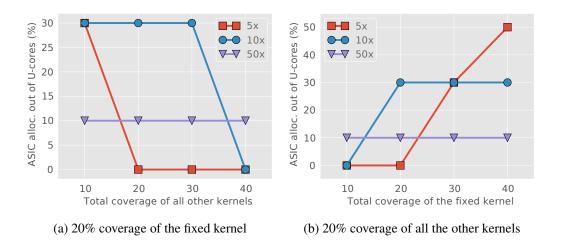

| 2.12 | To study the benefit of a dedicated ASIC accelerator, we add one special kernel to      |    |

|      | the set of ten kernels used before. We vary the total coverage of all other kernels     |    |

|      | at 10% (left plots) and 30% (right plots), while setting the coverage of the special    |    |

|      | kernel at $20\%$ (upper plots) and $40\%$ (lower plots). The results show that the ded- |    |

|      | icated ASIC accelerator in only beneficial when its targeted kernel has a dominant      |    |

|      | coverage with applications, e.g. in Figure 2.12c                                        | 33 |

| 2.13 | Sensitivity study on ASIC performance ratio                                             | 34 |

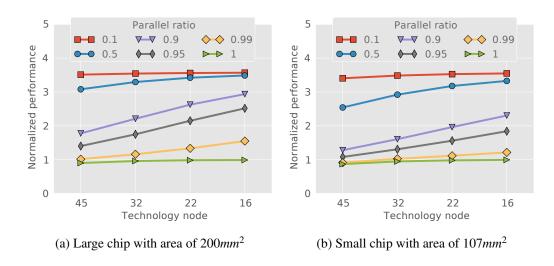

| 2.14 | Relative performance by using O3 core to run the serial part of an application.         |    |

|      | System budget is large in 2.14a and small in 2.14b, as characterized in Table 2.5.      |    |

|      | Y-axis is the performance normalized to the system at the same technology node,         |    |

|      | which only includes in-order cores and uses one of the in-order cores as the serial     |    |

|      | core                                                                                    | 35 |

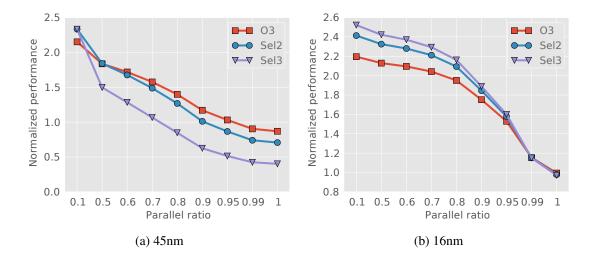

| 2.15 | Performance comparison among systems implementing the serial core as an out-            |    |

|      | of-order (O3) core, core-selectability of two O3 cores (Sel2), and core-selectability   |    |

|      | of three O3 cores (Sel3). The system budget is small from Table 2.5. Y-axis is          |    |

|      | the performance normalized to the system at the corresponding technology node,          |    |

|      | which only includes in-order cores and uses one of in-order cores as the serial core.   | 37 |

List of Figures xv

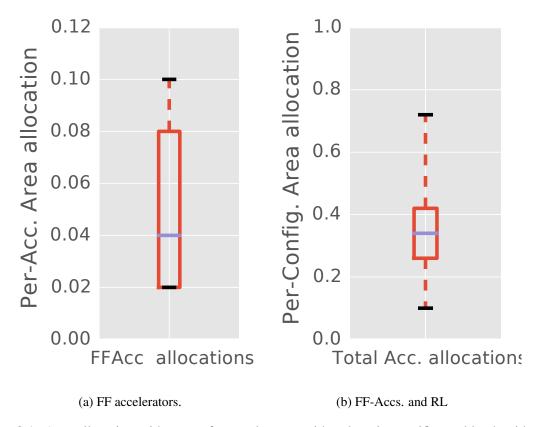

| 3.1 | Area allocation with <i>BFopt</i> for accelerators with a domain-specific workload, with |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | an FF-Acc speedup of 40X. The box extends from the lower to upper quartile values        |    |

|     | of the data, with a line at the median, and the whiskers indicating min/max of the       |    |

|     | data. (a) distribution of per-accelerator area allocations on FF-Accs within these       |    |

|     | optimal configurations. Allocations on FF-Accs range from 2% to 10% with a step          |    |

|     | size of 2%. (b) distribution of total accelerator allocations (including RL and FF-      |    |

|     | Accs) of each optimal configuration                                                      | 45 |

| 3.2 | Number of dedicated ASIC accelerators in optimal configurations, plotted in pie          |    |

|     | charts                                                                                   | 46 |

| 3.3 | Distribution of performance volatility of optimal configurations for ASIC perfor-        |    |

|     | mance ratio of 5x, and 40x. The box-plot setting is the same as described in Fig-        |    |

|     | ure 3.1                                                                                  | 47 |

| 3.4 | Performance volatility comparison between per-application optimal configurations         |    |

|     | and RL-only configurations. Performance ratio of FF-Accs is 40x                          | 51 |

| 3.5 | Performance volatility comparison between per-application optimal configurations         |    |

|     | and RL-only configurations. Performance ratio of FF-Accs is 40x                          | 52 |

| 3.6 | Impact of reconfiguration overhead on performance volatility of RL-only config-          |    |

|     | urations, as a function of the number of reconfiguration options per application.        |    |

|     | "None" means that reconfiguration overhead is ignored                                    | 53 |

| 4.1 | SER taxonomy                                                                             | 58 |

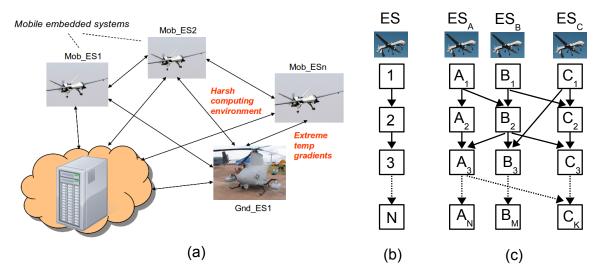

| 4.2 | Cloud-backed airborne embedded system network, which operates under harsh con-           |    |

|     | ditions                                                                                  | 60 |

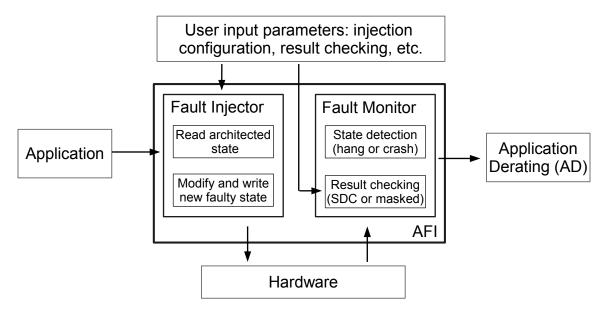

| 4.3 | Block diagram of Application-Level Fault Injection framework (AFI). AFI includes         |    |

|     | two major components: 1) a fault injector which launches an application and injects      |    |

|     | error guided by user input, and 2) a fault monitor which determines the outcome of       |    |

|     | injected error into one of four outcomes as masked, SDC, crash, and hung                 | 62 |

List of Figures xvi

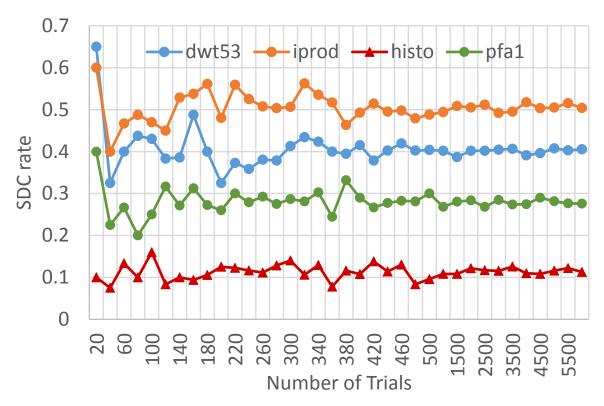

| 4.4  | Sensitivity study on the number of injections to achieve statistical stability. X-axis |    |

|------|----------------------------------------------------------------------------------------|----|

|      | is the number of injections, while Y-axis shows the masking rate of corresponding      |    |

|      | experiments. Three well known benchmarks are choose as conjugate gradient (CG-         |    |

|      | A) from NAS benchmark suite, bzip2 from SPEC2006, and matrix multiply (mmm).           | 68 |

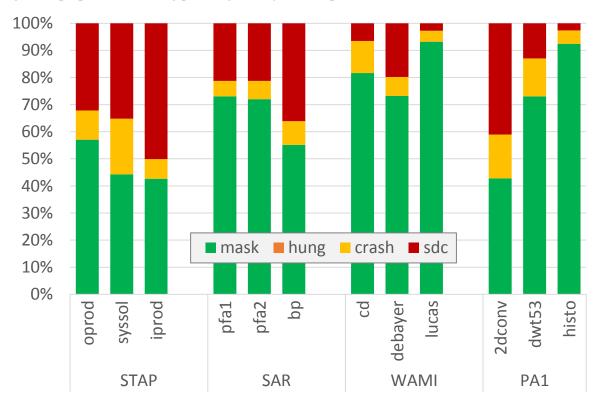

| 4.5  | General-purpose register injections                                                    | 69 |

| 4.6  | Floating point register injections                                                     | 70 |

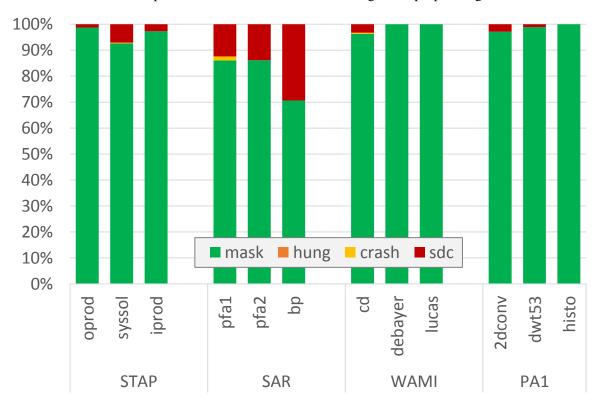

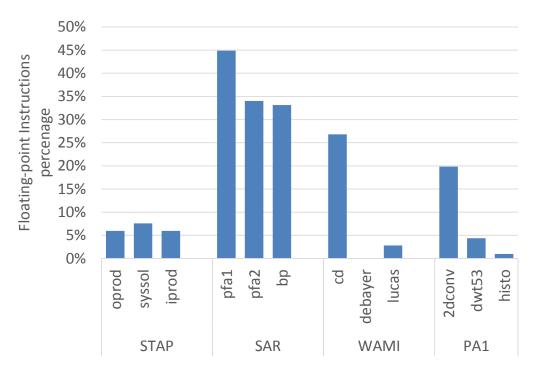

| 4.7  | Floating point instruction percentage                                                  | 71 |

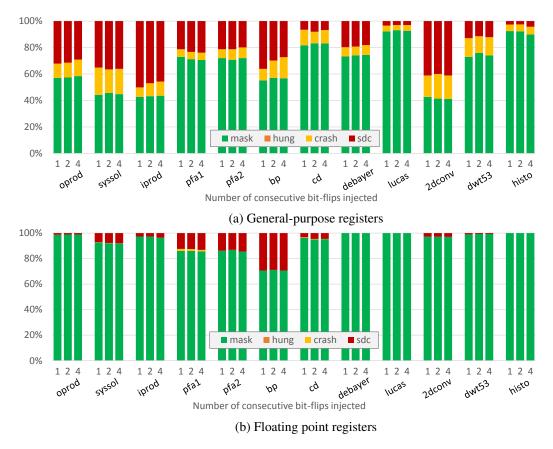

| 4.8  | Multi-bit error injections                                                             | 72 |

| 4.9  | Results for alternate multi-bit error injection model (GPRs) to mimic the SEMU case.   | 73 |

| 4.10 | SDC rates of sar.bp with different compiler optimization levels                        | 74 |

| 4.11 | Phased characterization on (a) pa1.2dconv, (b) stap.iprod, and (c) sar.bp              | 75 |

| 4.12 | Single event multi-bit upset (SEMU) trends for CMOS PD-SOI [66]                        | 78 |

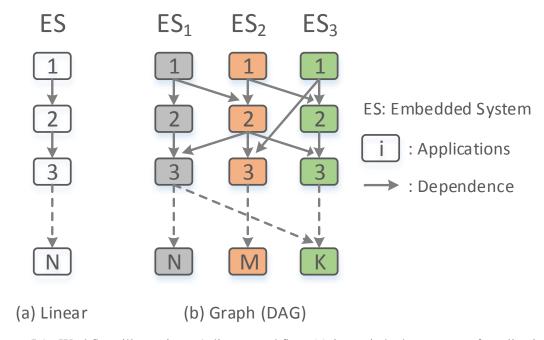

| 5.1  | Workflow illustration. A linear workflow (a) is a stitched sequence of applications,   |    |

|      | modeling a single embedded system (ES). A graph workflow (b) is a set of lin-          |    |

|      | ear workflows with inter-dependencies, modeling multiple embedded systems with         |    |

|      | inter-system communications                                                            | 83 |

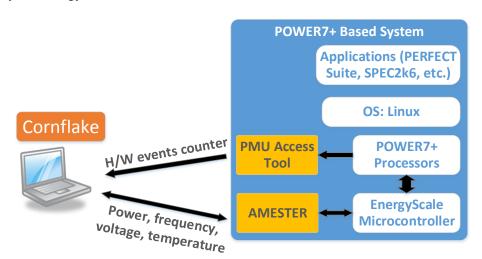

| 5.2  | Experimental system block diagram                                                      | 85 |

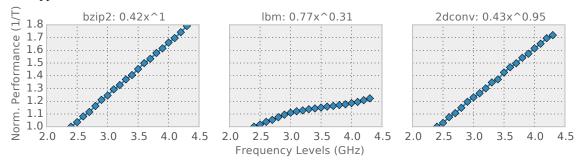

| 5.4  | Using frequency masks to denote the running frequency domains of each application.     | 90 |

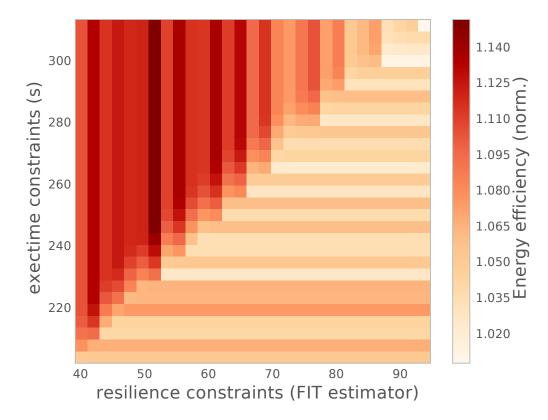

| 5.5  | LinOpt improvement in performance/Watt (GOPS/W) over SimpleOpt across a                |    |

|      | range of constraints. The workflow is a stitched sequence of all 20 characterized      |    |

|      | applets. Constraints of resilience and execution time are plotted on X-axis and Y-     |    |

|      | axis respectively. Energy efficiency obtained by LinOpt under various constraints      |    |

|      | are normalized to the baseline SimpleOpt under the same constraint, and plotted in     |    |

|      | a heat-map with dark color indicating the highest, while light color indicating the    |    |

|      | lowest                                                                                 | 92 |

List of Figures xvii

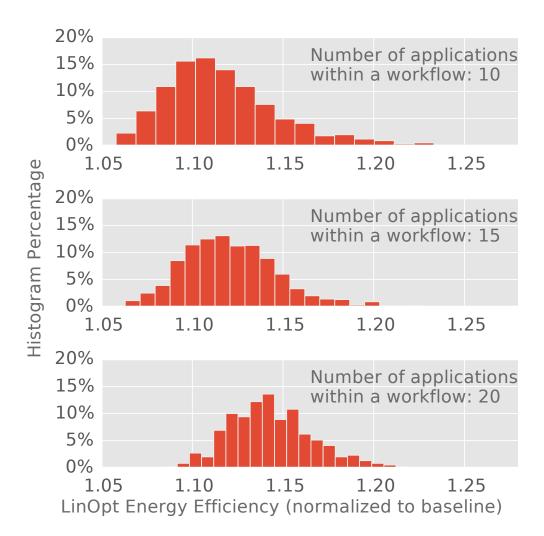

| 5.6  | Histogram of the maximum improvement in BIPS/W achieved by LinOpt over the                            |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | baseline across 1,000 generated workflows with a given number of applications.                        |    |

|      | Power and resilience constraints are set as the maximum of applications within a                      |    |

|      | workflow running at the nominal frequency level. X-axis is the relative energy                        |    |

|      | efficiency of LinOpt normalized to the baseline. Y-axis is histogram in percentage.                   | 93 |

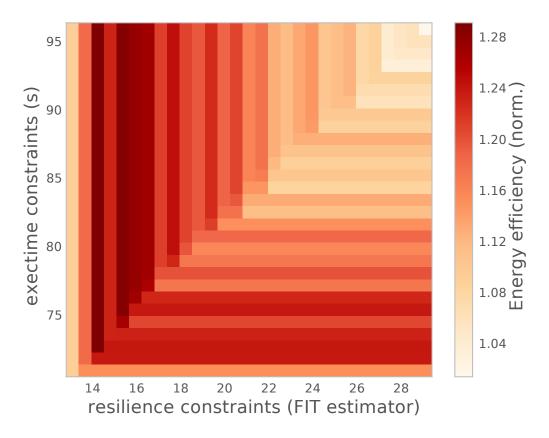

| 5.7  | LinOpt benefit over SimpleOpt for a workflow composed of two synthetic applets                        |    |

|      | based on 2dconv. The syn-hp doubles the power characterization of 2dconv to serve                     |    |

|      | as a high-power variant, and the syn-lp reduce the power characterization by 90%                      |    |

|      | to serve as a low-power variant                                                                       | 94 |

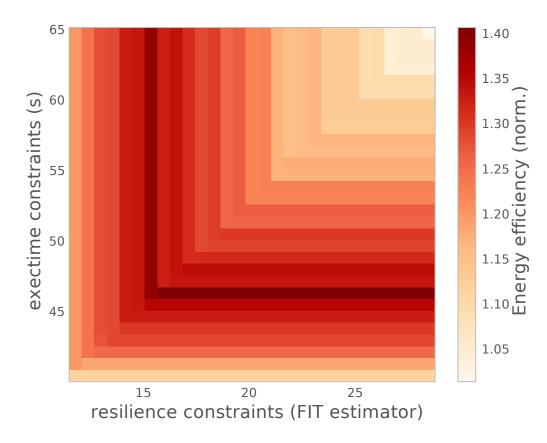

| 5.8  | LinOpt improvement in performance/Watt (GOPS/W) over SimpleOpt when the                               |    |

|      | targeting workflow compose of 2dconv and lbm, of which have quite different ex-                       |    |

|      | ecution time characterization with regard to voltage-frequency scaling. The work-                     |    |

|      | flow includes 7 applets as 3 2dconv followed by 4 lbm                                                 | 95 |

| 5.9  | DAGopt illustration on a synthetic workflow. Numbers in each node indicate the ex-                    |    |

|      | ecution time of the corresponding application in seconds. Suppose that the deadline                   |    |

|      | constraint is 85s. In (a), all applications are initialized with the lowest frequency                 |    |

|      | levels. In (b), DAGopt identifies the critical path as $A \rightarrow C \rightarrow D$ , then invokes |    |

|      | LinOpt on the path. Upon a successful optimization, DAGopt sets optimized fre-                        |    |

|      | quency levels as indicated by the new execution time, and marks all nodes within the                  |    |

|      | path as processed. In (c), DAGopt identifies the next_critical_path as $A \to B \to D$                |    |

|      | and invokes LinOpt on the path while only selecting higher frequency levels for A                     |    |

|      | and $D$ than their already chosen levels. DAGopt terminates after this step since all                 |    |

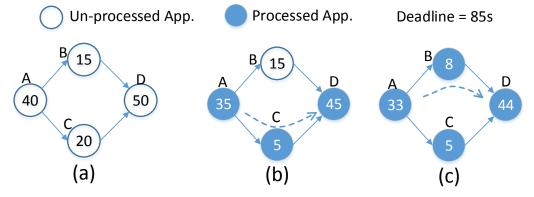

|      | the applications within the workflow have been marked as processed                                    | 97 |

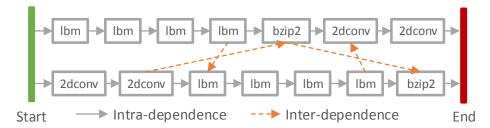

| 5.10 | An illustrative graph workflow, consisting of 2 threads with inter-dependencies in-                   |    |

|      | dicated by dashed arrows.                                                                             | 98 |

List of Figures xviii

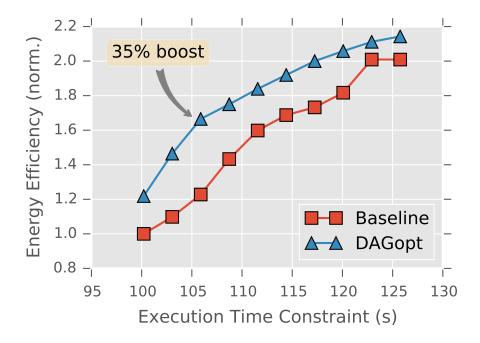

| 5.11 | DAGopt energy efficiency improvement over simple single-frequency selection                  |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | heuristics, evaluated on an illustrative workflow (Figure 5.10). Power and resilience        |     |

|      | constraints are set as the maximum of applications within a workflow running at the          |     |

|      | nominal frequency level. Energy efficiency values, plotted on Y-axis, are normal-            |     |

|      | ized to the baseline under the execution time constraint of 100s (the leftmost data          |     |

|      | point). DAGopt outperforms the baseline in all cases, with up to 35% boost when              |     |

|      | the execution time constraint is 106s                                                        | 99  |

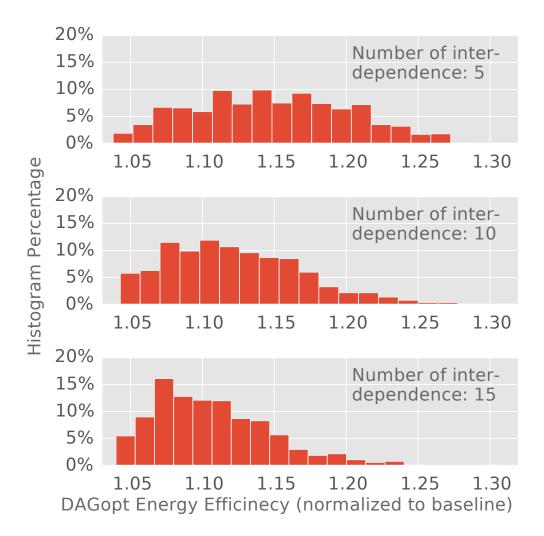

| 5.12 | Histogram of the maximum relative BIPS/W obtained by DAGopt over the base-                   |     |

|      | line across 1,000 generated workflows. The number of inter-dependencies is varied            |     |

|      | from 5 to 15. Power and resilience constraints are set as the maximum of these               |     |

|      | metric values across applications within a workflow running at the nominal fre-              |     |

|      | quency level. The X-axis is the relative energy efficiency normalized to the base-           |     |

|      | line, Y-axis is the histogram distribution percentage. It shows that with fewer inter-       |     |

|      | dependencies, DAGopt is good to achieve an energy efficiency boost over the base-            |     |

|      | line by 10% to 20%, while as the number of inter-dependencies increases to 15, the           |     |

|      | improvement in energy efficiency reduces to the range of 5% to 10%                           | 100 |

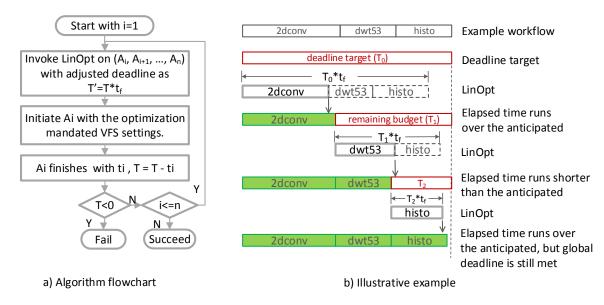

| 5.13 | An iterative algorithm adapting to dynamic execution time variations. In (a), the            |     |

|      | algorithm is presented as a flowchart, and in (b), a step-by-step example illustrates        |     |

|      | the dynamic optimization algorithm. The illustrative linear workflow is a stitched           |     |

|      | sequence of three applications: 2dconv, dwt53, and histo                                     | 101 |

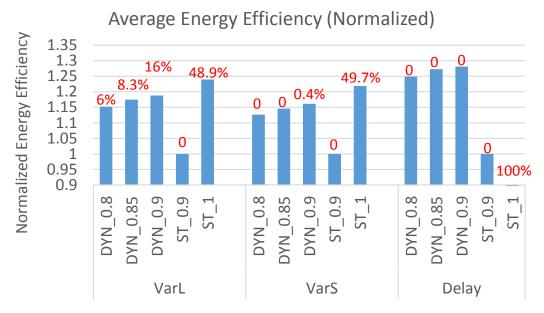

| 5.14 | Dynamic simulation results. For the described scenarios (VarL, VarS, and Delay),             |     |

|      | we compare the dynamic iterative approach with 3 values of $min(t_f)$ (DYN <sub>-</sub> 0.9, |     |

|      | DYN_0.85, and DYN_0.8), and two two cases of static LinOpt with (ST_0.9) and                 |     |

|      | without (ST_1) conservative provision on deadline constraints. The Y-axis is the av-         |     |

|      | erage energy efficiency computed in BIPS/W normalized to ST_0.9. The percentage              |     |

|      | on top of a bar is its deadline miss ratio. Dynamic approaches generally achieve en-         |     |

|      | ergy efficiency close to the aggressive static approach (ST_1), while maintaining            |     |

|      | miss ratios close to the conservative static approach (ST 0.9)                               | 104 |

## **List of Tables**

| 2.1 | Characteristics of PTM                                                            | 12 |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | Technology scaling for high-performance (HP) processes and low-power (LP) pro-    |    |

|     | cesses. The area scaling is assumed to be ideal so that the area of a single core |    |

|     | shrinks by 2x per technology node                                                 | 12 |

| 2.3 | Baseline core                                                                     | 17 |

| 2.4 | Summary of parameters                                                             | 21 |

| 2.5 | System Configurations                                                             | 22 |

| 2.6 | Alternative parameters                                                            | 27 |

| 2.7 | O3 Core                                                                           | 35 |

| 3.1 | Parameters for <i>GAopt</i> using DEAP framework                                  | 50 |

| 4.1 | Result checking mechanism of PERFECT applications                                 | 67 |

# **Chapter 1**

## Introduction

As the semiconductor industry keeps evolving at the pace predicted by Moore's Law [53,54], computer system architects are facing increasing challenges from the three major design constraints: performance, power, and reliability.

First of all, performance has always been a primary constraint for system architects. However, it is getting increasingly hard to improve the performance, especially the performance of a single core. Chip-multiprocessors (CMP) have been widely accepted to be promising to deliver scalable performance over generations. Nevertheless, its effectiveness has been largely reduced due to physical constraints arising from recent technology scaling trends (this will be discussed in detail later). On the other hand, hardware specialization is another promising approach to achieve better performance in an efficient way. Unfortunately, the heterogeneity among conventional cores and the specialized hardware increases the design complexity significantly, not to mention the substantially higher engineering cost associated with the customized hardware.

Secondly, power consumption has been widely accepted as another first-class constraint ever since early this century [10]. Thermal constraints from a reasonable cooling cost set the total system power, also known as the "Power Wall," which does not scale well as the technology evolves. The recent trend in technology scaling poses even more challenges on power constraints. Threshold voltage scales down slowly in current and future technology generations to keep leakage power under control. The dwindling scaling on threshold voltage leads to a slower pace of supply voltage scaling. Since the switching power scales as  $CV^2f$ , Dennard Scaling can no longer be maintained,

and power density keeps increasing. Furthermore, the cooling cost and on-chip power delivery implications limit the increase of a chip's thermal design power (TDP). As Moore's Law continues to double transistor density across technology generations, total power consumption will soon exceed TDP, and if high supply voltage must be maintained, future chips will only support a small fraction of active transistors, leaving others inactive, a phenomenon referred to as "dark silicon" [26, 84].

Last but not least, reliability has been evolved to be a primary constraint for system designers, which traditionally is a serious concern only for mission-critical systems, such as unmanned aerial vehicles (UAVs), or high-end server systems, such as IBM POWER series processors. The transistor density keeps doubling every eighteen months, as Moore's Law predicts. The growing density results in a higher probability of manufacturing imperfection and raises the likelihood of a chip to fail. Additionally, technology scaling keeps delivering smaller feature size and reduced supply voltage for electronic devices. Single-event upsets (SEUs) caused by high-energy particle strike are exacerbated at lower voltages, due to the critical charge ( $Q_{crit}$ ) required to cause a latch or SRAM bit flip diminishes correspondingly. Similarly, transient errors caused by voltage noise also increase in frequency under low-voltage operations. To make the situation even worse, errors are expensive to detect and recover in terms of power and performance. Redundancy-based techniques, such as dual-modular redundancy (DMR) and triple-modular redundancy (TMR), suffer from considerable overheads in system power and area. On the other hand, checkpoint-based techniques have nonnegligible run-time overhead, and could potentially prevent forward progress if the soft error rate (SER) is too high. Meanwhile, extra energy consumed by recovery hurts the overall energy efficiency of the system. This leaves computer systems with worse performance as well as even more pressure on an already stringent power budget.

Integration of accelerators to create heterogeneous processors is becoming more common for both power and performance reasons. However, this adds one more dimension to the design space that is already complex due to technology variants, system organizations, applications variability, and so on. As a result, high-level models are essential for system designers to explore the design space and make decisions in a timely manner. Additionally, the three design constraints compete with each other. For example, resilience-aware techniques, such as DMR and TMR, are expen-

sive in terms of power and performance; low-power designs are implemented at a price of lower speed. Therefore, it requires system designers to make trade-offs by considering all the three design constraints at the same time.

To address these challenges, we propose a set of frameworks to model power-efficiency, resilience, and performance for future heterogeneous multi-core systems. The proposed frameworks are flexible and easily integrated to perform holistic analysis regarding all design constraints. Our approaches consist of the following major research tasks:

- Design and implement an analytical modeling framework that is capable of modeling both power and performance for heterogeneous architecture with hardware accelerators under different technology variants.

- 2. Explore the design space composed of conventional CPU cores and hardware accelerators, revealing potential trends of system designs for future heterogeneous architectures.

- 3. Propose an approach to analyze and evaluate accelerator-rich heterogeneous architectures exploiting an advanced optimization algorithm.

- 4. Design and implement a rapid resilience modeling framework based on application-level fault injections, then characterize resilience across a range of applications in DSP, and image processing domains.

- 5. Propose an integrated framework to optimize energy-efficiency by trading off design constraints of power and resilience in the context of real-time embedded processing.

# 1.1 Lumos: An Analytical Modeling Framework for Design Space Exploration on Heterogeneous Computer Architecture

Quantitative models for power and performance play an essential role in computer architecture research. As a result, researchers have proposed enormous amount of models through decades'

research within the field, they vary in complexities and accuracies. Theoretically, direct measurements on a real machine are considered as the most accurate modeling approach, however, it comes with the limitation that quite a few architectural parameters can be changed. It is almost impossible to use this approach to explore innovative architectures nor to experiment with new features on existing architecture. The next level of approaches exploits architecture simulators to adopt power and performance of the target computer systems. Although simulators are popular for architectural research and development in the last couple of decades [2, 7, 10], they suffer from orders of magnitude slower simulation throughput than native execution. And it is prohibitively expensive to use simulation-based approaches to do a broad exploration in a large design space.

Analytical models based on Amdahl's Law [1] have gained popularity recently [26, 35], primarily for the interest of design space exploration of future computer architectures. These efforts in early-stage exploration are not aimed at proposing specific architectural features. Instead, their goals are trying to find important implications for architecture designs. For example, in [26], authors showed that an increasing amount of die area will be inactive, a.k.a. "dark silicon," due to the more stringent relative power budget as the manufacturing technology advancing to the next couple of generations. The observation advocated a shift of focus from multi-core scaling to more power-efficient computing units (e.g. hardware accelerators).

In Chapter 2, we propose an analytical modeling framework, called "Lumos", that is capable of modeling the power and the performance of conventional CPU cores, as well as hardware accelerators. Using "Lumos", we explore the design trade-offs among CPU cores and various accelerators. We show that despite the performance benefits from operating CPU cores at a substantially lower supply voltage, it is even more promising to include hardware accelerators as the building block in heterogeneous systems. Furthermore, in Chapter 3, we design a systematic approach to analyze accelerator-rich heterogeneous architectures with regard to domain-specific and general-purpose applications. From our extensive design space exploration, we show that reconfigurable accelerators are preferable over dedicated accelerators when overall performance across a set of applications is of particular interest.

## 1.2 AFI: Application-Level Fault Injection

Due to technology scaling, reliability has emerged as a first-order design constraint for mainstream computer systems. The shrinking feature size makes circuits more vulnerable to permanent and transient faults. Permanent faults are caused by manufacturing imperfection as well as the aging effect in transistors. Transient faults, also known as soft errors, are due to high-energy particle strikes [4] and voltage droops [58]. Both types of faults are important from the perspective of system reliability. However, in this dissertation, we mainly focus on transient faults since they are more common.

Fortunately, a given pair of a machine architecture and an application offers significant masking of effects in the face of spurious bit-flips. As a result, the raw soft error rate (SER) of processor chips – even though it may increase with device density and lower voltages – is at least partially offset by large degrees of masking. For a given machine, different applications or phases within an application workflow present different degrees of masking. It is also true that despite errors in a particular program output, consuming applications can often actuate actions accurately, thereby providing error-free outcome at the end. For example, an image processing and recognition algorithm can tolerate numerous pixel errors in the input data that may have been produced by an earlier image-scanning step.

To quantify the SER with regard to various applications, in Chapter 4, we present a framework based on a software-implemented fault injection (SWIFI) tool, called AFI. It features a runtime-independent triggering mechanism to enable flexible parallel experiment runs, as well as a mechanism to characterize only the region-of-interest (ROI) of an application through source code annotation. The tool is built on top of standard debugging interface and performance counters which are available in most of the modern operating systems and processors. AFI is currently implemented on AIX<sup>TM</sup> for POWER7 processor for demonstration purpose. It can be easily ported to other platforms such as X86 on Linux. Using AFI, We characterize the transient error tolerance of a set of applications from DSP and image processing domains. Various error injection models are used to see if the relative ordering of applications gets changed while measuring resilience metrics. Additionally,

we show that error tolerance is a strong function of the compiler optimization level. This provides a static optimization knob for application scientists in the quest to optimize performance/watt while meeting resilience targets. Finally, we explain changes in the degree of error tolerance by analyzing simple workload metrics like the dynamic instruction frequency mix.

# 1.3 Resilience-aware Optimization for Power-Efficiency with Real-Time Constraints

A powerful control parameter for power management of embedded processor systems is dynamic voltage-frequency scaling (DVFS). However, soft error rates (SERs) are known to increase sharply as the supply voltage is scaled downward [70]. Hence, in order to preserve system resilience levels, it is important to apply voltage scaling carefully, keeping in mind the varying levels of vulnerability to SER within an application's execution profile. On the other hand, overclocking or turbo-boosting (with higher voltages applied if/as necessary) to meet the real-time deadlines, comes at the cost of higher power (or current) density and temperature (as well as higher gate-oxide field stress), which results in higher hard-failure rates.

In Chapter 5, we consider a class of embedded systems that require high levels of power-performance efficiency while meeting mission-critical reliability specifications and real-time performance targets. Such systems require an energy optimization protocol that is cognizant of the variable resiliency needs and properties of the executed application. A representative example of such an embedded system of interest is a single unmanned aerial vehicle (UAV) or a swarm of such UAVs. These are typically engaged in remote sensing of ground images, for the purposes of reconnaissance, object recognition/tracking and tactical response. We propose PEARL, a novel software modeling framework that enables users to: (a) *statically* prepare application workflows for energy-optimized resilience; and (b) explore *run-time* deployment options in targeted embedded systems. The overall goal is to maximize performance per watt, while meeting real-time deadlines and resilience-related constraints (dictated by effective SER and maximum power dissipation). PEARL stands for Power Efficient And Resilient embedded processing with reaL-time constraints.

## 1.4 Summary

By finishing these research tasks, I contribute to a set of modeling frameworks with regard to three important design factors: power, performance, and resilience. Lumos/Lumos+ provide mechanisms for system designers to rapidly explore design points of future heterogeneous architectures, and make early decisions before spending significant efforts on a single path. AFI helps application developer to better understand applications' resilience. System designers can also benefit from resilience characterization by applying application-specific tuning algorithms. Finally, we demonstrate an optimization scenario where trade offs are made among power, performance, and resilience to achieve the best energy efficiency while still maintain the real-time deadline.

## **Chapter 2**

# Lumos: An Analytical Modeling Framework for Multiprocessors

Threshold voltage scales down more slowly in current and future technology nodes to keep leakage power under control. In order to achieve fast switching speed, it is necessary to keep transistors operating at a considerably higher voltage than their threshold voltage. Therefore, the dwindling scaling on threshold voltage leads to a slower pace of supply voltage scaling. Since the switching power scales as  $CV^2f$ , Dennard Scaling can no longer be maintained, and power density keeps increasing. Furthermore, cooling cost and on-chip power delivery implications limit the increase of a chip's thermal design power (TDP). As Moore's Law continues to double transistor density across technology nodes, total power consumption will soon exceed TDP. If high supply voltage must be maintained, future chips will only support a small fraction of active transistors, leaving others inactive, a phenomenon referred to as "dark silicon" [26, 84].

Since dark silicon poses a serious challenge for conventional multi-core scaling [26], researchers have tried different approaches to cope with dark silicon, such as "dim silicon" [36] and customized accelerators [79]. Dim silicon, unlike conventional designs working at nominal supply, aggressively lowers supply voltage close to the threshold to reduce dynamic power. The saved power can be used to activate more cores to exploit more parallelism, trading off per-core performance loss with better overall throughput [27]. However, with near-threshold supply, dim silicon designs suffer from diminishing throughput returns as the core number increases. On the other

hand, customized accelerators are attracting more attention due to their orders of magnitude higher power efficiency than general-purpose processors [16, 32]. Although accelerators are promising in improving performance with less power consumption, they are built for specific applications, have limited utilization in general-purpose applications, and sacrifice die area that could be used for more general-purpose cores. Poorly-utilized die area would be very costly if there are more efficient solutions, in terms of opportunity cost. Therefore, the utilization of each incremental die area must be justified with a concomitant increase in the average selling price (ASP).

To investigate the performance potential of dim cores and accelerators, we have developed a framework called *Lumos*, which extends the well-known Amdahl's Law, and is accompanied by a statistical workload model. We investigate two types of accelerators, application-specific logic (ASIC) and RL. When we refer to RL, we generically model both fine-grained reconfigurability such as FPGA and coarse-grained such as Dyser [31]. We also assume the reconfiguration overhead is overwhelmed by sufficient utilization of each single configuration. In this chapter, we show that

- Systems with dim cores achieve up to 2x throughput over conventional CMPs, but with diminishing returns.

- Hardware accelerators, especially RL, are effective to further boost the performance of dim cores.

- Reconfigurable logic is preferable over ASICs on general-purpose applications, where kernel commonality is limited.

- A dedicated fixed logic ASIC accelerator is beneficial either when: 1) its targeted kernel has significant coverage (e.g. twice as large as the total of all other kernels), or 2) its speedup over RL is significant (e.g. 10x-50x).

This work has been published in IEEE Micro [87].

#### 2.1 Related Work

The power issue in future technology scaling has been recognized as one of the most important design constraints by architecture designers [56,84]. Esmaeilzadeh et al. performed a comprehensive design space exploration on future technology scaling with an analytical performance model in [26]. While primarily focusing on maximizing single-core performance, they did not consider lowering supply voltage, and concluded that future chips would inevitably suffer from a large portion of dark silicon. In [9], Borkar and Chien indicated potential benefits of near-threshold computing with aggressive voltage-scaling to improve the aggregate throughput. We evaluate near-threshold in more detail with the help of Lumos calibrated with circuit simulations. In [36], Huang et al. performed a design space exploration for future technology nodes. They recommended dim silicon and briefly mentioned the possibility of near-threshold computing. Our work exploits circuit simulation to model technology scaling and evaluates in detail the potential benefit of improving aggregate throughput by dim silicon and near-threshold computing. In short, Lumos allows design space exploration for cores running at near-threshold supply factoring in the impact of process variations.

Another set of studies has evaluated the benefit of hardware accelerators as a response to dark silicon. Chung et al. studied the performance potentials of GPU, FPGA, and ASIC in [16], regarding physical constraints of area, power, and memory bandwidth. Although a limited number of applications were studied in their work, our work corroborates that reconfigurable accelerators, such as FPGA, are more competitive than dedicated ASICs. Wu and Kim did a study across several popular benchmark suites regarding the targets to be accelerated in [91]. Their work suggested a large number of dedicated accelerators are required to achieve a moderate speedup due to the minimal functional level commonality in benchmark suites like SPEC2006. This is consistent with our observation that dedicated fixed logic accelerators are less beneficial due to limited utilization across applications in a general-purpose workload, and the importance of efficient, reconfigurable accelerators. In [81], Tseng and Brooks build an analytical model to study trade-offs between latency and throughput performance under different power budgets and workloads. However, the

model lacks the support of voltage and frequency scaling, especially near threshold and the capability of hardware accelerator performance modeling, limiting the design space explorations of future heterogeneous architectures. In [96], Zidenberg et al. propose MultiAmdahl model to study the optimal allocations to each type of computational units, including conventional cores and u-cores. The MultiAmdahl model cannot support voltage scaling and near threshold effects. Therefore, its design space exploration capability is limited to heterogeneous systems under dark/dim silicon projections. Lumos takes a broader view of these issues, by providing a highly configurable tool for exploring the design space composed of conventional cores, various forms of accelerators, and low-voltage operation, with various power constraints and various workload characteristics.

#### 2.2 Lumos Framework

The design space of heterogeneous architectures with accelerators is too huge to use extensive architectural simulation in a feasible way. To enable rapid design space explorations, we build Lumos, a framework putting together a set of analytical models for power-constrained heterogeneous many-core architectures with accelerators. Lumos extends the simple Amdahl's Law model by Hill and Marty [35] with physical scaling parameters calibrated by circuit simulations with a modified Predictive Technology Model [12]. Lumos is composed of:

- 1. a technology model for inter-technology scaling;

- 2. a model for voltage-frequency scaling;

- 3. a model evaluating power and performance of conventional cores;

- 4. a model evaluating power and performance of accelerators;

- 5. a model for workloads and applications.

#### 2.2.1 Technology Modeling

Technology scaling is built based on the modified PTM, which tunes transistor models with more up-to-date parameters extracted from recent publications [12]. Two types of technology variants

are investigated, a high-performance process and a low-power process. The primary difference is that low-power processes have a higher threshold, as well as a higher nominal supply voltage, than high-performance processes for every single technology node, as shown in 2.1.

Table 2.1: Nominal supply voltage  $(V_{nom})$  and threshold voltage  $(V_t)$  for each PTM technology variants. Voltage units are volt (V).

|       |           | 45 <i>nm</i> | 32 <i>nm</i> | 22nm  | 16 <i>nm</i> |

|-------|-----------|--------------|--------------|-------|--------------|

| High  | $V_{nom}$ | 1.0          | 0.9          | 0.8   | 0.7          |

| Perf. | $V_t$     | 0.424        | 0.466        | 0.508 | 0.505        |

| Low   | $V_{nom}$ | 1.1          | 1.0          | 0.95  | 0.9          |

| Power | $V_t$     | 0.622        | 0.647        | 0.707 | 0.710        |

Inter-technology scaling mainly deals with scaling ratios for the frequency, the dynamic power, and the static power. From the circuit simulation, we compare the frequency, the dynamic power, and static power at the nominal supply for each of technology nodes. We assume CPU cores will have the same scaling ratio as the circuit we simulated. As shown in Table 2.2, the scaling factors of high-performance variants are normalized to 45nm, while the scaling factors of low-power variants are normalized to their high-performance counterparts.

Table 2.2: Technology scaling for high-performance (HP) processes and low-power (LP) processes. The area scaling is assumed to be ideal so that the area of a single core shrinks by 2x per technology node.

| Tech. (nm) | Freq. | Switch<br>Power | Static<br>Power |

|------------|-------|-----------------|-----------------|

| 45         | 1.0   | 1.0             | 1.0             |

| 32         | 0.95  | 0.49            | 0.31            |

| 22         | 0.79  | 0.21            | 0.12            |

| 16         | 0.66  | 0.09            | 0.13            |

<sup>(</sup>a) HP, normalized to 45nm

Tech. Static Freq. Switch Power Power (nm) 0.0084 45 0.27 0.30 32 0.28 0.320.042 22 0.34 0.23 0.26 22 0.26 0.40 0.49

<sup>(</sup>b) LP, normalized to HP counyerparts

#### 2.2.2 Frequency Modeling

Voltage-to-frequency scaling is modeled by interpolating empirical results from circuit simulations. We use a 32-bits ripple carry adder (RCA) to emulate the core frequency changes subject to various supply voltages. The adder is synthesized with a standard-cell library [38] at 45nm. Sizes of transistors in the post-synthesized net-list are scaled to other technology nodes. These circuit net-lists are then simulated using a modified version of Predictive Technology Model (PTM) for the bulk devices. Note that Lumos is not limited to the bulk devices, but can be extended to other technologies by applying the same RCA characterization with the target technology library. More specifically, Lumos can be extended with minimal efforts to support FinFET devices by using the latest PTM from [75].

The switching speed of transistors scales exponentially to the threshold voltage when it is operating at near-threshold voltage; therefore, the working frequency of a circuit in the near-threshold region is extremely sensitive to the threshold voltage. To investigate the fluctuation of frequency subject to process variations, the test circuit has been simulated with Monte-Carlo analysis, assuming a standard Gaussian distribution with  $3-\sigma$  on the threshold voltage of transistors.

The results for 16nm are shown in Figure 2.1. For the high-performance process plotted in Figure 2.1a, the maximum performance penalty due to process variations is less than 10% when the circuit is operated at higher voltages around 1V. However, when supply voltage approaches the threshold, frequency penalty increases significantly to more than 90%, which means an order of magnitude slowdown on frequency. A similar trend is observed in Figure 2.1b for the low-power process, though the low-power process suffers from a larger percentage of frequency loss than the high-performance process even at a higher supply voltage, e.g. 1V.

Figure 2.1: Voltage-frequency scaling characterization on a 32-bits ripple carry adder (RCA) simulated at 16nm, subjecting to process variation (VarMin).  $V_t$  is the threshold voltage, and  $V_{nom}$  is the nominal supply voltage.

#### 2.2.3 Core Modeling

#### 2.2.3.1 Power

Core power consumption is modeled as two major sources, dynamic power due to transistor switching and static power due to leakage. Therefore, per-core power is given by

$$P_{\text{total}} = P_{\text{dynamic}} + P_{\text{leakage}} \tag{2.1}$$

Generally speaking, dynamic power is given by

$$P_{\text{dynamic}} = \alpha \cdot C_{eff} \cdot V_{dd}^2 \cdot f \tag{2.2}$$

where  $\alpha$  is the activity factor,  $C_{eff}$  is the effective capacitance,  $V_{dd}$  is supply voltage, and f is the core running frequency. We assume a constant activity factor and effective capacitance when the core frequency is scaled with various supply voltages. Therefore, dynamic power changes quadratically to supply voltage and linearly to frequency. According to [11], the static power of a

system is given by

$$P_{\text{leakage}} = V_{dd} \cdot N \cdot k_{design} \cdot \hat{I}_{leak} \tag{2.3}$$

where  $V_{dd}$  is supply voltage, N is the number of transistors,  $k_{design}$  is a device-specific constant, and  $\hat{I}_{leak}$  is the normalized per-transistor leakage current. We assume the normalized per-transistor leakage current is proportional to the leakage current of a single transistor, which, according to [64], is given by

$$I_{leak} = I_0 \cdot 10^{\frac{V_{gs} - V_t + \eta V_{ds}}{S}} \cdot \left(1 - e^{-\frac{V_{ds}}{V_{th}}}\right)$$

(2.4)

where  $V_t$  is the threshold voltage,  $\eta$  is the drain-induced barrier lowering factor (DIBL),  $V_{th}$  is the thermal voltage, and n is a process-dependent constant. The thermal voltage at room temperature is around 28mV, which is far less than the supply voltage of interest in this project, therefore,  $e^{-V_{ds}/V_t} \approx 0$ . Because the transistor is at its static state when considering the static leakage power,  $V_{gs}$  and  $V_{ds}$  is roughly proportional to the supply voltage. As a result, the above equation can be reduced to

$$\hat{I}_{leak} \propto 10^{\frac{V_{dd}}{\hat{S}_{leak}}} \tag{2.5}$$

where  $\hat{S}_{leak}$  is the aggregate scaling coefficient derived from fittings to the simulated results.

#### 2.2.3.2 Performance

Lumos uses aggregate throughput under physical constraints as the primary performance metric. For the aggregate throughput performance  $(pf_s)$ , we model it with Amdahl's Law as shown in Equation 2.6

Speedup =

$$\frac{1}{\frac{1-\rho}{S_{\text{serial}}} + \frac{\rho}{n \cdot S_{\text{parallel}}}}$$

(2.6)

where  $\rho$  is the parallel ratio of the studied workload,  $S_{\text{serial}}$  is the serial part speedup over a baseline core,  $S_{\text{parallel}}$  is the per-core speedup when the system works in parallel mode, and n is the number of active cores running in parallel. For  $S_{\text{serial}}$ , only one core is active. In this case, the core is boosted to 1.3x nominal supply to achieve the best single core performance, denoted as  $\hat{pf}_c$ . When the system is in parallel mode, both n and  $S_{\text{parallel}}$  are determined by supply voltage. First, Lumos picks the optimal frequency with a given supply voltage; Second, it calculates percore power consumption including both the switching power and the leakage power according to the frequency and the supply. Finally, the number of active cores is the minimum restricted by the overall power and area budgets, which is given by

$$n(v) = \min(\frac{P}{p(v)}, \frac{A}{a}) \tag{2.7}$$

where p(v) is the per-core power as a function of supply voltage, P and A are system budgets of power and area, respectively. As a result, Equation 2.6 can be rewritten as

Speedup =

$$1 / \frac{1 - \rho}{\frac{\hat{pf_c}}{pf_0}} + \frac{\rho}{n(\nu) \cdot \frac{pf(\nu)}{pf_0}}$$

(2.8)

where  $pf_0$  is the performance of a single baseline core, pf(v) is the per-core performance as a function of supply voltage,

When considering process variation, performance loss of a single core leads to the poor throughput of a symmetric many-core system, in which the slowest core dictates the overall performance of the whole system. Adaptive Body Bias (ABB) is not considered here, but is important future work. However, the worst-case variation we used here sets an upper bound on the benefits of ABB. As a result, the parallel performance of a system is confined to the core with the worst performance, denoted as  $pf(v)_{min}$ . As for the power, we assume no fine-grained per-core level power management mechanisms; therefore, all cores contribute to the total power consumption through the whole period that the system is in parallel mode. We use the total mean power  $(\overline{p})$  to estimate the per-core

power, so Equation 2.7 is rewritten to

$$n(v) = \min(\frac{P}{\overline{p}}, \frac{A}{a}) \tag{2.9}$$

When considering process variations, the overall speedup in Equation 2.8 is rewritten to

Speedup =

$$1 / \frac{1 - \rho}{\frac{\hat{pf_c}}{pf_0}} + \frac{\rho}{n(\nu) \cdot \frac{pf(\nu)_{min}}{pf_0}}$$

(2.10)

#### 2.2.3.3 Un-core Components

Un-core components, such as network-on-chip (NoC) and memory controllers (MCs), have important implications on power and performance of a modern processor. Detailed models ( [40, 67]) are too fine-grained to achieve fast evaluation, and unsuitable for exploration tasks of large design space explorations that Lumos have been targeted. Alternatively, Lumos takes advantage of implicit approaches to model the power and performance impacts of un-core components. Lumos reserves 50% of both the total thermal design power (TDP) and the die area for un-core components. The performance impact on the multi-core scaling has been lumped into the  $\rho$  parameter in Equation 2.6.

#### **2.2.3.4** Baseline

A Niagara2-like in-order core is chosen as a single-core baseline design. The characteristics of this baseline core at 45nm are obtained from McPAT [48] and summarized in Table 2.3.

Table 2.3: Characteristics of a single Niagara2-like in-order core at 45nm, obtained from McPAT [48].

| Frequency | Dynamic   | Leakage   | Area     |

|-----------|-----------|-----------|----------|

| (GHz)     | Power (W) | Power (W) | $(mm^2)$ |

| 4.20      | 6.14      | 1.06      | 7.65     |

### 2.2.4 Accelerator Modeling

We model the speedup and the power consumption of RL and customized ASIC for a given kernel by u-core parameters  $(\eta,\phi)$ . "u-core" is a term proposed by Chung et. al. [16] to represent any single computational unit that is not a conventional CPU core. Examples of "u-core" include dedicated hardware accelerators and reconfigurable accelerators.  $\eta^1$  is the power relative to a single, basic in-order core, and  $\phi$  is the performance relative to the same baseline in-order core. We assume that u-cores are only used to accelerate kernels that are ideally parallelized. Therefore, we model the relative performance of a u-core proportional to its area:

$$Power_{ucore} = \eta \cdot \frac{A_{ucore}}{A_0}, \quad Perf_{ucore} = \phi \cdot \frac{A_{ucore}}{A_0}$$

where  $A_{ucore}$  is the area of a u-core, and  $A_0$  is the area of a single baseline in-order core.

### 2.2.5 Workload Modeling

Figure 2.2 illustrates the workload model, where a workload is composed of a pool of applications. Each single application is divided into two parts, serial and parallel. Part of an application can be also partitioned into several computing kernels. These kernels can be accelerated by various computing units, such as multi-core, possibly dim CPU cores, an RL accelerator, or a dedicated ASIC accelerator. We add two more parameters to model the relationship between applications and kernels:

**Presence** ( $\lambda$ ) A binary value to indicate whether or not a kernel present in an application.

**Coverage** (ε) The time consumption in percentage for a kernel when the whole application is running with a single base line core.

To model these two parameters, We have profiled the PARSEC benchmark suite [6] using Valgrind [59]. We use native input set for all applications except for x264, due to that Valgrind failed

<sup>&</sup>lt;sup>1</sup>In the original paper of [16],  $\mu$  is used to denote relative performance of u-cores. However,  $\mu$  is commonly used as the mean in statistics. Therefore, we use  $\eta$  as an alternative to avoid confusions.

to capture source annotations for x264. We extract top kernels for every single application. Their presence and coverage, which are plotted in Figure 2.3, show trends:

- Kernels, such as library calls, have a larger probability of presence, but lower coverage in a single application;

- Kernels, such as application-specific routines, have very limited presence, but higher coverage once they present;

- The majority of kernels are application-specific.

In addition to general-purpose benchmark suites like PARSEC, we have observed a similar trend on domain-specific benchmarks suite such as SD-VBS [83] and Minebench [57]. Based on these observations, we propose a statistical approach to model kernels' speedup  $(\eta)$ , presence  $(\lambda)$ ,

Figure 2.2: A workload is composed of applications. An application may have several computing kernels, which can be accelerated by many-core parallelization, RL, and ASIC.

Figure 2.3: Kernels coverage and presence. Kernels are extracted from PARSEC applications, excluding x264. The coverage percentages of *exp*, *fscanf*, *log*, and *rand* are averaged across their all occurrences. The coverage percentage of the "app specific" is the average of all application-specific kernels.

and coverage  $(\varepsilon)$ , which is shown in Equation 2.11.

$$\begin{cases} \eta \sim \mathcal{N}(\mu_s, \sigma_s^2) \\ \lambda = B(1, p) \quad \text{where } p = PDF(\eta) \\ \varepsilon \sim \mathcal{N}(\mu_c, \sigma_c^2) \end{cases}$$

(2.11)

Lumos samples the speedup  $(\eta)$  of kernels from a normal distribution. Speedup values of common kernels (e.g. library calls) are close to the mean of the distribution. On the other hand, speedup values of application-specific kernels are sampled from both tails of the distribution. The left tail represents kernels that are hard to accelerate, such as control-intensive ones. The right tail denotes kernels that are highly efficient on accelerators, such as compute-intensive streaming ones. Lumos samples the presence  $(\lambda)$  of these kernels from a Bernoulli distribution where the distribution parameter equals to  $PDF(\eta)$ . Lumos then samples the coverage  $(\epsilon)$  from an independent normal distribution. We justify coverage parameters using values extracted from PARSEC. We extract speedup values of RL accelerators by normalizing reported data from recent publications in the RL research community. Finally, we assume a fixed performance scaling ratio of 5x between an ASIC

accelerator and its counterpart RL implication. Table 2.4 summarizes values of all parameters used in Lumos's workload model.

Table 2.4: Summary of statistical parameters for kernel modeling

| $\mu_s$ RL | $\mu_s$ ASIC | $\sigma_s$ RL | $\sigma_s$ ASIC | $\mu_c$ | $\sigma_c$ |

|------------|--------------|---------------|-----------------|---------|------------|

| 40x        | 200x         | 10            | 50              | 40%     | 10%        |

Lumos exploits a priority-based approach to map kernels to accelerators and conventional cores. Dedicated ASIC accelerators are considered to have the highest priority and followed by reconfigurable accelerators. If neither types of accelerators are available, a kernel will be mapped to conventional CPU cores.

#### 2.2.6 System Configuration

Lumos models the basic system as a symmetric multi-core system composed of in-order cores. We assume the power and the area of the last-level cache (LLC) remains a constant ratio to the whole system. According to [48], we take the assumption that un-core components attribute to 50% of both the total thermal design power (TDP) and the die area. The bandwidth of the memory subsystem is assumed to be sufficient for future technology nodes by applying advanced techniques such as 3D-stacking, optical connections, multi-chip modules, etc. In the rest of this section, the power and the area of a system only refer to core components.

We have modeled three systems with different configurations of power and area by extracting data from commodity processors fabricated in 45nm. They include a small system representing desktop level processors [18], a medium system for normal server processors [19], and a large system that represents the most aggressive server throughput processors [20]. One more parameter is introduced as the power density of a system, reflecting the maximum power allowed for a unit area. It is calculated by dividing the area from the TDP. Table 2.5 summarizes detailed parameters of system configurations for Lumos.

Within an application, we assume that each kernel takes a considerable amount of computation

System Area **TDP** P. Density # of  $(mm^2)$  $(W/mm^2)^{\dagger}$ (W)Cores\* Type small 107 33 0.308 14 medium 130 65 0.5 17 large 200 120 0.6 26

Table 2.5: System configurations. All numbers are for core components, assumed to be 50% of the total TDP and the die area.