### Submillimeter-wave Schottky Diodes Integrated on Micromachined Silicon Probes

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science

University of Virginia

in partial fulfillment of the requirements for the degree

Doctor of Philosophy

by

Linli Xie

August 2019

$\bigodot$  2019 Linli Xie

### **APPROVAL SHEET**

This Dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

This Dissertation has been read and approved by the examining committee:

Advisor: Robert M. Weikle, II

Committee Member: Arthur W. Lichtenberger

Committee Member: N. Scott Barker

Committee Member: Andreas Beling

Committee Member: Steven M. Bowers

Committee Member: James M. Fitz-Gerald

Accepted for the School of Engineering and Applied Science:

CB

Craig H. Benson, School of Engineering and Applied Science

August 2019

### Abstract

The submillimeter-wave and terahertz region (300 GHz-3000 GHz) remains one of the the most scientifically useful yet least explored regions of the electromagnetic spectrum. This spectral range is critical for many applications such as remote sensing, radio astronomy, spectroscopy and imaging. However, the measurement infrastructure for developing submillimeter-wave and terahertz devices and materials is often ill-adapted for interfacing to devices for direct in-situ characterization, too large in size, cost-prohibitive, or non-existent. In addressing this issue, the focus of this work is the integration of GaAs Schottky diodes on micromachined on-wafer probes to provide compact, low cost and innovative metrology tools for the submillimeter-wave and terahertz scientific community.

The first part of the thesis focuses on developing a robust fabrication process of heterogeneous integration of Schottky diodes onto silicon substrates. The process aims to simplify the fabrication and improve the yield. The new approach eliminates most thermal processes, including ohmic contact thermal annealing and high-temperature wafer bonding of GaAs epitaxial transfer, that can lead to wafer fracture and delamination. A 160 GHz quadrupler is implemented using the new process to assess its potential.

The second part of the thesis investigates a new approach for on-wafer calibration at submillimeter wavelengths based on GaAs Schottky diodes integrated onto silicon as an electronic standard. Comparison of the error coefficients derived for both one-port and two-port calibration applications, derived using the diode standard are shown to be in good agreement with those obtained from a conventional set of offset short and TRL standards, respectively.

Finally, two implementations of integrating GaAs Schottky diodes onto micromachined

#### Abstract

on-wafer probes metrology are described. Probes incorporating diodes for temperature sensing and S-parameters measurement are detailed and designed. The design, fabrication process and measurement plans of these integrated probes are described.

### Acknowledgments

First of all, I would like to thank my advisor Professor Robert Weikle for continuously guiding, supporting, trusting and encouraging me during my PhD journey. I feel honored and privileged to have been his student and a member of the UVA FIR Lab. He encouraged freedom in doing research and studies, and provided numerous valuable insights and help along the way. His philosophy of teaching and mentoring young graduate students will continue to inspire me after I graduate.

I would like to extend my same appreciation to Professor Arthur Lichtenberger and Professor Scott Barker for their support and guidance. Through regular weekly research meetings over the years, they both have advised me a lot in research. I would also like to thank the members of my committee: Professor Andreas Beling, Professor Steven Bowers, and Professor James Fitz-Gerald for their valuable advice and feedback.

Additionally, I would like to express my gratitude to Dr. Matthew Bauwens and Dr. Michael Cyberey, who have always been available to offer help. I would like to thank my "cleanroom twin brother" Dr. Souheil Nadri for spending countless days and nights of developing diodes process with me, as well as other fellow graduate students in our research group: Christopher Moore, Noah Sauber, Masoud Jafari, Michael Eller, Yukang Feng, Dustin Widmann, Vinay Iyer, Hanyu Cao, Yuxin Wang, Scott Hinton, Hussain Humadi, Finbar Curtin and Austin Raymer. I would like to thank previous members of our research group: Dr. Naser Alijabbari, Dr. Sami Hawasli, Dr. Chunhu Zhang, Dr. Qiang Yu, Dr. Alex Arsenovic, Dr. Tannaz Farrahi, Gregory Stronko, Benjamin Gonzalez, Chenqian Gan, Dr. Becca Percy, Dr. Bob Benoit, Dr. Huilin Li, Dr. Therodore Reck, Dr. Haiyong Yu and Professor Lei Liu. My thanks also go to Joseph Beatrice, Alex Lobo, Michael Stogoski, Jianzhong Zhang and Jie Wang for their hard work in keeping the microfabrication cleanroom running. I would like to thank Dr. Bascom Deaver, Dr. Acar Isin, Dr. Jeffrey Hesler and Edward Douglas for their guidance and support. Many thanks to Qianhuan Yu, Dr. Ye Wang, Dr. Andrew Mercante, Dr. John Gaskins and Professor Brian Foley for the collaborations and discussions. I would like to thank Yadi Weaver, Beth Eastwood, Susan Malone and Dan Fekto for the help in administrative coordination.

Special thanks go to the IEEE Instrumentation and Measurement Society (IEEE I&M-S) for awarding me the 2017 I&M-S Graduate Fellowship and Student Travel Award, which partially funded me in completing the work presented in Chapter 5 of the dissertation.

Finally, I want to thank my parents for their support along the way of my life. I am also grateful for my friends for their company. I would like to express my love and appreciation to my wife for her understanding and care in everyday of my life over the years. This dissertation would have been impossible without her support.

## Contents

| $\mathbf{C}$ | onter          |                                                                           | $\mathbf{g}$ |

|--------------|----------------|---------------------------------------------------------------------------|--------------|

|              |                | of Tables                                                                 | j            |

|              | List           | of Figures                                                                | k            |

| 1            | Intr           | oduction                                                                  | 1            |

|              | 1.1            | Metrology for Submillimeter-wave Spectrum                                 | 1            |

|              | 1.2            | Micromachined On-Wafer Probes                                             | 4            |

|              | 1.3            | Heterogeneous Integration of GaAs Diodes onto Si Membranes                | 6            |

|              | 1.4            | Electronic Calibration at Submillimeter Wavelengths using Schottky Diodes |              |

|              |                | as On-Wafer Standards                                                     | 8            |

|              | 1.5            | On-Wafer Micromachined Probe with Submillimeter-wave Sensors              | 9            |

|              | 1.6            | Outline of Dissertation                                                   | 11           |

| <b>2</b>     | Epi            | taxy Transfer for Heterogeneous Integration of GaAs Schottky Diodes       |              |

|              | on S           | Silicon                                                                   | 12           |

|              | 2.1            | Introduction                                                              | 13           |

|              | 2.2            | Quasi-vertical Schottky Diode                                             | 15           |

|              |                | 2.2.1 Revised Fabrication Process                                         | 17           |

|              |                | 2.2.2 DC Measurement                                                      | 21           |

|              |                | 2.2.3 Submillimeter-wave Measurement                                      | 22           |

|              | 2.3            | Summary                                                                   | 24           |

| 3            | Free           | quency Quadruplers Based on Heterogeneous Integration of GaAs             |              |

|              | $\mathbf{Sch}$ | ottky Diodes with Silicon                                                 | <b>25</b>    |

|              | 3.1            | Introduction                                                              | 26           |

|              | 3.2            | Circuit Architecture and Design                                           | 26           |

|              | 3.3            | Fabrication Process                                                       | 29           |

|              | 3.4            | Measurements                                                              | 31           |

|              | 3.5            | Simulations and Design Improvements for Future Work                       | 33           |

|              | 3.6            | Summary                                                                   | 36           |

| 4            | Elec           | ctronic Calibration for Submillimeter On-Wafer Scattering Parameter       |              |

|              | Mea            | asurements                                                                | <b>37</b>    |

|              | 4.1            | Introduction                                                              | 38           |

|              | 4.2            | Electronic Calibration of One-Port Networks                               | 40           |

|              |                | 4.2.1 Schottky Diode Calibration Standard                                 | 40           |

|              |                | 4.2.2 Measurement                                                         | 42           |

|              | 4.3            | Electronic Calibration of Two-Port Networks                               | 48           |

|   |     | 4.3.1  | Diode Elctronic Calibration Standard 49                                                                                    |

|---|-----|--------|----------------------------------------------------------------------------------------------------------------------------|

|   |     | 4.3.2  | Error Model and Coefficients                                                                                               |

|   |     | 4.3.3  | Implementation of On-Wafer Electronic Calibration                                                                          |

|   |     | 4.3.4  | Application of On-Wafer Measurement Results of S-parameters 56                                                             |

|   | 4.4 | Conclu | sion $\ldots \ldots 59$                |

| 5 | Mic | romac  | hined Probes with Integrated GaAs Schottky Diodes for On-                                                                  |

| Ŭ |     |        | aperature Sensing 60                                                                                                       |

|   | 5.1 | Introd | $uction \dots \dots$ |

|   | 5.2 | Low-T  | emperature Diode Characterization                                                                                          |

|   |     | 5.2.1  | Liquid Nitrogen Cooling Measurement                                                                                        |

|   |     | 5.2.2  | Liquid Helium Cooling Measurement                                                                                          |

|   | 5.3 | Tempe  | erature Sensor Probe Design                                                                                                |

|   |     | 5.3.1  | Finite-Element Simulation                                                                                                  |

|   | 5.4 | Tempe  | erature Sensor Probe Fabrication                                                                                           |

|   | 5.5 | Proof- | of-Concept Temperature Sensor Probe Assembly and Measurement . 71                                                          |

|   | 5.6 |        | erature Sensor Probe Measurement Plans                                                                                     |

|   |     | 5.6.1  | Temperature Measurement    73                                                                                              |

|   |     | 5.6.2  | Mechanical Properties Characterization                                                                                     |

|   | 5.7 | Conclu | usions and Future Work                                                                                                     |

| ~ | а I | •11•   |                                                                                                                            |

| 6 |     |        | eter-Wave Six Port Reflectometer Integrated onto Microma-<br>-Wafer Probes 75                                              |

|   | 6.1 |        | uction                                                                                                                     |

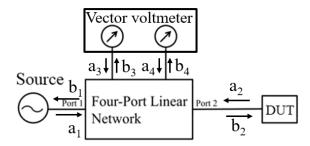

|   | 6.2 |        | rt Reflectometer Theory                                                                                                    |

|   | 0.2 | 6.2.1  | Four and Six-port Reflectometers                                                                                           |

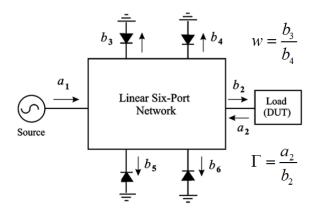

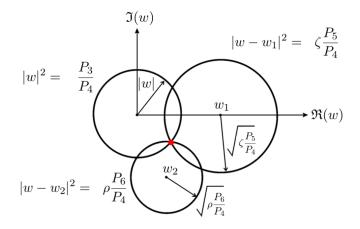

|   |     | 6.2.1  | General Six-port Measurements   78                                                                                         |

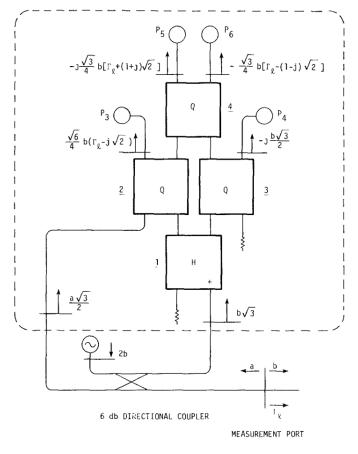

|   |     | 6.2.2  | Six-port Architectures                                                                                                     |

|   |     | 6.2.3  | Sampled Line Architecture                                                                                                  |

|   | 6.3 |        | ky Diode Detectors                                                                                                         |

|   | 0.0 | 6.3.1  | Responsivity and NEP   84                                                                                                  |

|   |     | 6.3.2  | Linearity and Dynamic Range                                                                                                |

|   |     | 6.3.3  | Square Law Detectors   86                                                                                                  |

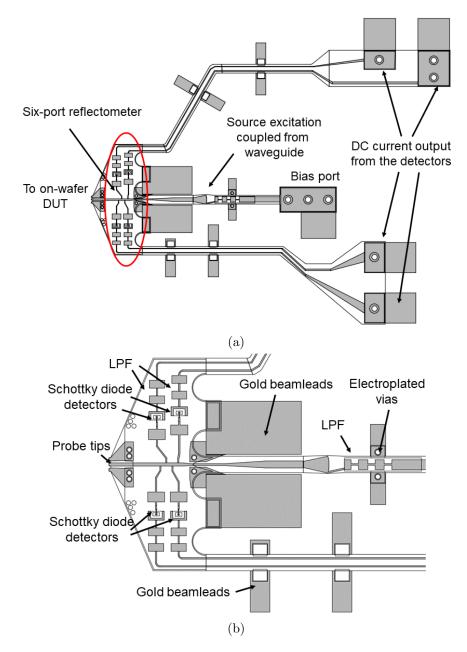

|   | 6.4 |        | ated Six Port Reflectometer On-Wafer Probe                                                                                 |

|   | 0.1 | 6.4.1  | Circuit Layout                                                                                                             |

|   |     | 6.4.2  | Circuit Design Simulations                                                                                                 |

|   |     | 6.4.3  | On-Wafer Probe without Integrated Six Port Reflectometer 91                                                                |

|   |     | 6.4.4  | Low Pass Filter at the Output                                                                                              |

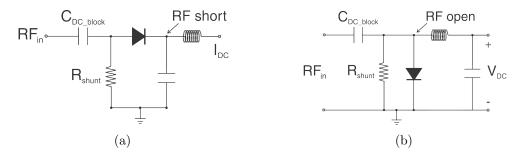

|   |     | 6.4.5  | Detector Circuits of the Six Port Reflectomter                                                                             |

|   |     | 6.4.6  | Six Port Reflectometer Integrated with On-Wafer Probes                                                                     |

|   |     | 6.4.7  | Mechanical Simulation                                                                                                      |

|   |     | 6.4.8  | Six Port Reflectometer Calibration Simulations                                                                             |

|   | 6.5 |        | rement Approach                                                                                                            |

|   | 0.0 | 6.5.1  | Calibration                                                                                                                |

|   |     | 6.5.2  | Preliminary RF Measurement                                                                                                 |

|   |     | 6.5.2  | Mechnical Measurements                                                                                                     |

|   |     | 6.5.4  | Advanced RF Measurement Plans                                                                                              |

|   | 6.6 |        | ation Process                                                                                                              |

|   | 0.0 |        |                                                                                                                            |

#### Contents

|              |       | 6.6.1   | Overview of the Process |     | <br>101 |

|--------------|-------|---------|-------------------------|-----|---------|

|              |       | 6.6.2   | Initial Progress        |     | <br>101 |

|              | 6.7   | Conclu  | usion                   | • • | <br>104 |

| 7            | Con   | clusior | ns and future work      |     | 105     |

|              | 7.1   | Conclu  | sions                   |     | <br>105 |

|              | 7.2   | Future  | work                    |     | <br>107 |

| Aŗ           | openo | dices   |                         |     | 113     |

| $\mathbf{A}$ | Dio   | des Fal | brication Recipe        |     | 114     |

| в            | Reci  | ipe of  | GaAs Bonding to Silicon |     | 126     |

| Bi           | bliog | raphy   |                         |     | 132     |

|              |       |         |                         |     |         |

# List of Tables

|     | Specific contact resistance of different ohmic contact metals and processes                         | 14 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.2 | Typical series resistance of Schottky diodes with 5.0-8.0 $\times 10^{-7} \ \Omega \ cm^2$ specific |    |

|     | contact resistance.                                                                                 | 18 |

| 2.3 | Extracted DC parameters and parameters normalized to anode area                                     | 22 |

| 5.1 | Extracted DC parameters and parameters normalized to anode area of the                              |    |

|     | temperature sensor probe                                                                            | 71 |

# List of Figures

| 1.1  | An integrated 340 GHz low noise amplifier chip mounted to a waveguide                                                                                            |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | housing for measurement and characterization [1]. The right image is a                                                                                           | 0   |

| 1.0  | close-up of the chip mounted to the housing. $\dots \dots \dots$ | 2   |

| 1.2  | (a) Image of a PNAX vector network analyzer with terahertz frequency                                                                                             |     |

|      | extension modules from Virginia Diodes (image courtesy of Agilent, Inc.). (b)                                                                                    | 2   |

| 1.3  | Image of a PM5 power meter (image courtesy of Virginia Diodes, Inc.) (a) On-wafer probes interfaced to VNA frequency extenders mounted to                        | 2   |

| 1.0  | large-area positioners (Cascade PA200 probe station [2]. (b) Image of an InP                                                                                     |     |

|      | amplifier, developed by Northrup Grumman, that is the first to produce gain                                                                                      |     |

|      | at frequencies exceeding 1 THz [3]                                                                                                                               | 3   |

| 1.4  | Photograph of (a) a cryogenic probe station with feedthroughs for on-wafer                                                                                       | 0   |

| 1.4  | probe measurements. (b) Probe feed-through assembly [4,5]                                                                                                        | 4   |

| 1.5  | Scanning electron micrograph (SEM) of a micromachined on-wafer probe for                                                                                         | т   |

| 1.0  | the WR-1.0 (750-1100 GHz) band on 15 $\mu$ m thick high-resistivity silicon [6].                                                                                 | 5   |

| 1.6  | A WR-1.5 micromachined probe mounted to its housing [7]                                                                                                          | 5   |

| 1.7  | A quasi-vertical GaAs Schottky diode fabricated on a high-resistivity ( $\rho > 10$                                                                              | 0   |

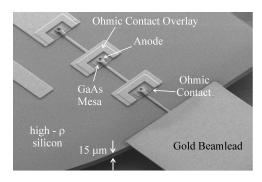

| 1.1  | $k\Omega$ -cm) silicon substrate [8]                                                                                                                             | 7   |

| 1.8  | Integrated quasi-vertical GaAs Schottky diodes fabricated on a thin $(15 \ \mu m)$                                                                               | •   |

| -    | silicon membrane with beamleads [9]                                                                                                                              | 7   |

| 1.9  | In-block view of the WR-1.5 integrated strain sensor probe chip [10]                                                                                             | 9   |

| 1.10 | Micromachined on-wafer probes with integrated baluns. (a) Full model of the                                                                                      |     |

|      | WR-10 balun probe in HFSS [11]. (b) Top side and bottom side geometry of                                                                                         |     |

|      | the WR-5.1 micromachined balun probe head. The probe design shown has a                                                                                          |     |

|      | ground-signal-ground-signal-ground tip configuration [12].                                                                                                       | 10  |

| 0.1  |                                                                                                                                                                  | 1 5 |

| 2.1  | Cross section view and equivalent circuit of a GaAs Schottky diode [13]                                                                                          | 15  |

| 2.2  | (a) Cartoon illustrating the quasi-vertical Schottky diode geometry. (b) Image                                                                                   |     |

|      | illustrating fracturing and delamination of GaAs epitaxy bonded to silicon                                                                                       | 15  |

| 0.9  | using Filmtronics FG-65 SOG.                                                                                                                                     | 15  |

| 2.3  | Quasi vertical diodes of under-annealed $Ge/Pd/Au/Ti$ ohmic contact. (a)                                                                                         |     |

|      | SEM of the diodes. (b) Measured current-voltage characteristic of a quasi-                                                                                       | 16  |

| 2.4  | vertical diode with 3 µm diameter anode                                                                                                                          | 10  |

| 2.4  | tion of Ti (20 nm)/Pd (40 nm)/Au (150 nm)/Ti (20 nm) ohmic contact over                                                                                          |     |

|      | the $In_{0.6}Ga_{0.4}As$ cap layer. (b) Bonding of the III-V epitaxy to high-resistivity                                                                         |     |

|      | silicon. (c) Removal of the GaAs handle and AlGaAs etch stop layers. (d)                                                                                         |     |

|      | Etching of the device mesa and formation of the Schottky anode contact.                                                                                          | 17  |

|      | Litering of the device mesa and formation of the benotity alloue contact.                                                                                        | т ( |

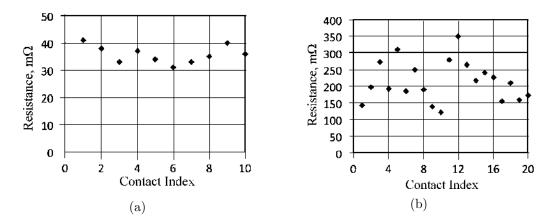

| 2.5  | Contact resistance measurement test of InGaAs/GaAs epi wafers. (a) Fab-                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ricated rectangular array of ohmic contacts. The TLM pattern width was                                                                         |    |

|      | $300 \ \mu m.$ (b) TLM pattern resistance as a function of contact spacing for the                                                             |    |

|      | Ti/Pd/Au non-alloyed ohmic contact to GaAs with InGaAs cap layers                                                                              | 19 |

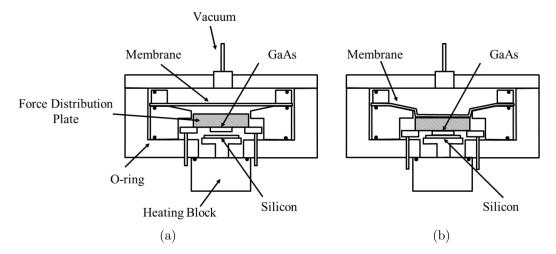

| 2.6  | (a) Cross section view of the membrane press before bonding GaAs to SOI,                                                                       |    |

|      | (b) view of the press during bonding [14]. The press is designed by Edward                                                                     |    |

|      | Douglas.                                                                                                                                       | 20 |

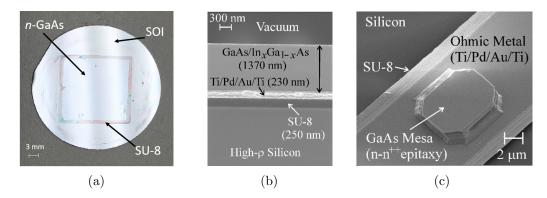

| 2.7  | (a) Image of the bonded GaAs epitaxy onto a silicon-on-insulator (SOI) wafer.                                                                  |    |

|      | (b) Scanning electron micrograph (SEM) of a cross-section of the bonded                                                                        |    |

|      | GaAs epitaxy, ohmic metal, SU-8 resist, and silicon substrate. (c) SEM                                                                         |    |

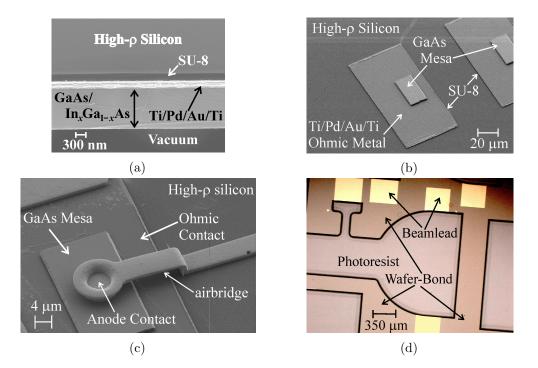

|      | showing the GaAs mesa and ohmic metal contact bonded to silicon                                                                                | 20 |

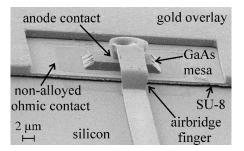

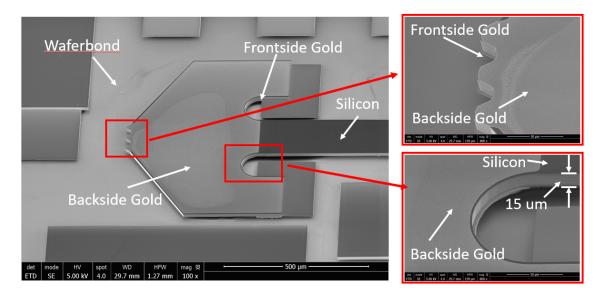

| 2.8  | SEM of the quasi-vertical diode profile (diameter $=3 \ \mu m$ ) showing the device                                                            |    |

|      | mesa, underlying ohmic contact, and anode contact airbridge. A CPW feed                                                                        |    |

|      | to the diode permits on-wafer S-parameter characterization of the device.                                                                      | 21 |

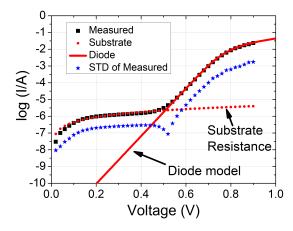

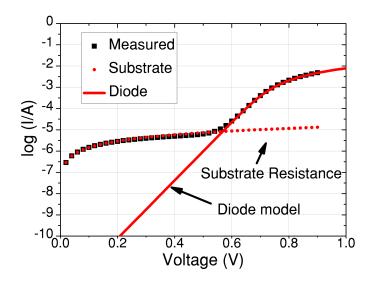

| 2.9  | Measured average current-voltage characteristic of eight quasi-vertical diodes                                                                 |    |

|      | with 3 $\mu$ m diameter anode with non-alloyed ohmic contact. The standard                                                                     |    |

|      | deviation (STD) of current-voltage measurements of eight diodes with the                                                                       |    |

|      | same anode size is also plotted.                                                                                                               | 22 |

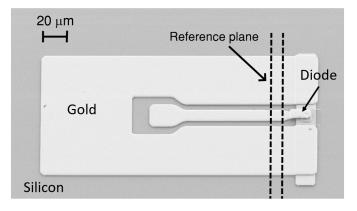

| 2.10 | Reference plane of the on-wafer S-parameter measurement of the Schottky                                                                        |    |

|      | diodes                                                                                                                                         | 22 |

| 2.11 | WR-2.2 on wafer measurement results. (a) $S_{11}$ vs voltage at 425 GHz. (b)                                                                   |    |

|      | Equivalent circuit model used to represent the non-alloyed ohmic contact                                                                       |    |

|      | diode. (c) Extracted junction capacitance. (d) Extracted series resistance                                                                     | 23 |

| 0.1  |                                                                                                                                                |    |

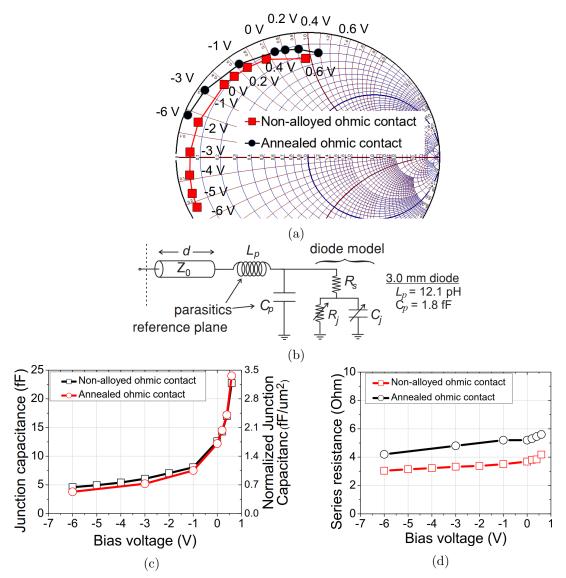

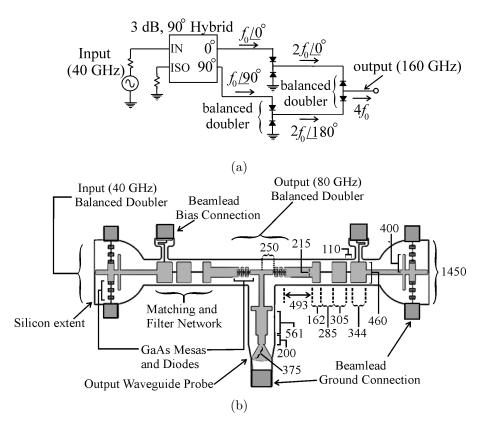

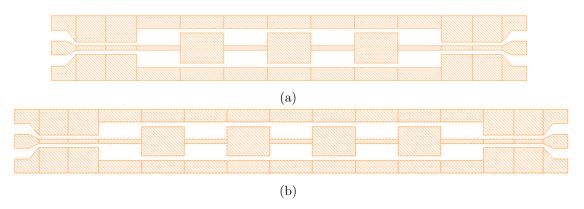

| 3.1  | (a) Quadrupler circuit architecture and (b) layout of the integrated quadrupler                                                                |    |

|      | chip. The quadrature hybrid is implemented off-chip (in waveguide) and all dimensions noted are in um                                          | 27 |

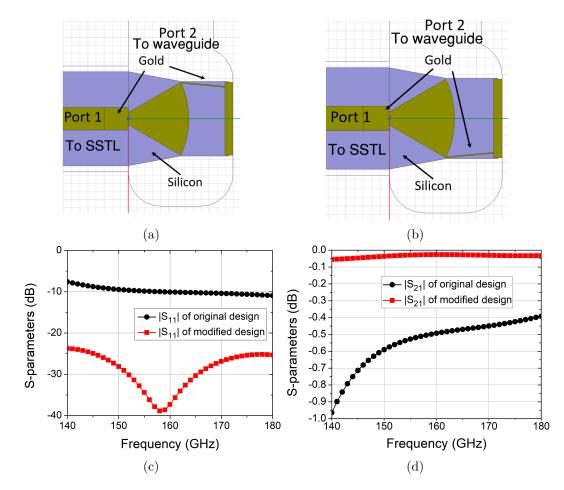

| 3.2  | dimensions noted are in µm                                                                                                                     | 21 |

| 3.2  | quadrupler circuit of SSTL-waveguide transition. (b) Modified<br>quadrupler circuit of SSTL-waveguide transition. (c) Comparison of simulation |    |

|      | results of return loss of the original and modified SSTL-waveguide transition.                                                                 |    |

|      | (d) Comparison of simulation results of insertion loss of the original and                                                                     |    |

|      | modified SSTL-waveguide transition.                                                                                                            | 28 |

| 3.3  | Images illustrating steps of the fabrication process. (a) SEM image of the                                                                     | 20 |

| 0.0  | bonded epitaxy. (b) Formation of the GaAs mesas and ohmic metal pedestals,                                                                     |    |

|      | (c) Anode and airbridge structures. (d) Backside lithography used to define                                                                    |    |

|      | the chip geometry.                                                                                                                             | 29 |

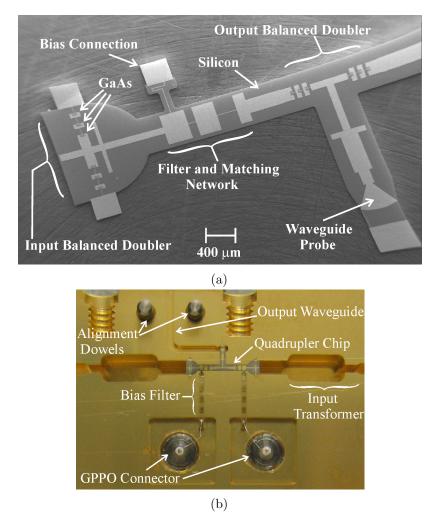

| 3.4  | (a) SEM image of the completed quadrupler chip. (b) The quadrupler chip                                                                        |    |

|      | mounted to its waveguide housing. The quadrature hybrid is not shown                                                                           | 30 |

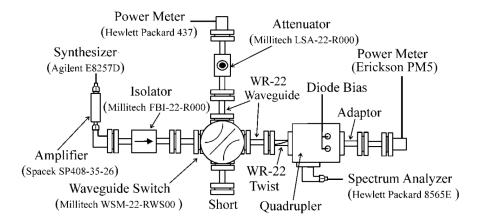

| 3.5  | Diagram of the quadrupler measurement setup.                                                                                                   | 31 |

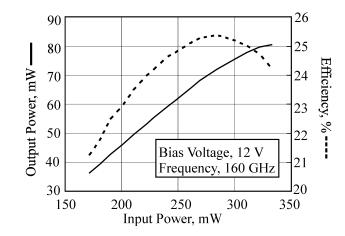

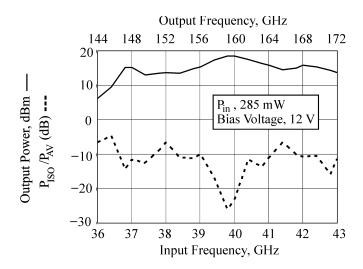

| 3.6  | Quadrupler output power and efficiency vs. input power                                                                                         | 32 |

| 3.7  | Output power and power measured at the isolation port, normalized to                                                                           |    |

|      | available power. vs. frequency.                                                                                                                | 32 |

| 3.8  | Power output vs frequency for different input power levels                                                                                     | 32 |

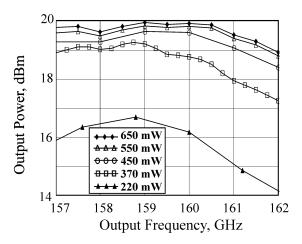

| 3.9  | Possible positions to add extra beamlead to improve thermal handling of the                                                                    |    |

|      | quadrupler without interfering the electronic performance                                                                                      | 33 |

|      |                                                                                                                                                |    |

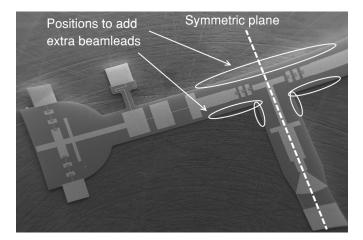

| 3.10 | Three options of extra beamlead added to the second stage of the quadrupler           |    |

|------|---------------------------------------------------------------------------------------|----|

|      | for enhanced thermal handling. (a) Option 1: two separate pieces of extra             |    |

|      | beamlead added to the long side. (b) Option 2: one continuous piece of extra          |    |

|      | beamlead added to the long side. (c) Option 3: one continuous piece of extra          |    |

|      | beamlead added to the long side and two more pieces of extra beamlead added           |    |

|      | close to the output RF channel side                                                   | 34 |

| 3.11 | Increase the clearance between the edge of ohmic contact and anchor of the            |    |

|      | finger air bridge to increase the fabrication yield                                   | 34 |

| 3.12 | Add the beamlead to enhance thermal handling of the quadrupler and increase           |    |

|      | the clearance between the edge of ohmic contact and anchor of the finger air          |    |

|      | bridge to increase the fabrication yield                                              | 34 |

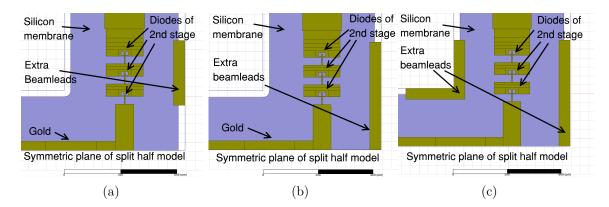

| 3.13 | Comparison of steady state simulation of the quasi-half split model of quadru-        |    |

|      | pler chip with or without additional beamleads at the second stage and                |    |

|      | increased air bridge anchor clearance to the ohmic contact pad. (a) 280 mW            |    |

|      | input power, original design. (b) 280 mW input power, modified design shown           |    |

|      | in Figure 3.12. (c) 600 mW input power, original design. (b) 600 mW input             |    |

|      | power, modified design shown in Figure 3.12. Appoximate temperature of                |    |

|      | anodes in both first stage and second stage of the quadrupler chip are labled.        | 35 |

| 3.14 | Comparison of simulation of impedance matching of the modified design to the          |    |

|      | original design. (a) Output matching of the first stage. (b) Input matching of        |    |

|      | the second stage. (c) Output matching of the second stage                             | 36 |

|      |                                                                                       |    |

| 4.1  | Repeated four-point resistance measurements of a nickel-tip micromachined             |    |

|      | probe contacting (a) gold, and (b) aluminum pads [2]                                  | 39 |

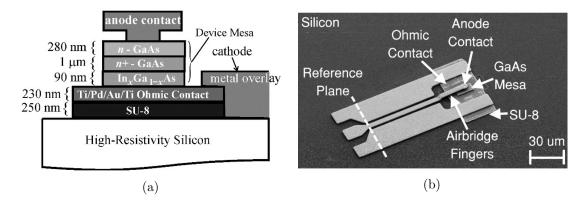

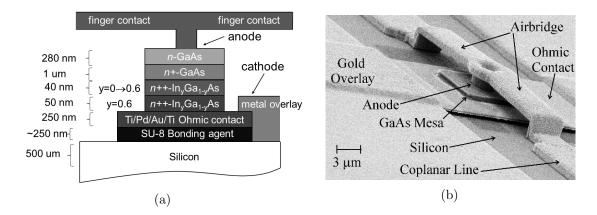

| 4.2  | (a) Geometry of the quasi-vertical Schottky diode showing the epitaxial layers.       |    |

|      | (b) Scanning electron micrograph of a coplanar-fed quasi-vertical diode used          |    |

|      | as an electronic standard.                                                            | 41 |

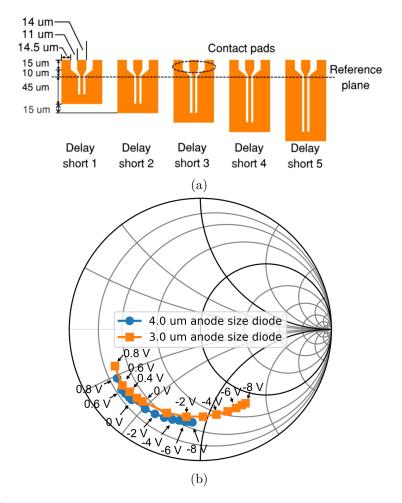

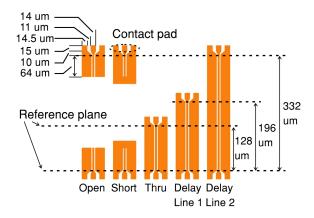

| 4.3  | (a) Coplanar offset short circuits used as calibration standards. (b) Measured        |    |

|      | $S_{11}$ of CPW-fed Schottky diodes with different diameters (4.0 $\mu$ m and 3.0     |    |

|      | $\mu m)$ as a function of bias at 425 GHz. The voltage is swept from -8 V to 0.8      |    |

|      | V for each diode.                                                                     | 43 |

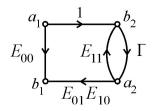

| 4.4  | Signal flow graph of the one-port error model. $\Gamma$ represents the "true" reflec- |    |

|      | tion coefficient of the device-under-test.                                            | 44 |

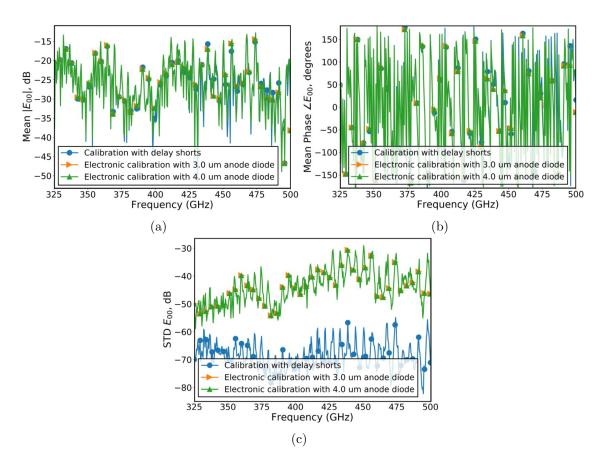

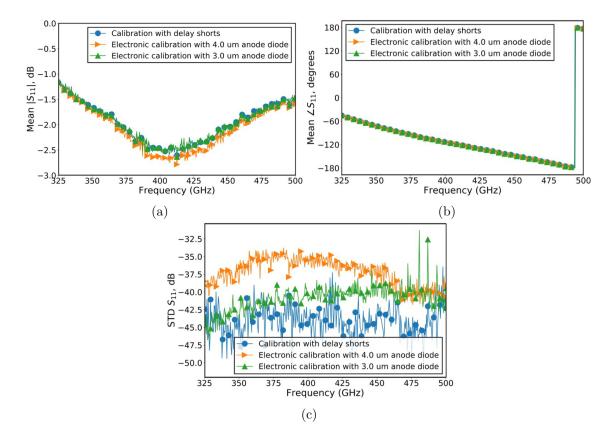

| 4.5  | (a) Magnitude, (b) phase and (c) standard deviation of the directivity error          |    |

|      | coefficient $(E_{00})$ extracted from three sets of calibration standards             | 45 |

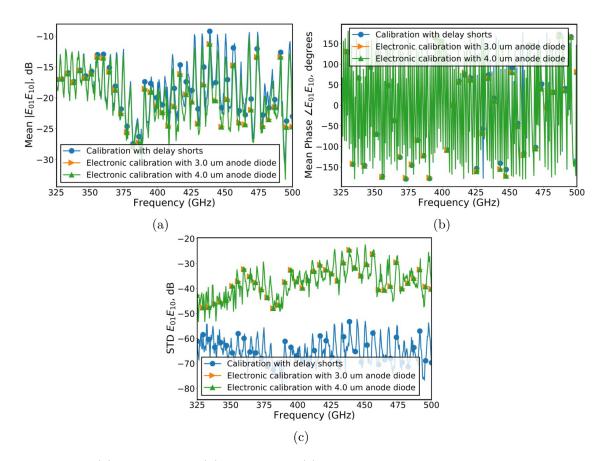

| 4.6  | (a) Magnitude, (b) phase and (c) standard deviation of the tracking error             |    |

|      | coefficient $(E_{01}E_{10})$ extracted from three sets of calibration standards       | 46 |

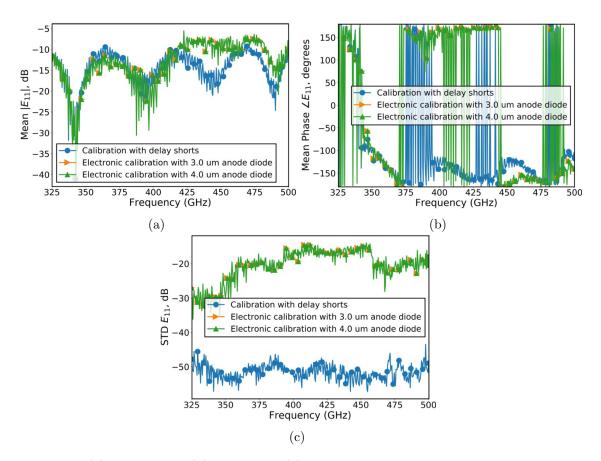

| 4.7  | (a) Magnitude, (b) phase and (c) standard deviation of the port match error           |    |

|      | coefficient $(E_{11})$ extracted from three sets of calibration standards             | 47 |

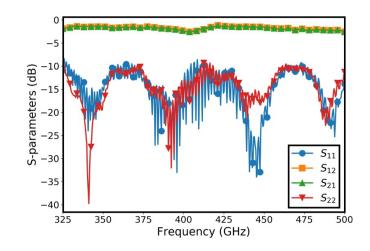

| 4.8  | Measured scattering parameters (magnitude) of the micromachined WR-2.2                |    |

|      | wafer probe                                                                           | 47 |

| 4.9  | Comparison of measurements over the WR-2.2 band of a 5.6 $\mu$ m diameter diode       |    |

|      | biased at -4 Volts, corrected using delayed shorts and electronic calibration         |    |

|      | standards. (a) Mean value of magnitude in dB (b) mean phase in degrees,               |    |

|      | and (c) standard deviation expressed in dB                                            | 48 |

| 4.10 | (a) Cartoon showing the diode geometry and epitaxial layers. (b) Scanning             |    |

|      | electron micrograph of a dual-finger quasi-vertical GaAs Schottky diode               |    |

|      | shunting a coplanar transmission line.                                                | 49 |

| 4.11 | SEM images of two-port fed diode (anode diameter=4 $\mu$ m) for two port                                    |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | electronic calibration of S-parameter measurement.                                                          | 49 |

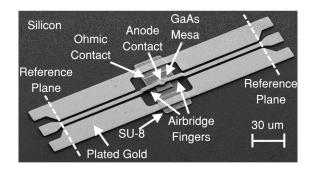

| 4.12 | TRL calibration kit used for regular two port calibration of S-parameters                                   |    |

|      | measurement. The calibration standards are fabricated on the same wafer as                                  |    |

|      | the two port diodes and DUTs.                                                                               | 50 |

| 4.13 | Measured S-parameters across the WR-2.2 band of the TRL standards used                                      |    |

|      | for regular two port calibration: (a) $S_{11}$ (b) $S_{21}$                                                 | 51 |

| 4.14 | Measured S-parameters of the 2 port electronic calibration standard diodes                                  |    |

|      | at 425 GHz. The bias voltage is swept from -8 V to 0.8 V                                                    | 52 |

| 4.15 | Eight term model of two port calibration of S-parameters measurement. The                                   |    |

|      | switch terms $\Gamma_{\rm F}$ and $\Gamma_{\rm R}$ are included too.                                        | 53 |

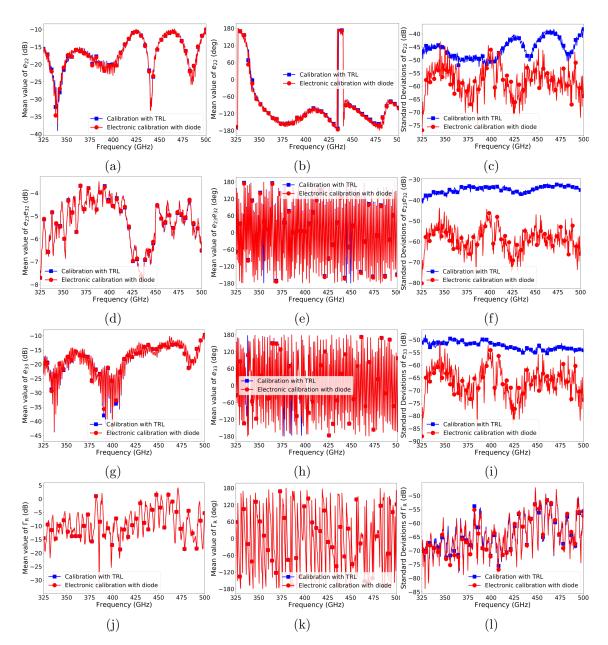

| 4.16 | Comparison of forward model error terms: $e_{00}$ , $e_{01}e_{10}$ , $e_{11}$ and $\Gamma_{\rm F}$ of error |    |

|      | network from WR-2.2 two port electronic calibration results and TRL calibra-                                |    |

|      | tion. (a) Magnitude of mean value of $e_{00}$ in dB. (b) Phase of mean value of                             |    |

|      | $e_{00}$ in degrees. (c) Complex standard deviation of $e_{00}$ in dB. (d) Magnitude                        |    |

|      | of mean value of $e_{01}e_{10}$ in dB. (e) Phase of mean value of $e_{01}e_{10}$ in degrees.                |    |

|      | (f) Complex standard deviation of $e_{01}e_{10}$ in dB. (g) Magnitude of mean value                         |    |

|      | of $e_{11}$ in dB. (h) Phase of mean value of $e_{11}$ in degrees. (i) complex standard                     |    |

|      | deviation of $e_{11}$ in dB. (j) Magnitude of mean value of $\Gamma_{\rm F}$ in dB. (k) Phase of            |    |

|      | mean value of $\Gamma_{\rm F}$ in degrees. (l) Complex standard deviation of $\Gamma_{\rm F}$ in dB.        | 54 |

| 4.17 | Comparison of reverse model error terms: $e_{22}$ , $e_{23}e_{32}$ , $e_{33}$ and $\Gamma_{\rm R}$ of error |    |

|      | network from WR-2.2 two port electronic calibration results and TRL calibra-                                |    |

|      | tion. (a) Magnitude of mean value of $e_{22}$ in dB. (b) Phase of mean value of                             |    |

|      | $e_{22}$ in degrees. (c) Complex standard deviation of $e_{22}$ in dB. (d) Magnitude                        |    |

|      | of mean value of $e_{23}e_{32}$ in dB. (e) Phase of mean value of $e_{23}e_{32}$ in degrees.                |    |

|      | (f) Complex standard deviation of $e_{23}e_{32}$ in dB. (g) Magnitude of mean value                         |    |

|      | of $e_{33}$ in dB. (h) Phase of mean value of $e_{33}$ in degrees. (i) Complex standard                     |    |

|      | deviation of $e_{33}$ in dB. (j) Magnitude of mean value of $\Gamma_{\rm R}$ in dB. (k) Phase               |    |

|      | of mean value of $\Gamma_{\rm R}$ in degrees. (1) Complex standard deviation of $\Gamma_{\rm R}$ in dB.     | 55 |

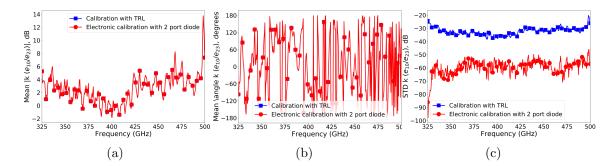

| 4.18 | Comparison of $k$ $(e_{10}/e_{23})$ error terms from WR-2.2 two port electronic                             |    |

|      | calibration results and TRL calibration. (a) Magnitude of mean value of $k$ in                              |    |

|      | dB. (b) Phase of mean value of $k$ in degrees. (c) Complex standard deviation                               |    |

|      | of $k$ in dB                                                                                                | 56 |

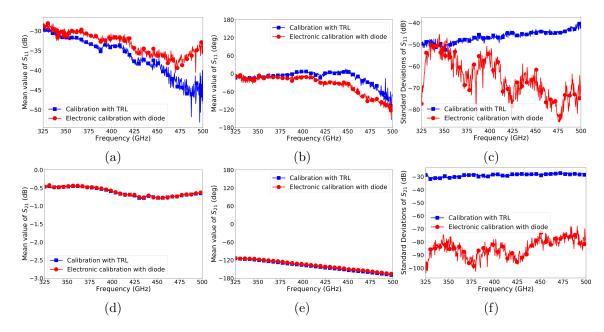

| 4.19 | Comparison of WR-2.2 two port electronic calibration results and TRL cal-                                   |    |

|      | ibration results to a Thru. (a) Magnitude of mean value of $S_{11}$ in dB. (b)                              |    |

|      | Phase of mean value of $S_{11}$ in degrees. (c) Complex standard deviation of $S_{11}$                      |    |

|      | in dB. (d) Magnitude of mean value of $S_{21}$ in dB. (e) Phase of mean value of                            |    |

|      | $S_{21}$ in degrees. (f) Complex standard deviation of $S_{21}$ in dB                                       | 57 |

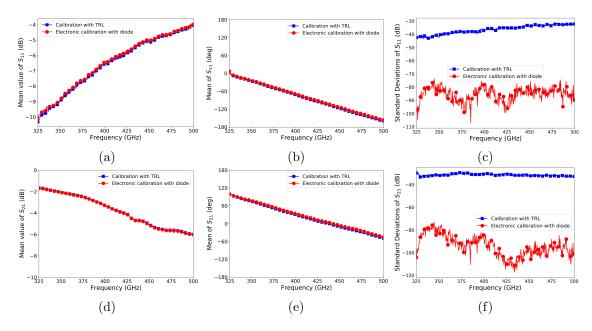

| 4.20 | Comparison of WR-2.2 two port electronic calibration results and TRL cal-                                   |    |

|      | ibration results to a two port diode structure with 4.0 um anode size. (a)                                  |    |

|      | Magnitude of mean value of $S_{11}$ in dB. (b) Phase of mean value of $S_{11}$ in                           |    |

|      | degrees. (c) Complex standard deviation of $S_{11}$ in dB. (d) Magnitude of mean                            |    |

|      | value of $S_{21}$ in dB. (e) Phase of mean value of $S_{21}$ in degrees. (f) Complex                        |    |

|      | standard deviation of $S_{21}$ in dB                                                                        | 58 |

| 5.1  | Configuration of the Lakoshore TTP 6 amogenic probe station for an under                                    |    |

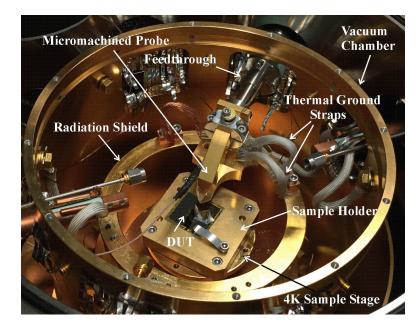

| 0.1  | Configuration of the Lakeshore TTP-6 cryogenic probe station for on-wafer measurements.                     | 62 |

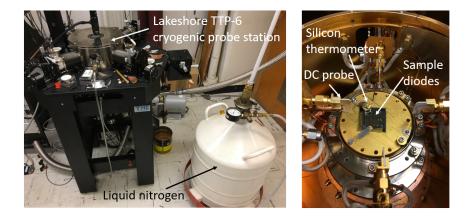

|      |                                                                                                             | 04 |

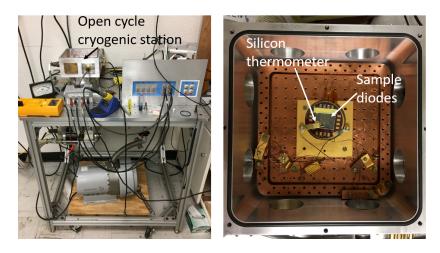

| 5.2                                       | Image of the measurement setup for cryogenic characterization of a quasi-<br>vertical diode by liquid nitrogen cooling                                        | 63       |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

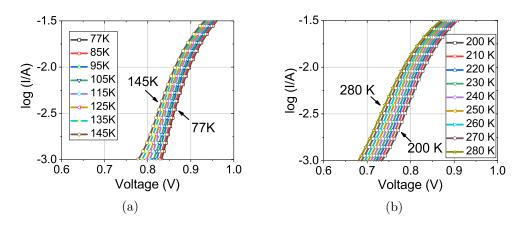

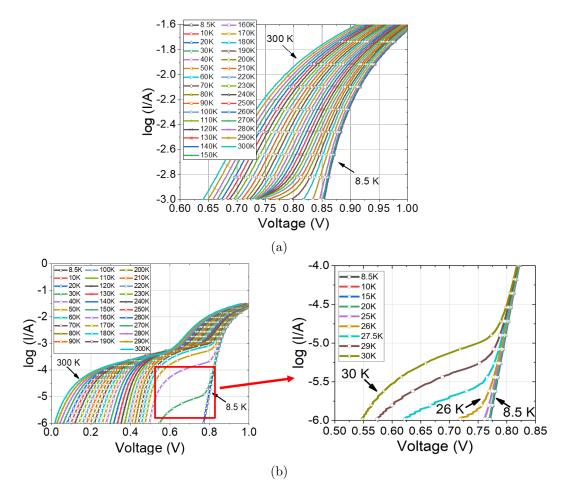

| 5.3                                       | Measured forward voltage-current characteristic of two diodes in two temper-                                                                                  |          |

| - 1                                       | ature ranges.                                                                                                                                                 | 63       |

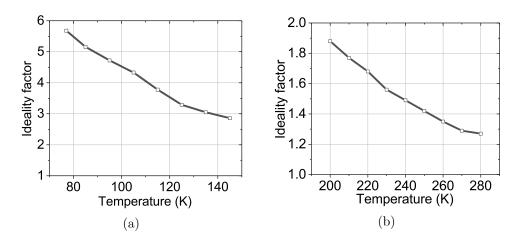

| 5.4                                       | Extracted idealty factor of two diodes at 1mA bias current in two temperature ranges.                                                                         | 64       |

| 5.5                                       | Measured sensitivity at different bias current of two diodes in two temperature                                                                               | 01       |

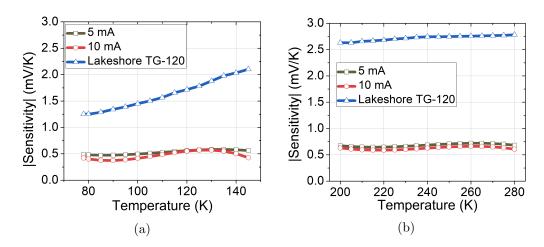

|                                           | ranges compared to GaAlAs diodes from Lakeshore Inc. [15]                                                                                                     | 64       |

| 5.6                                       | Image of the measurement setup for cryogenic characterization of a quasi-                                                                                     | ~        |

| 5.7                                       | vertical diode by liquid nitrogen cooling                                                                                                                     | 65       |

| 5.1                                       | down in liquid helium. (a) Forward region only (b) Full bias span and zoom                                                                                    |          |

|                                           | in view of the region where carriers freeze out.                                                                                                              | 66       |

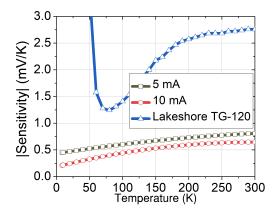

| 5.8                                       | Measured sensitivity at different bias current of one proof-of-concept diode                                                                                  |          |

|                                           | cooled down in liquid helium compared to GaAlAs diodes from Lakeshore                                                                                         | 66       |

| 5.9                                       | Inc. [15]                                                                                                                                                     | 00       |

|                                           | used in on-wafer S-parameters measurement in cryogenic temperatures up to                                                                                     |          |

|                                           | 77K [4]. (b) Bottom: proposed temperature sensor probes with integrated                                                                                       |          |

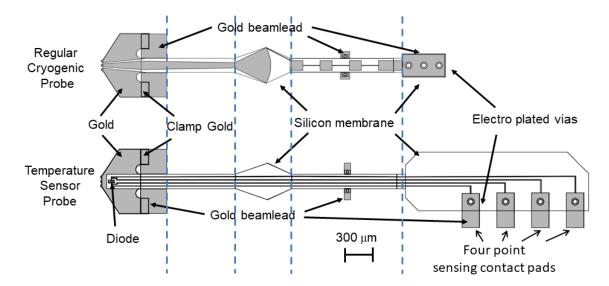

| F 10                                      | GaAs Schottky diodes                                                                                                                                          | 67       |

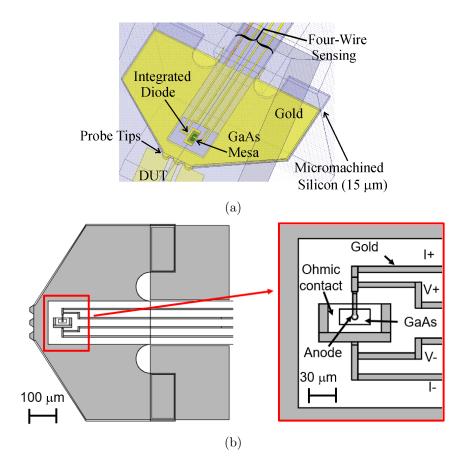

| 5.10                                      | sensor. (a) Electromagnetic simulation model showing details of the probe                                                                                     |          |

|                                           | tip, and (b) Zoom in view of the probe tip area                                                                                                               | 68       |

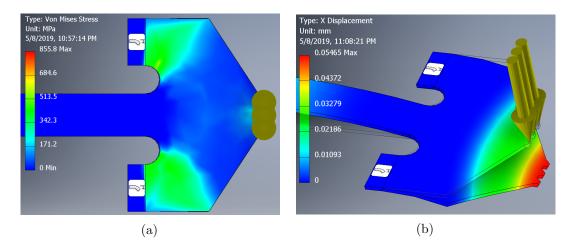

| 5.11                                      | Mechanical simulation of the temperature-sensor probe induced in the chip                                                                                     |          |

| 5 10                                      | when subject to a 10 mN/tip load: (a) stress (b) displacement. $\ldots$                                                                                       | 69<br>70 |

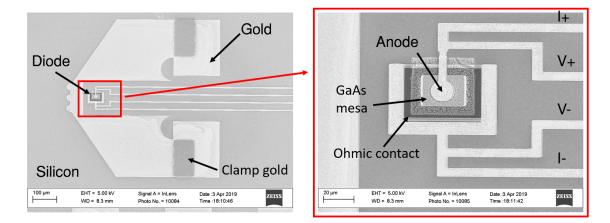

|                                           | SEM of the tip area of temperature sensor probe: front side                                                                                                   | 70<br>70 |

|                                           | Measured room temperature current-voltage characteristic of a quasi-vertical                                                                                  | 10       |

|                                           | Schottky diode integrated on high-resistivity silicon                                                                                                         | 71       |

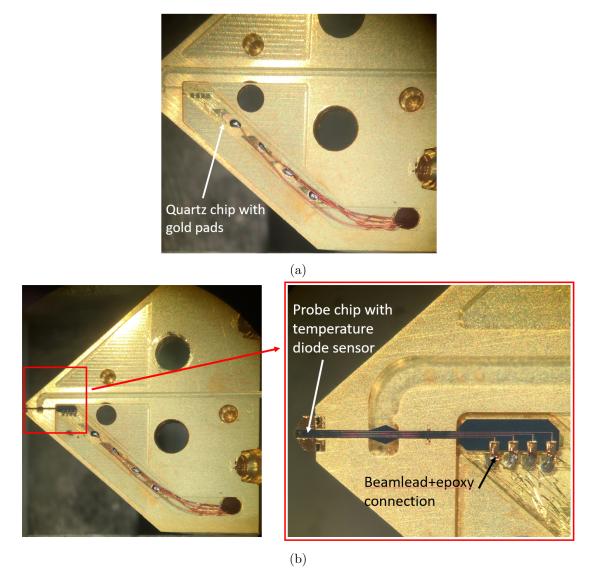

| 5.15                                      | Assembling of the probe thermometer into the waveguide housing. (a) Mount-                                                                                    |          |

|                                           | ing quartz chip into the recess and solder wires onto the gold pads (b) Tacking<br>down the probe chip with integrated diode temperature sensor and strength- |          |

|                                           | ened the connection with epoxy                                                                                                                                | 72       |

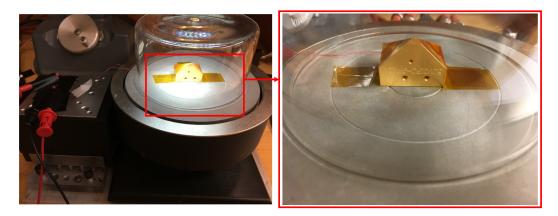

| 5.16                                      | Measurement setup of the prototype characterization of the temperature                                                                                        |          |

|                                           | sensor probe.                                                                                                                                                 | 73       |

| 6.1                                       | Basic structure of a four-port reflectometer.                                                                                                                 | 77       |

| 6.2                                       | Basic structure of a six-port reflectometer                                                                                                                   | 78       |

| 6.3                                       | The complex value of $w$ is determined by the intersection of these three circles.                                                                            | 80       |

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Engen's six port architecture based on hybrid couplers [16]                                                                                                   | 82<br>82 |

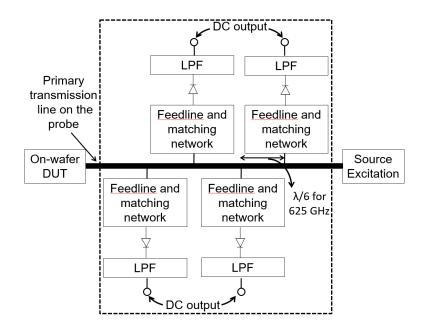

| 6.6                                       | Six port circuit sampled line structure                                                                                                                       | 83       |

| 6.7                                       | Mapping from the $\Gamma$ plane to the <i>w</i> plane                                                                                                         | 83       |

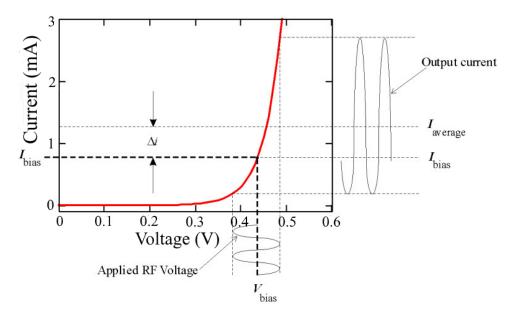

| 6.8                                       | IV characteristic of a detector diode.                                                                                                                        | 85       |

| 6.9                                       | An RF voltage applied to a biased diode generates a DC response as well as higher harmonics, resulting in an offset current $\Delta I$                        | 96       |

| 6.10                                      |                                                                                                                                                               | 86       |

|                                           | on-wafer probe.                                                                                                                                               | 88       |

| 6.11 | Circuit layout of the proposed six port reflectometer integrated onto the                |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | on-wafer probe. (a) Full chip. (b) Zoom in view of the probe tip area                    | 89  |

| 6.12 | Two types of detector circuits. (a) Current detection. (b) Voltage detection.            | 90  |

| 6.13 | Option 1 of the micromachined on-wafer probe to be integrated with six port              |     |

|      | reflectometer: tighter lithography alignment tolerance with wider bandwidth.             |     |

|      | (a) HFSS model of probe tip area. (b) Zoom in view of the MSL to SSTL                    |     |

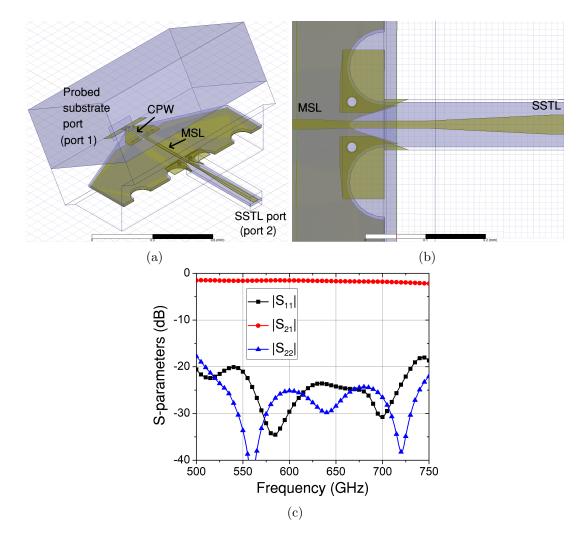

|      | transition. (c) Simulation results of the S-parameters.                                  | 91  |

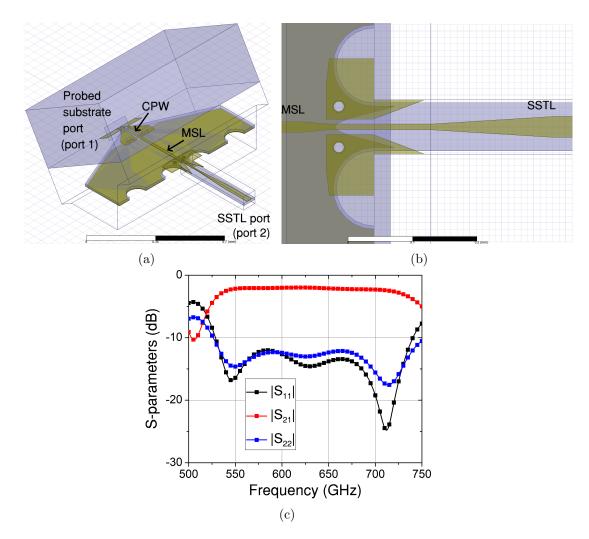

| 6.14 | Option 2 of the micromachined on-wafer probe to be integrated with six                   |     |

|      | port reflectometer: looser lithography alignment tolerance with narrower                 |     |

|      | bandwidth. (a) HFSS model of probe tip area. (b) Zoom in view of the MSL                 |     |

|      | to SSTL transition. (c) Simulation results of the S-parameters.                          | 92  |

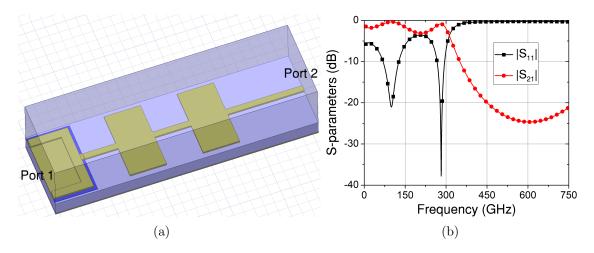

| 6 15 | Low pass filter used in the six port reflectometer probe. (a) HFSS model. (b)            | 04  |

| 0.10 | Simulation results of the S-parameters                                                   | 93  |

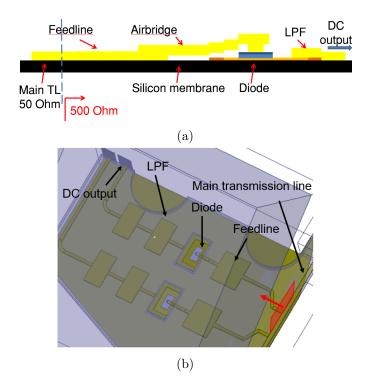

| 6 16 | *                                                                                        | 95  |

| 0.10 | (a) Cross section view of reference plane of embedded impedance of detector              |     |

|      | circuit to the original main transmission line. (b) Reference plane of two               | 0.4 |

| 0.15 | detector circuits on the same side of the main transmission line                         | 94  |

| 0.17 | (a) Single branch of the six port reflectometer of the full circuit model in             |     |

|      | HFSS. (b) Simulation results of the reflection seen from the sampling point              |     |

|      | of the single branch to the main transmission line                                       | 94  |

|      | Probe tip area part of the full circuit model in HFSS                                    | 95  |

| 6.19 | Simulation results of option 1 of the full model: (a) ADS simulation results             |     |

|      | of return loss and insertion loss of the full model with integrated six port             |     |

|      | reflectometers and (b) ADS simulation results of coupling to the diodes of the           |     |

|      | full model with integrated six port reflectometers for layout option 1. Port 1           |     |

|      | and 2 are SSTL port and CPW port respectively. Port 3-6 are diode ports.                 | 95  |

| 6.20 | Simulation results of option 2 of the full model: (a) ADS simulation results             |     |

|      | of return loss and insertion loss of the full model with integrated six port             |     |

|      | reflectometers and (b) ADS simulation results of coupling to the diodes of the           |     |

|      | full model with integrated six port reflectometers for layout option 2. Port 1           |     |

|      | and 2 are SSTL port and CPW port respectively. Port 3-6 are diode ports.                 | 96  |

| 6.21 | (a) Simulated displacement of the tips and (b) Simulated strain distribution             |     |

|      | profile of the power meter integrated onto WR-1.5 micromachined on-wafer                 |     |

|      | probe. Each tip is applied to 10 mN contact force.                                       | 97  |

| 6.22 | Simulated average magnitude and phase measurement errors at 625 GHz.                     | 97  |

|      | Offset coplanar short and open circuits for the six port reflectometer calibration       |     |

| 0.20 | of ellipse fitting.                                                                      | 98  |

| 6.24 | Coplanar offset short for the VNA calibration. Another set of calibration                | 00  |

| 0.21 | standards are incorporated in a back-to-back configuration to save wafer space.          | 99  |

| 6 25 | Mismatched load DUTs: (a) 65 $\Omega$ coplanar open circuit load. (a) 65 $\Omega$        | 00  |

| 0.20 | coplanar short circuit load. (a) 80 $\Omega$ coplanar open circuit load. (d) 80 $\Omega$ |     |

|      |                                                                                          | 100 |

| ເລ   | Low pass filter DUTs for two port calibration evaluation: (a) Stepped                    | 100 |

| 0.20 |                                                                                          | 101 |

| 0.07 |                                                                                          | 101 |

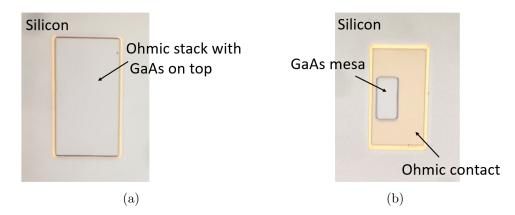

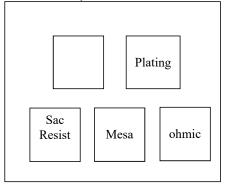

| 0.27 | (a) Ohmic contact stack with unetched GaAs on top. (b) GaAs mesa formed                  | 101 |

| 0.00 | *                                                                                        | 101 |

|      |                                                                                          | 102 |

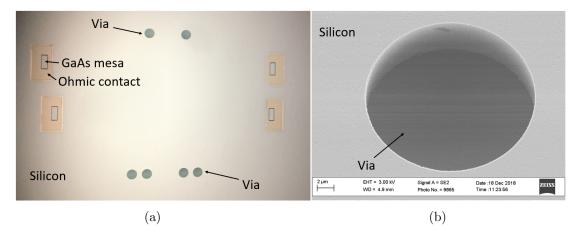

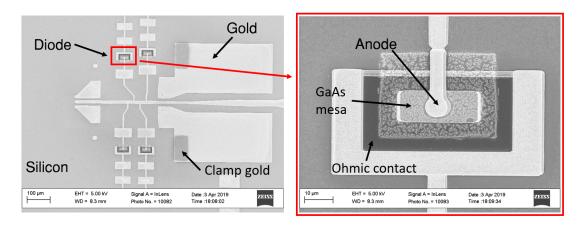

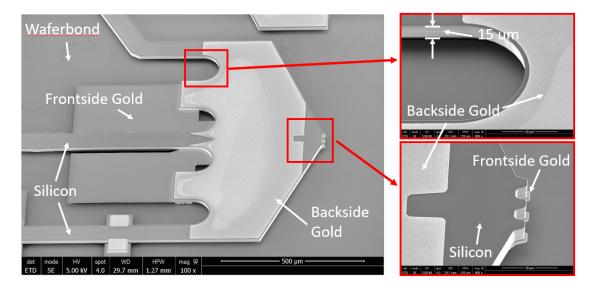

| 6.29 | SEM of the front side of the six port reflectometer probe before bonding for             |     |

|      | backisde processing.                                                                     | 102 |

р

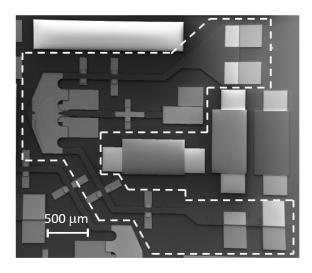

| 6.30 | The outline of one six port reflectometer probe chip prior to chip release: |     |

|------|-----------------------------------------------------------------------------|-----|

|      | backside view. The chip is enclosed in the dashed white rectangle           | 103 |

| 6.31 | SEM of the backside of the six port reflectometer probe chip prior to chip  |     |

|      | release                                                                     | 103 |

### Chapter 1

### Introduction

#### 1.1 Metrology for Submillimeter-wave Spectrum

The submillimeter-wave region (300 GHz-3 THz) is one of the the most scientifically useful yet least explored regions of the electromagnetic spectrum. This region is crucial to remote sensing and radio astronomy, molecular spectroscopy, imaging for medical or security purposes and other applications [17–21]. Unfortunately, the measurement infrastructure for developing submillimeter-wave devices and materials remains limited, too large in size, cost-prohibitive, or non-existent. and is often ill-adapted for direct in-situ characterization.

Among the most important instruments for characterizing RF, microwave and millimeterwave devices is the vector network analyzer (VNA). The technology of vector network analyzers has been significantly improved since it was first commercially introduced by Hewlett Packard in 1967, the HP 8410. However, it has been less than a decade that VNA measurements of S-parameters have been extended into the terahertz frequency range with external frequency extension modules [22, 23].

Another example of limited measurement infrastructure for terahertz applications is the waveguide and waveguide interfaces. Conceived by Lord Rayleigh in 1897 and rediscovered by G. C. Southworth and W. L. Barrow about fourty years later [24], the past century has witnessed the extensive application of this technology in RF, microwave and millimeter-wave ranges. However, it is found that the measurement precision and accuracy of submillimeter-wave wave and terahertz range instruments is limited by interconnection quality, repeatability,

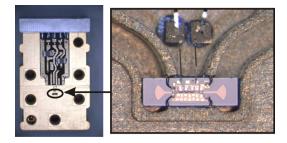

Figure 1.1: An integrated 340 GHz low noise amplifier chip mounted to a waveguide housing for measurement and characterization [1]. The right image is a close-up of the chip mounted to the housing.

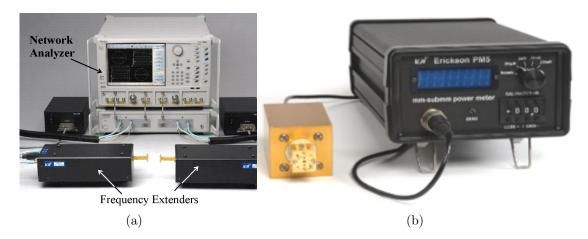

Figure 1.2: (a) Image of a PNAX vector network analyzer with terahertz frequency extension modules from Virginia Diodes (image courtesy of Agilent, Inc.). (b) Image of a PM5 power meter (image courtesy of Virginia Diodes, Inc.)

and the lack of traceable standards. Recognition of this issue has led, as a result, to new designs for waveguide flanges [25] and the establishment of a recent IEEE standard P1785 for waveguide interfaces above 100 GHz to at least 1 THz [26, 27].

Figure 1.1 illustrates a common approach to measuring submillimeter-wave and terahertz devices and materials. The device-under-test (DUT) to be characterized is mounted to a test fixture equipped with waveguide flanges that permit interfacing to standard test instrumentation such as a vector network analyzer (Figure 1.2a) or power meter equipped with waveguide flanges (Figure 1.2b).

Mounting of the DUT to a fixture is time-consuming, expensive, and requires deembedding of the fixture response from the measurement, which is a complex process that limits accuracy and precision. The preferred approach is to measure the DUT *in-situ*, without removing it from its native environment and introducing measurement error due to the

(b)

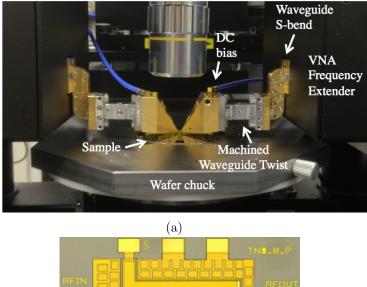

Figure 1.3: (a) On-wafer probes interfaced to VNA frequency extenders mounted to largearea positioners (Cascade PA200 probe station [2]. (b) Image of an InP amplifier, developed by Northrup Grumman, that is the first to produce gain at frequencies exceeding 1 THz [3].

fixture. An example is shown in Figure 1.3a, which shows a measurement system equipped with on-wafer probes that permit direct interfacing to planar devices and integrated circuits for characterization on wafer, without need for separating die and mounting them to a housing. The innovation of on-wafer probes developed at the University of Virginia allowed, for the first time, calibrated on-wafer measurement of electronic devices at frequencies over 1 THz and permitted the development and characterization of the world's first terahertz transistor in 2014 (Figure 1.3b) [3].

The prevalent approach for in-situ characterization of submillimeter-wave devices is to measure the device under test (DUT) in-situ with on-wafer probes. However, there is usually considerable overhead associated with this approach. The frequency extender modules that are needed to interface to coplanar on-wafer probes must be mounted to large-area translation stages for positioning and alignment. This places limitations on the number of

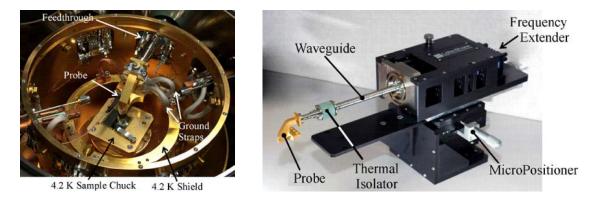

Figure 1.4: Photograph of (a) a cryogenic probe station with feedthroughs for on-wafer probe measurements. (b) Probe feed-through assembly [4,5].

ports that can be measured practically on a standard probe station, due to the footprint of the extenders and how closely they can be positioned. In addition, measurements of a DUT within a shielded enclosure, such as a vacuum chamber or cryostat, is problematic. Typically, measurement instruments must be placed outside the chamber and be interfaced to the DUT within through hermetically-sealed or thermally-isolated feedthroughs. Thus contributes to system complexity and cost, increases loss, and reduces dynamic range. An example of such as system is shown in Figure 1.4. The submillimeter-wave research community has immediate need for in-situ measurement capabilities as described above, and the work in this dissertation aims to address this issue.

#### 1.2 Micromachined On-Wafer Probes

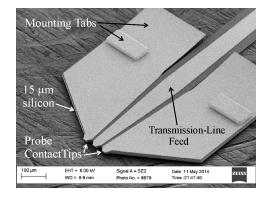

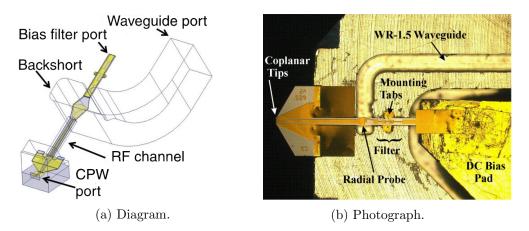

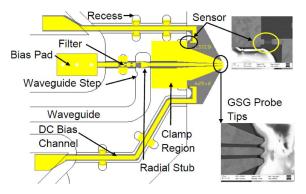

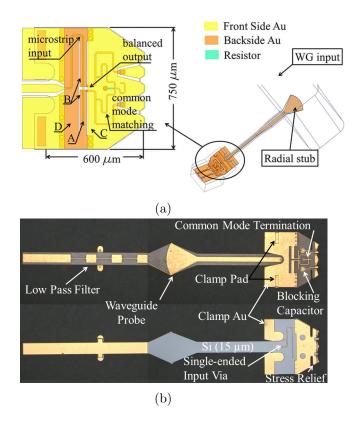

State-of-the-art micromachining technologies developed at the University of Virginia [6,28,29] has made in-situ on wafer characterization possible up to 1 THz. The SEM image of a WR-1.0 (750-1100 GHz) micromachined probe is shown in Figure 1.5. The micromachined probe is a single, integrated module fabricated from thin (15  $\mu$ m) micromachined high-resistivity silicon and includes metallized electrical contacts for direct interfacing and physical contact to device under test (DUTs). Figure 1.6 shows a diagram and an example of an on-wafer probe chip for the WR-1.5 band (500–750 GHz) mounted to its housing (a split-block waveguide for interfacing to back-end waveguide-based VNA frequency extenders) [7]. The probe chip protrudes about 500  $\mu$ m from the housing to permit contact with DUT's on a wafer. As the

Figure 1.5: Scanning electron micrograph (SEM) of a micromachined on-wafer probe for the WR-1.0 (750-1100 GHz) band on 15  $\mu$ m thick high-resistivity silicon [6].

Figure 1.6: A WR-1.5 micromachined probe mounted to its housing [7].

micromachined probe is compatible with other standard microfabrication processes, it can serve as a foundation for fully-integrated terahertz instruments, including power detectors and frequency multiplier sources based on Schottky diodes.

Design and fabrication of the probe described above is based on micromachining of silicon-on-insulator (SOI) substrates. Because of its well-understood RF properties, low loss, mature processing technology, and mechanical robustness [28], high-resistivity ( $\rho > 10$  k $\Omega$ -cm), silicon has proven to be an excellent choice for realizing robust terahertz probes and also represents a natural choice as the host support substrate for realizing fully integrated instruments and sensors based on compound semiconductors (e.g., GaAs).

### 1.3 Heterogeneous Integration of GaAs Diodes onto Si Membranes

Schottky diodes are a critical device technology for applications in the submillimeter-wave spectrum, playing a central role as power detectors, heterodyne receivers, and frequency multipliers. Over the decades, this device has evolved from a single-element whisker-contacted geometry [30–32] to a planar chip with integrated finger contact [33] and finally heterogeneously integrated device bonded to host substrates supporting associated circuitry [34–38].

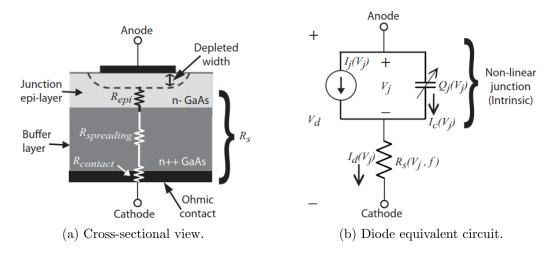

Heterogeneous integration of III-V semiconductor epitaxy onto silicon has proven an effective approach for realizing novel devices that combine outstanding RF characteristics with a mechanically-robust and low-loss substrate [8,39,40]. Integration processes have been shown to provide flexibility in engineering new device geometries and can be exploited to mitigate the electrical parasitics and thermal grounding bottlenecks that frequently limit the performance of terahertz components [13].

GaAs, the primary material used to realize submillimeter-wave Schottky diodes, has a number of severe limitations—its thermal conductivity and mechanical robustness are poor compared to silicon. Moreover, the material is fragile and ill-suited for the direct contact applications such as the on-wafer probes. Fortunately, heterogeneous integration of compound semiconductors onto support substrates, through epitaxial growth or epitaxial transfer, can address this issue. In contrast to epitaxial growth, epitaxial transfer (wafer bonding) is not limited by material issues such as lattice mismatch, coefficient of thermal expansion (CTE) or polarities [41,42]. Direct bonding can provide high thermal conductivity compared to indirect wafer bonding where an intermediate polymer is placed in between, but this method requires excellent surface cleanness and smoothness of the wafers which limits its applications in many instruments [43].

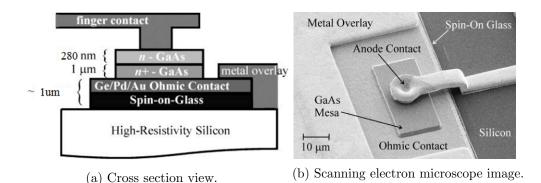

Recent research at the University of Virginia initiated the development of a heterogeneous integration technology for fabricating GaAs Schottky diodes on silicon [8,44] and silicon support membranes [9], which is also compatible with the process of micromachining of on-wafer probes. Figure 1.7b shows the diode epitaxy is bonded to a host, high-resistivity

Figure 1.7: A quasi-vertical GaAs Schottky diode fabricated on a high-resistivity ( $\rho > 10$  k $\Omega$ -cm) silicon substrate [8].

Figure 1.8: Integrated quasi-vertical GaAs Schottky diodes fabricated on a thin (15  $\mu$ m) silicon membrane with beamleads [9].

silicon substrate that supports both the diode and its associated circuitry. Figure 1.8 shows a GaAs Schottky diode integrated on a high-resistivity silicon substrate and a three-element diode array fabricated on a thin (15  $\mu$ m) silicon membrane with associated circuitry and beamleads. This initial work serves as the foundation of fully integrated submillimeter-wave and terahertz instruments detailed in this work.

The device shown in Figure 1.7b is a quasi-vertical diode in which ohmic contact lies beneath a GaAs mesa and the anode. As a result, the diode current flows through the bulk GaAs material instead of along the surface, as it does for the more common laterally-oriented planar diodes. Current crowding due to the skin and proximity effects associated with the lateral current flow near the diode surface [13,45] are understood to increase the RF series resistance of planar diodes. Diode series resistance and parasitic capacitance, critical factors that limit the device's performance at terahertz frequencies, are generally found to be lower for vertically-oriented devices. Quasi-vertical GaAs Schottky diodes integrated onto silicon can serve as the electronic calibration standard, based on their voltage-dependent impedance. After the RF on-wafer characterization of the diodes to obtain the S-parameters as a function of bias, the diodes can be subsequently used as the standard for electronic calibration. This allows full on-wafer calibration without need for moving or repositioning wafer probes onto the standards' contact pads.

### 1.4 Electronic Calibration at Submillimeter Wavelengths using Schottky Diodes as On-Wafer Standards

Measurement accuracy, precision and repeatability are of fundamental importance in characterizing the scattering parameters of devices and circuits using vector network analyzers (VNAs). The repeatability associated with interfaces and interconnects between network analyzers and devices-under-test (DUTs) fundamentally limits measurement precision and introduces nonsystematic error that cannot be eliminated through calibration. This issue is particularly important for measurements in the submillimeter-wave spectrum, as small offsets in the mating of interfaces and practical restrictions on mechanical tolerances and can conspire to produce significant electrical discontinuities that are difficult to predict or model.

With the development of wafer probes for the submillimeter-wave region [28,29], interface repeatability has become a more prevalent issue for on-wafer scattering parameter characterization. Misalignment in the positioning and placement of probes onto the contact pads of calibration standards and DUTs can have considerable influence on measurement uncertainty. Variations in the force applied between the probe tips and mating surfaces during such measurements result in uncertainties in contact resistance. Physical displacement of the probe from the measurement reference plane during calibration, due for instance to skating or overdrive, can produce more consequential errors. Such offsets introduce phase error that scales with frequency. Prior work has, in fact, identified phase error associated with positioning misalignment, skating, or overdrive as a major contributor to uncertainty for on-wafer scattering parameter measurements above 500 GHz [46, 47]. Electronically-tunable impedance standards that do not require movement and repositioning between calibration measurements have potential to mitigate the issues noted above, by eliminating uncertainty arising from misalignment or variations in applied contact force that are associated with skating of the probe, bowing of the wafer [10], micrometer backlash and other physical non-idealities of the measurement system. Since their introduction more than two decades ago, electronic calibration techniques have become an important technique for microwave scattering parameter characterization [48–53]. Because they eliminate the requirement for physical connection and re-connection of standards between calibration measurements, electronic standards provide convenience as well as the potential to mitigate measurement uncertainty associated with the electrical repeatability of interfaces.

### 1.5 On-Wafer Micromachined Probe with Submillimeter-wave Sensors

The micromachining and heterogeneous integration technologies, illustrated in Figure 1.6 and 1.7b, make on-wafer micromachined probes with integrated sensors a feasible approach for submillimeter-wave metrology. Some of the potential applications of this approach are integrated on-wafer probes with single diode temperature sensors, single diode power detectors and six port reflectometer [54] with an ensemble of diode detectors, among other types of instruments.

The report of integrating sensors onto micromachined on-wafer probes (Figure 1.9) was described in [10]. A symmetrical integrated resistive strain sensor pair was used to

Figure 1.9: In-block view of the WR-1.5 integrated strain sensor probe chip [10].

Figure 1.10: Micromachined on-wafer probes with integrated baluns. (a) Full model of the WR-10 balun probe in HFSS [11]. (b) Top side and bottom side geometry of the WR-5.1 micromachined balun probe head. The probe design shown has a ground-signal-ground-signal-ground-signal-ground tip configuration [12].

monitor and control the contact force of a terahertz on-wafer probe to improve measurement repeatability of terahertz probing and enable contact force measurement without modification to the standard probe station. Film resistors [11] and metal-insulator-metal capacitors [12,55] have also been successfully integrated onto micromachined on-wafer probes (Figure 1.10), enabling circuit design flexibility of more innovative designs to be incorporated onto micromachined on-wafer probes to realize differential probes.

By integrating power detector circuits or diode temperature sensors onto micromachined probes, it is possible to perform direct on-wafer power and S-parameters measurement, as well as temperature measurements. By integrating detectors to form a six port reflectometer (an alternative architecture of VNA), which is then integrated onto a micromachined on-wafer probe, a simple, compact, affordable alternative VNA can be realized.

#### **1.6** Outline of Dissertation

The first chapter introduces the development of one of the technical foundations of the dissertation work, an epitaxy transfer process for heterogeneous integration of submillimeterwave GaAs Schottky diodes on silicon using SU-8. Previous work and process refinement are discussed. Diodes fabricated using the revised process are characterized by both DC measurement and submillimeter-wave on-wafer characterization.

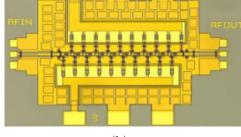

Chapter 3 discusses the new implementation of an integrated frequency quadrupler, based on previous work. An integrated frequency quadrupler operating at 160 GHz, producing 100 mW of output power, and achieving peak efficiency of 25.5% is described. The quadrupler design is based on prior art and consists of GaAs Schottky diodes with epitaxy transferred to a micromachined silicon carrier forming a heterogeneously-integrated chip. The newlydeveloped fabrication process described in Chapter 2, which eliminates high temperature annealing and utilizes SU-8 for adhesive bonding, was employed to realize the circuit.

The material presented in Chapter 4 presents the first demonstration of an electronic standard for on-wafer calibration at submillimeter-wave frequencies. The standard is based on the voltage-dependent impedance presented by a GaAs Schottky diode and allows full on-wafer calibration without need for moving or repositioning wafer probes onto contact pads. Both one port and two port on-wafer S-parameter measurement applications are discussed.

Chapter 5 reports the first implementation of heterogenous integration of GaAs Schottky diodes onto micromachined on-wafer probes to realize a temperature sensor. Design and fabrication of the probe, as well as fabrication and measurement of prototype diodes for the temperature sensor are described.

Chapter 6 presents a final example of heterogeneous integration of GaAs Schottky diodes onto micromachined on-wafer probes to realize a sampled line type six port reflectometer. The design of the probe, simulations of its calibration for one port S-parameter measurement, and the fabrication process and measurement plan are described.

The final chapter summaries the contributions and general conclusions as a result of this work. Potential areas of future investigation that stem from the work are also discussed.

### Chapter 2

# Epitaxy Transfer for Heterogeneous Integration of GaAs Schottky Diodes on Silicon

This chapter is based on the following publication, with some modifications and augmentations.

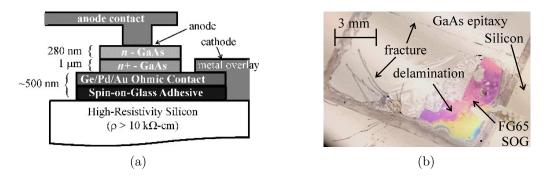

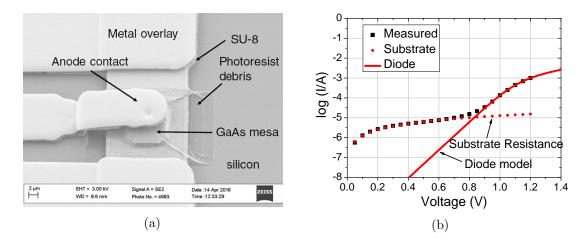

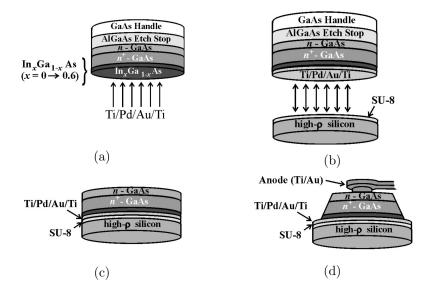

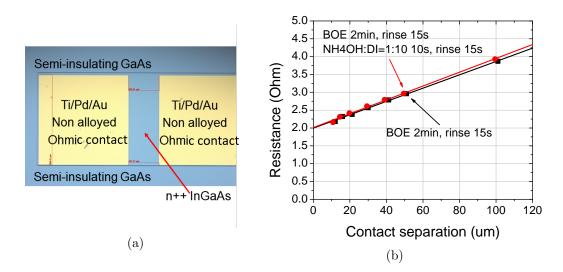

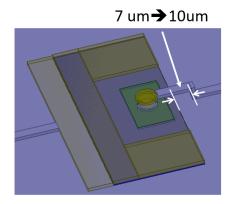

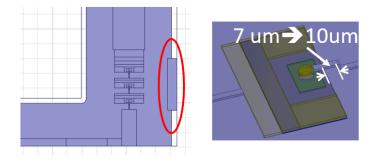

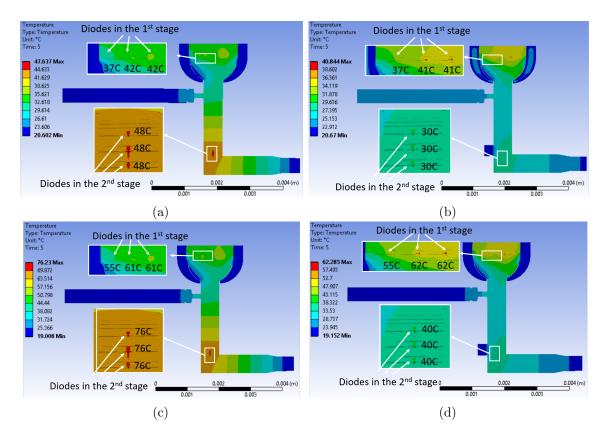

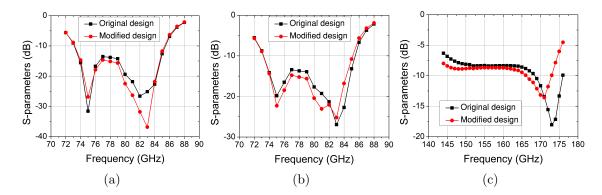

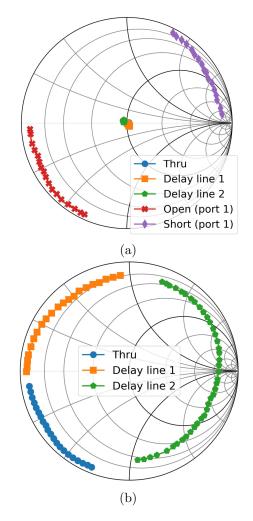

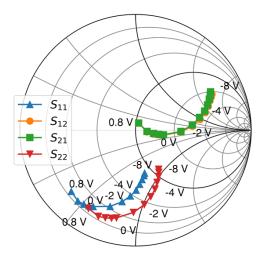

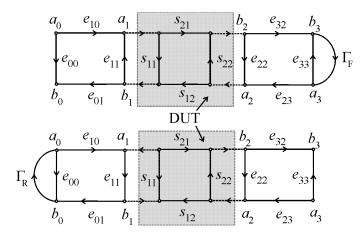

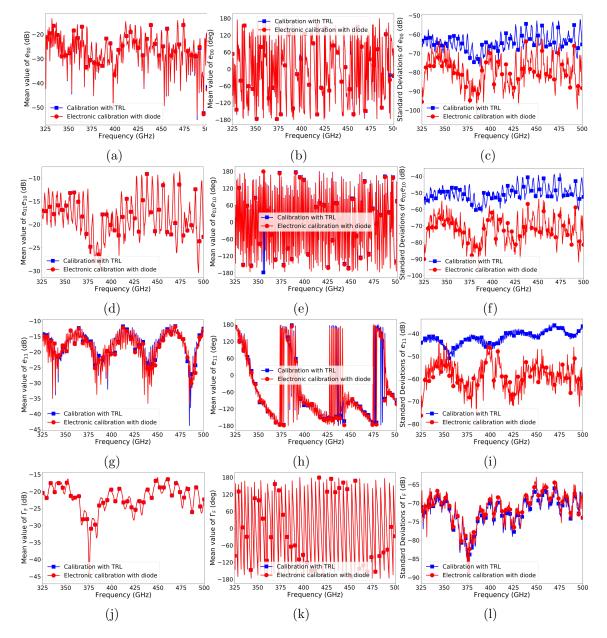

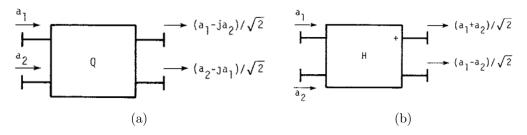

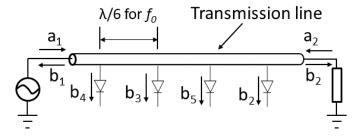

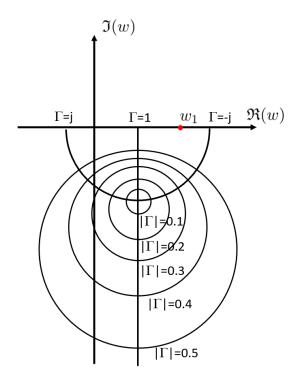

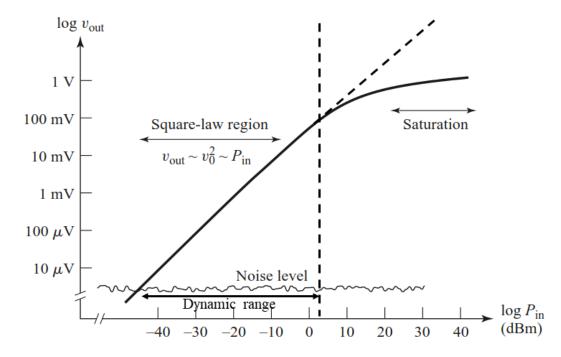

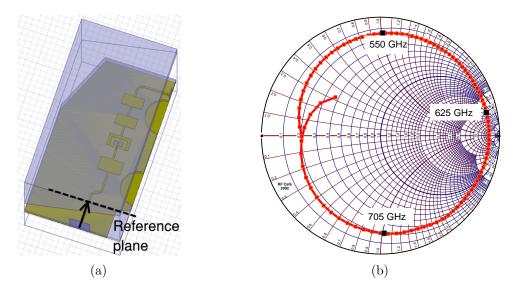

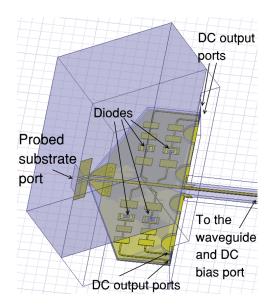

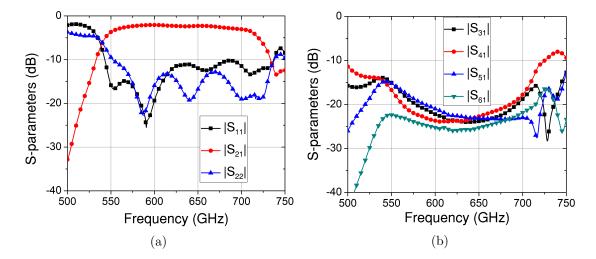

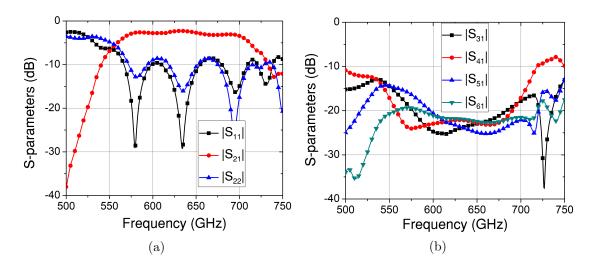

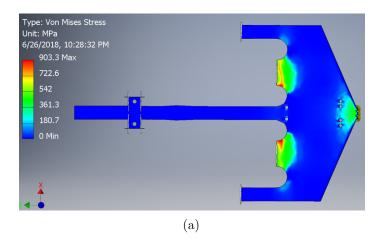

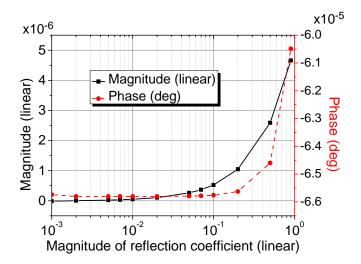

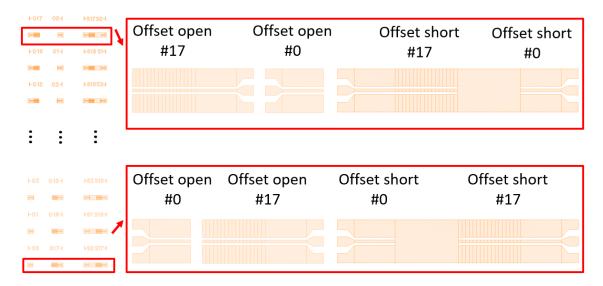

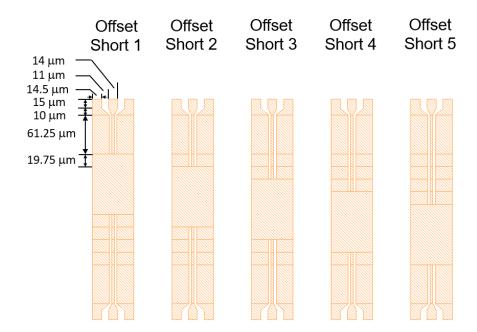

<u>L. Xie</u> (co-first author), S. Nadri (co-first author), N. Alijabbari, M. E. Cyberey, M. F. Bauwens, A. W. Lichtenberger, N. Scott Barker, and R. M. Weikle, II, "An epitaxy transfer process for heterogeneous integration of submillimeter-wave GaAs Schottky diodes on silicon using SU-8," *IEEE Electron Device Letters*, vol. 38, no. 11, pp. 1-4, Nov. 2017, doi: 10.1109/LED.2017.2756920