# Ultra-Low-Power Inter-Integrated Circuit Implementation for Fabric-Based Self-Powered Systems

Α

**Thesis**

Presented to

the faculty of the School of Engineering and Applied Science

University of Virginia

In partial fulfillment of the requirements for the degree

**Master of Science**

by

**Zhenghong Chen**

April 2023

#### **Abstract**

With the advance of various energy harvesting and storage devices, self-powered wearable systems have gained significant interest in the past few years. In addition, the growing focus on fibers with digital devices is driving the potential for fabrics with digital systems for health monitoring and human-machine interfaces. While such digital-enable fabric systems consist of various distributed digital devices, a low-power serial communication component is in high demand. The standard Serial Peripheral Interface (SPI) commonly used in device connection is unsuitable for communication in fiber because the bit width of the slave select signal (SS) increases with the number of networked devices.

To address this research gap, we propose using Inter-Integrated Circuit (I<sup>2</sup>C) for communication in fiber and presenting the SPI-I<sup>2</sup>C Protocol Converter chip for data transfer from the SPI to the I<sup>2</sup>C bus. Our research involves designing and implementing a low-power I<sup>2</sup>C module with tunable frequency, data width, and output voltage. The I<sup>2</sup>C module on the chip can work at 0.4 V supply voltage with only 2.6 nW static power. In addition, we designed the I<sup>2</sup>C controller on the chip that can adaptively adjust the drive capability to balance power consumption and reliability when more devices are connected. Finally, we integrate the I<sup>2</sup>C module into the System-on-Chip (SoC) using the ARM Advanced Peripheral Bus (APB) to complete the digital-enabled fabric system.

## Acknowledgments

I would like to express my deepest gratitude to my advisor, Prof. Benton H. Calhoun, for his invaluable advice, unwavering support, and endless patience throughout my master's degree.

I also want to extend my heartfelt appreciation to my friends and collaborators, Xinjian Liu and Suprio Bhattacharya, who provided critical assistance in digital circuit design, tape-out processes, and chip testing. Their expertise, dedication, and hard work were essential in bringing this project to fruition.

I want to thank Yimin Gao from the University of Virginia High-Performance Low-Power Lab for his advice throughout designing the digital circuit and optimizing the SoC. Thank you, Yimin, for your support and contribution to this work.

I wish to thank my committee members, Prof. Todd A. DeLong and Prof. Steven M. Bowers, for their help and support throughout my master's degree.

Finally, I thank my parents for their selfless love and care. With their help, I have a better living and learning environment, as well as more opportunities for growth.

## **Contents**

| Al | bstrac | et e e e e e e e e e e e e e e e e e e                    | ii  |

|----|--------|-----------------------------------------------------------|-----|

| A  | cknow  | vledgments                                                | iii |

| 1  | Intr   | oduction                                                  | 2   |

|    | 1.1    | Related Work                                              | . 3 |

|    |        | 1.1.1 I <sup>2</sup> C Protocol Based Multi-Device System | . 3 |

|    |        | 1.1.2 SPI to I <sup>2</sup> C Protocol Conversion         | . 3 |

|    | 1.2    | Motivation                                                | . 4 |

|    |        | 1.2.1 Fabric-Based Self-Powered System                    | . 4 |

|    |        | 1.2.2 Communication for Ultra-Low-Power System            | . 5 |

|    | 1.3    | Thesis statement                                          | . 6 |

| 2  | Bac    | kground Theory                                            | 7   |

|    | 2.1    | Communication in Integrated Circuits                      | . 7 |

|    | 2.2    | Serial Communication Protocols                            | . 8 |

|    |        | 2.2.1 Serial Peripheral Interface (SPI)                   | . 8 |

|   |      | 2.2.2               | Inter-Integrated Circuit (I <sup>2</sup> C)                    | 10 |

|---|------|---------------------|----------------------------------------------------------------|----|

| 3 | Desi | gn Proc             | eess of I <sup>2</sup> C                                       | 12 |

|   | 3.1  | I <sup>2</sup> C Co | omponents Specification                                        | 13 |

|   |      | 3.1.1               | I <sup>2</sup> C Master and Slave Architecture                 | 13 |

|   |      | 3.1.2               | $I^2C$ module Port List                                        | 14 |

|   |      | 3.1.3               | I <sup>2</sup> C Integrated Architecture                       | 16 |

|   |      | 3.1.4               | Open-Drain Structure for Bidirectional Communication           | 17 |

|   |      | 3.1.5               | SDA and SCL                                                    | 19 |

|   |      | 3.1.6               | Master and Slave Finite state machine                          | 20 |

|   |      | 3.1.7               | I <sup>2</sup> C Data Register                                 | 24 |

|   | 3.2  | Simula              | ation and Result                                               | 24 |

| 4 | Desi | gn and              | Implementation of SPI-I <sup>2</sup> C Protocol Converter chip | 28 |

|   | 4.1  | RTL to              | GDSII flow for I <sup>2</sup> C Module                         | 29 |

|   | 4.2  | I <sup>2</sup> C Ac | lditional Circuit Design                                       | 31 |

|   | 4.3  | Caden               | ce Spactre Simulation                                          | 32 |

|   | 4.4  | Schem               | atic and Layout of Chip                                        | 34 |

| 5 | Chip | Test R              | esults and Analysis                                            | 36 |

|   | 5.1  | Build 7             | Testing Board                                                  | 36 |

|   | 5.2  | I <sup>2</sup> C Ba | sic Function Test                                              | 37 |

|   | 5.3  | Power               | Consumption Measurement and Modeling                           | 40 |

| В | SPI-  | I <sup>2</sup> C Pro | tocol Converter Chip Test Environment                                                      | 60 |

|---|-------|----------------------|--------------------------------------------------------------------------------------------|----|

| A | Veri  | log Cod              | e of I <sup>2</sup> C                                                                      | 59 |

|   | 7.2   | System               | on Chip                                                                                    | 58 |

|   |       | 7.1.3                | Reliability and Efficiency                                                                 | 57 |

|   |       | 7.1.2                | Design $I^2C$ Slave without Clock                                                          | 57 |

|   |       | 7.1.1                | Optimize Open-Drain Circuit                                                                | 56 |

|   | 7.1   | I <sup>2</sup> C Pro | otocol Module                                                                              | 56 |

| 7 | Cone  | clusions             | and Future Directions                                                                      | 56 |

|   |       | 6.3.3                | Simulation Result                                                                          | 53 |

|   |       | 6.3.2                | Design $I^2C$ operation program                                                            | 52 |

|   |       | 6.3.1                | Structure of SoC and Testbench                                                             | 50 |

|   | 6.3   | Models               | sim Simulation                                                                             | 50 |

|   |       | 6.2.2                | Build APB to $I^2C$ Logic $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 48 |

|   |       | 6.2.1                | Update Address Map                                                                         | 47 |

|   | 6.2   | Connec               | et I <sup>2</sup> C module with APB bus                                                    | 47 |

|   | 6.1   | SoC A                | rchitecture                                                                                | 46 |

| 6 | Integ | grate th             | e I <sup>2</sup> C Module into the SoC                                                     | 46 |

|   | 5.4   | System               | Topology Test                                                                              | 43 |

|   |       | 5.3.2                | Active Power                                                                               | 41 |

|   |       | 5.3.1                | Static Power                                                                               | 40 |

| Glossary     | 61 |

|--------------|----|

|              |    |

| Bibliography | 67 |

## **Chapter 1**

### Introduction

In recent years, there has been a significant surge in interest in developing self-powered systems for various applications, including wireless sensors [1] [2] and Internet of Things (IoT) devices [3] [4]. These systems utilize energy harvesting techniques, such as solar, thermal, or kinetic energy harvesting, to generate energy from the environment and sustain their operation without needing batteries or external power sources. Self-powered systems [5] offer numerous advantages, including reduced maintenance costs, improved reliability, and increased flexibility in terms of where and how they can be used. To achieve self-powered, wearable electronics have integrated energy harvesters such as photovoltaic cells, piezoelectric generators [6] [7], and enzymatic or microbial biofuel cells [8] to balance energy consumption. These wearable systems [9] can eliminate the need for frequent recharges and wired power transmission, allowing for uninterrupted use and an improved user experience.

Current wearable devices [10] [11] are limited in their ability to collect physiological data due to their relatively rigid structure, unacceptable size, and limited contact area with the body. In contrast, traditional clothing fabrics offer a promising opportunity in power harvesting and physiological variables analysis since they already come into contact with large surface areas of the human body. Fibers, the basic building blocks of fabrics, offer a natural candidate for enabling sensory, memory, and other digital functions. Existing technologies have enabled digital com-

ponents into flexible polymer fiber bundles, allowing access to the collection of devices inside the fiber through connection ports at the end of the fiber [12] [13]. This presents an opportunity to realize digital systems integration into clothing, providing a solution for the comfortable and senseless self-powered wearable system.

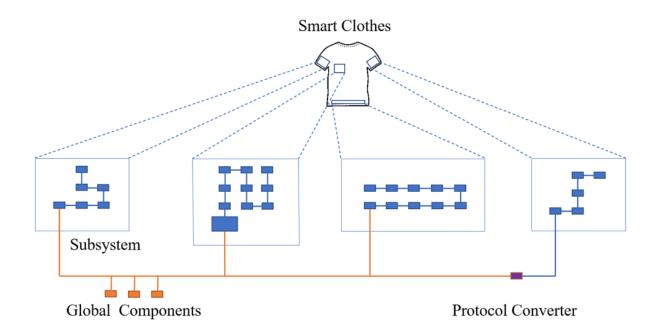

The Fabric-Based Distributed System aims to address the challenges posed by in-fiber digital devices size limited, which dimensions can not exceed 0.6mm. In this distributed system, the traditional structure is divided into smaller subsystems that can be distributed throughout a garment. Each subsystem can work independently, allowing for greater flexibility and customization. Besides the need to design each chip, the challenge is finding ways to interconnect these subsystems and chips in a reliable and efficient manner. We hope to find a suitable solution by exploring Serial Peripheral Interface (SPI) and Inter-Integrated Circuit (I<sup>2</sup>C) communication protocols to achieve interconnection while minimizing power consumption.

#### 1.1 Related Work

#### 1.1.1 I<sup>2</sup>C Protocol Based Multi-Device System

This custom home automation system [14] with eight devices interconnected via the  $I^2C$  protocol is programmable and modular. The  $I^2C$  protocol has the characteristics of simple structure and high compatibility in building a multi-device system. This user provides a technical basis for customizing devices in the system. The novelty of the subject lies in the combination of communication protocols and software tools to obtain reconfigurable, open-source, custom-made applications.

#### 1.1.2 SPI to I<sup>2</sup>C Protocol Conversion

SPI to I<sup>2</sup>C Protocol Conversion Unit [15] proposes a novel scheme to convert SPI to I<sup>2</sup>C by connecting the output of the SPI slave to the input of the I<sup>2</sup>C master and using FIFOs to build the

protocol conversion unit. This solution solves the problem of SPI and I<sup>2</sup>C being out of sync and operating at different frequencies, enabling the interconnection of these two protocol systems in low-power embedded systems. Although the proposed design has been successfully implemented on Field Programmable Gate Array (FPGA), it only supports one-way conversion from SPI to I<sup>2</sup>C. Nonetheless, the approach presented in this paper provides a promising basis for future work on bidirectional protocol translation.

#### 1.2 Motivation

#### 1.2.1 Fabric-Based Self-Powered System

The Self-Powered Fabric-Based System is a densely integrated digital system comprising interconnected functional components distributed throughout various positions on clothing. To enhance clothing comfort, integrated circuits must be divided into multiple ultra-low-power microchips that form distributed subsystems, enabling each subsystem to function independently. Moreover, the system's power consumption must be maintained within the nanowatts (nW) range, as limited by the size of the battery and energy harvester.

In the previous design, the SPI protocol was utilized as a communication tool for components due to its low power consumption and high efficiency, making it possible to achieve internal communication within the subsystem. However, regarding global communication, SPI is not ideal for several reasons. Each subsystem may act as a master, and SPI only supports single-master systems when interconnected. This limitation makes SPI unsuitable for global communication, where multiple subsystems need to communicate with each other. In addition, as the number of networked devices increases, the bit width of the SPI slave select signal (SS) also increases. This limitation makes SPI unsuitable for communication in fiber because the fiber only allows for limited transmission lines, which limits the number of devices that can be connected.

Figure 1.1: Fabric-Based Self-Powered System

#### **1.2.2** Communication for Ultra-Low-Power System

Sensors play a critical role in human-computer interaction and are indispensable to such systems. Achieving low-power or self-powered systems requires using sensors with the lowest supply voltage available. While several sensors are available on the Texas Instruments website, only a few options meet the controlled supply voltage requirements of the envisioned system, which is between 0.6-1.8V. While these sensors may not be suitable for the Self-Powered Fabric-Based System due to more integrated design requirements for the system, they are highly relevant when building a low-power embedded system where voltage and power consumption are top priorities. In general, sensors with I<sup>2</sup>C protocol have lower supply voltage requirements than other sensors.

Our current System on Chip (SoC) only supports SPI components, which means that a conversion structure from SPI to I<sup>2</sup>C needs to be designed or an I<sup>2</sup>C module needs to be incorporated into the SoC to achieve the desired functionality.

Table 1.1: Sensors

| Classification        | Product      | Interface               | Supply Voltage (min) (V) |

|-----------------------|--------------|-------------------------|--------------------------|

| Temperature Sensors   | TMP114 [16]  | I <sup>2</sup> C, SMBus | 1.08                     |

|                       | TMP126 [17]  | SPI                     | 1.26                     |

|                       | TMP144 [18]  | UART                    | 1.4                      |

| Humidity Sensors      | HDC3022 [19] | I <sup>2</sup> C        | 1.62                     |

| Ambient light sensors | OPT3005 [20] | I <sup>2</sup> C        | 1.6                      |

#### 1.3 Thesis statement

- 1. Design the customizable  $I^2C$  module with tunable frequency, data width, and output voltage. Power consumption measurement and analysis assess the viability of embedding the module in a ultra-low-power system.

- 2. Extend the function and efficiency of the distributed system through implementation of SPI- $I^2C$  Protocol Converter chip.

- 3. Optimize the System-on-Chip (SoC) performance with integrate an I<sup>2</sup>C module.

## **Chapter 2**

## **Background Theory**

This chapter will provide an overview of communication techniques used in integrated circuits, including using buses for communication, the underlying theory of interconnects, and introducing bus protocols such as  $I^2C$  and SPI.

#### 2.1 Communication in Integrated Circuits

Due to the modular structure of distributed systems, integrated circuit (IC) modules with distinct functions are packaged separately in the chip, requiring communication as an essential aspect. Communication within ICs can be achieved through serial or parallel transfers, which can be synchronous or asynchronous.

Serial communication involves transmitting data bits sequentially, one after the other. In contrast, parallel communication uses multiple transmission lines to transmit each bit simultaneously, resulting in high throughput but increased power consumption and area costs due to the need for more wires. Synchronous communication utilizes a dedicated clock signal to synchronize transfers between components, with the clock signal indicating when the receiver should sample the data on the line. On the other hand, asynchronous communication uses a handshake protocol to

synchronize transfers without relying on a separate clock signal line. However, this approach can result in higher overhead, as many transmitted bits are utilized only for control purposes.

A bus is a set of wires that permits signals to be transmitted between one or more integrated circuits. In such communication, the device that initiates communication is referred to as the Master, and the device that responds to the communication request is known as the Slave. Moreover, the bridge connects different buses while a decoder selects the appropriate slave for receiving data. Later in the thesis, we will discuss interfaces like ARM Advanced Microcontroller Bus Architecture (AMBA), Advanced eXtensible Interface 4 (AXI4), and Advanced Peripheral Bus (APB) that utilize these concepts in signal transmission.

#### 2.2 Serial Communication Protocols

Serial Communication Protocols suit low-power embedded systems with simple structures and high transmission efficiency. In most cases, SPI is selected because it has the advantages of high transmission frequency, simple module structure, and low power consumption compared with I2C. In contrast, the advantages of I2C are high reliability, fewer transmission lines, and support for multiple masters. This thesis presents the design and implementation of the SPI-I<sup>2</sup>C protocol converter chip. The following section provides an introduction to the SPI and I<sup>2</sup>C communication protocols and compares their respective characteristics.

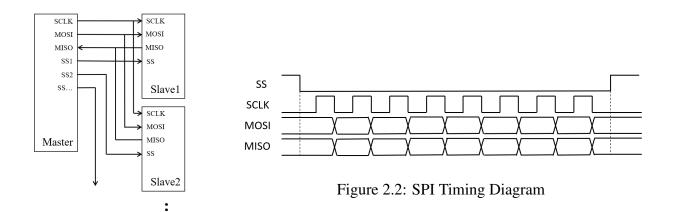

#### 2.2.1 Serial Peripheral Interface (SPI)

Serial Peripheral Interface (SPI) [21] [22] [23] is a synchronous serial full-duplex data transmission communication method introduced by Motorola. It is generally considered that the SPI protocol is a three-wire synchronous bus, but to connect multiple slave devices, each slave device needs to be equipped with a Chip Select signal (CS/SS). As the number of components connected to the system increases, the SPI master has to be designed with more chip-select signal lines to maintain

Figure 2.1: SPI Structure

control over all slaves in the system.

Table 2.1: I<sup>2</sup>C Lines List

| Classification | Signal Provider | Definition                |

|----------------|-----------------|---------------------------|

| SCLK           | Master          | Serial Clock              |

| MOSI           | Master          | Master Out Slave In       |

| MISO           | Slave           | Master In Slave Out       |

| CS/SS          | Master          | Chip Select, Slave Select |

To initiate a read/write operation in SPI, the master device first lowers the active SS line corresponding to the target slave and then sends clock pulses on the Serial Clock (SCLK). Depending on the mode selected, the output signal may be toggled by either the rising or falling edge of the clock pulse, while the input signal is sampled on the opposite edge. To perform a write operation, the master device transmits data on Master-Out-Slave-In (MOSI), while a read operation involves sampling Master-In-Slave-Out (MISO). Notably, SPI offers four different modes, each defining the operation at which specific edge and stable level value of the clock signal.

The SPI protocol offers a simple communication process that separates input and output data transmission for the master and slave. This separation eliminates the need for additional slave address

checks during communication since each slave has a separate chip select line. However, as the number of devices increases, more chip-select signal lines are required, which can lead to increase area and power consumption. In addition, the SPI protocol only supports one Master in the system, which impedes establishing crossover between multiple chips.

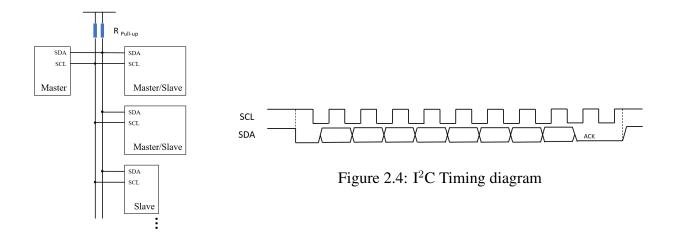

#### 2.2.2 Inter-Integrated Circuit (I<sup>2</sup>C)

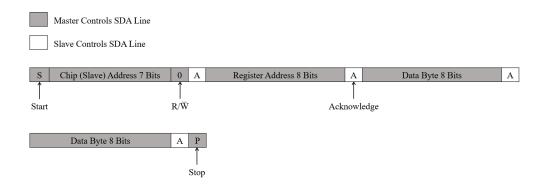

I<sup>2</sup>C or I2C [24] [25] is a simple bidirectional two-wire bus protocol standard developed by Philips, now NXP Semiconductors. I<sup>2</sup>C uses two signal lines, Serial Data (SDA) and Serial Clock (SCL), and does not rely on a physical chip selection signal or arbitration logic circuit. Instead, each I<sup>2</sup>C device has a unique seven-bit address for protocol handshake. I<sup>2</sup>C supports multiple master devices, and the protocol specification designates the initiating device as the master, while the all other devices on the bus are designated slaves.

Table 2.2: I<sup>2</sup>C Lines List

| Name | Signal Provider | Definition   |  |

|------|-----------------|--------------|--|

| SDA  | Master, Slave   | Serial Data  |  |

| SCL  | Master          | Serial Clock |  |

The I<sup>2</sup>C communication process consists of several steps. First, the master device sends a START signal, followed by a 7-bit device address and a bit for describing read or write operation. Upon receiving the data, the slave devices compare the address with their chip address to determine whether it is the intended recipient. If the comparison fails, the device waits until a STOP signal is received. In contrast, a successful comparison prompts the device to send an acknowledgment signal (ACK) back to the master. After receiving the ACK, the master can start transmitting or receiving data in 8-bit frames, with each frame followed by a one-bit response signal. Specifically, the master sends data, and the slave responds during write operations, while the reverse is true during read operations. When the transmission is complete, the master sends a STOP signal to release the bus, allowing other devices to access it, and all devices return to their initial state.

Figure 2.3: I<sup>2</sup>C Structure

Both the SCL and SDA lines in  $I^2C$  communication are open-drain and do not actively drive the bus high, ensuring that signal conflicts do not occur on the bus. When a device pulls the line to the ground, it transmits logic 0, and when it releases the line, the line returns to an idle state, transmitting logic 1. The following chapter will provide more detailed information on the specific structure and operation of  $I^2C$ .

Compared to the standard SPI protocol, which requires at least four signal lines and additional logic for multi-master structures, the I<sup>2</sup>C protocol requires only two. Even when using multiple slave devices, the number of signals needed remains low. Although the I<sup>2</sup>C protocol has a limited 7-bit address space, running out of 128 available addresses is rare. One significant advantage of the I<sup>2</sup>C protocol is the lightweight architecture Open-Drain implements multi-master device arbitration and routing. Moreover, read and write timing is relatively fixed and uniform, and the device driver is straightforward to write. Considering all these factors, we have decided to replace the SPI protocol with the I<sup>2</sup>C protocol in our current SoC design.

## **Chapter 3**

## **Design Process of I** $^2$ **C**

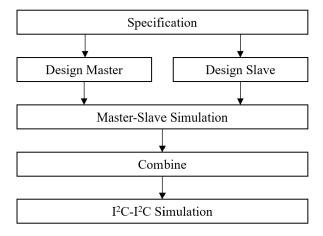

This chapter presents the complete design process for the I<sup>2</sup>C module. First, we formulated the design specifications by analyzing the I<sup>2</sup>C protocol articles [26] [27] [28] [29]. Next, we used Verilog to complete the Register Transfer Level (RTL) design for the I<sup>2</sup>C master and slave components. Then, we integrated these components and controlled them using an enable signal, resulting in higher integration and port savings. Additionally, we will conduct RTL simulation and analysis of the two design stages using Modelsim [30].

Figure 3.1: Flowchart of the Design Process

#### 3.1 I<sup>2</sup>C Components Specification

To discuss the design details of I<sup>2</sup>C, this section will cover several aspects. Firstly, the port planning for the I<sup>2</sup>C master and slave will be discussed. Next, the state machine for both read and write operations will be presented. Finally, the complete architecture block diagram will be introduced.

#### 3.1.1 I<sup>2</sup>C Master and Slave Architecture

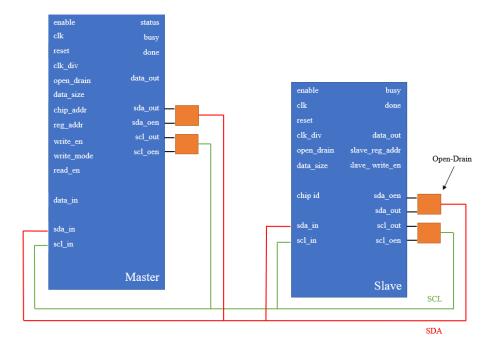

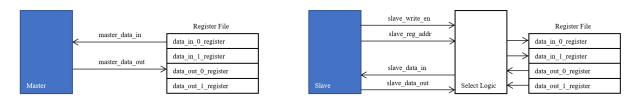

The planning architecture for the I<sup>2</sup>C master and slave modules is illustrated in the Fig.3.2, showing the input and output signals on either side of the block. The input signals include control signals, data input, SDA and SCL input signals, while the output signals consist of operating status display, data output, and SDA, SCL output control signals.

Figure 3.2: I<sup>2</sup>C Master and Slave Architecture

The open-drain structure used for bidirectional communication is implemented through analog circuit design, which is not included in the digital design RTL. However, this behavior can be

described using simple state statements in the testbench but cannot be achieved through synthesis.

#### 3.1.2 I<sup>2</sup>C module Port List

Since there are many repeated control signals in the port list in this chapter, the total ports are divided into five categories, Global, Master Logic, Slave Logic, Data path, SDA, and SCL. The  $I^2C$  port distribution described in this chapter is only used in this design.

Table 3.1: I<sup>2</sup>C module Shared Port List

| Classification | Port       | Input/Output | Function                   |

|----------------|------------|--------------|----------------------------|

| Global Setup   | enable     | Input        | Master/Slave mode Switch   |

|                | clk        | Input        | System Clock               |

|                | reset      | Input        | Reset signal               |

|                | clk_div    | Input        | Clock Divider              |

|                | open_drain | Input        | Open Drain Switch          |

|                | data_size  | Input        | Transmission data length   |

|                | done       | Output       | Finish Status Signal       |

|                | busy       | Output       | Work Status Signal         |

| Data Path      | data_in    | Input        | Data Input                 |

|                | data_out   | Output       | Data Output                |

| SDA and SCL    | sda_in     | Input        | Serial Data Input          |

|                | sda_out    | Output       | Serial Data Output         |

|                | sda_oen    | Output       | Serial Data Output Enable  |

|                | scl_in     | Input        | Serial clock Input         |

|                | scl_out    | Output       | Serial clock Output        |

|                | scl_oen    | Output       | Serial clock Output Enable |

The setting of the Enable signal does not entirely shut down the entire system but selects between

master and slave. By integrating the I<sup>2</sup>C master and slave components, controlled by the enable signal, we avoid any confusion that may arise from their simultaneous operation. When the enable signal is high, the master component works, and the slave is disabled. Conversely, when the enable signal is low, the slave is in the standby state.

The I<sup>2</sup>C design is designed to provide flexibility in data length, allowing the switching between 1-byte and 2-byte transmission modes by simply adjusting the input data\_size. Reviewing the actual usage of the I<sup>2</sup>C protocol in the I<sup>2</sup>C-based sensor purchased from Texas Instruments Incorporated shows that most data length in each communication is 2 Bytes. There also are some products whose data length in each communication is 1 Byte. Therefore, our design supports both data lengths to ensure communication with a wide range of I<sup>2</sup>C-based sensors.

The input clock serves as the primary operating frequency for the I<sup>2</sup>C module, while the clock divider is responsible for reducing the SCL output frequency. Modelsim and Cadence Spectre simulations show that a clock divider of at least 2 is required for stable operation. To ensure added stability and reliability, we have set the clock divider to 10 by default for all Modelsim and Cadence Spectre simulations and actual chip testing.

The several status ports are essential for checking the working status of the I<sup>2</sup>C interface and facilitating the debugging of I<sup>2</sup>C components. The Status port is particularly useful for monitoring the status of the I<sup>2</sup>C master, while the Done and Busy ports ensure that I<sup>2</sup>C transactions are completed. Additionally, these ports are reserved for the convenience of supervising the I<sup>2</sup>C reservation and preparing for the SoC interrupt system design.

The I<sup>2</sup>C master initiates the write or read operation when the write\_en or read\_en signal is high. If the slave does not support adjusting the data length, the write mode signal allows multiple I<sup>2</sup>C write operations to be performed continuously. When the write mode signal is high, the master's state machine skips the stop state and proceeds directly to the next write operation. This design is intended to enhance data transmission efficiency, particularly when transmitting large amounts of data.

The output register slave\_reg\_addr is specifically designed to store the address provided by the

Classification **Port** Input/Output **Function** Master Logic chip addr Input Target Chip Address reg addr Input Target Register Address write en Write Operation Start Signal Input write\_mode Input Write Operation Mode Switch read en Input Read Operation Start Signal Master State Machine Status status Output Slave Logic chip id Input Self Chip Address slave reg addr Output Slave Register address Slave write enable slave write en Output

Table 3.2: I<sup>2</sup>C module Independent Port List

master. Upon receipt of the slave\_write\_en signal, the slave will then store the incoming data at the address stored in slave\_reg\_addr.

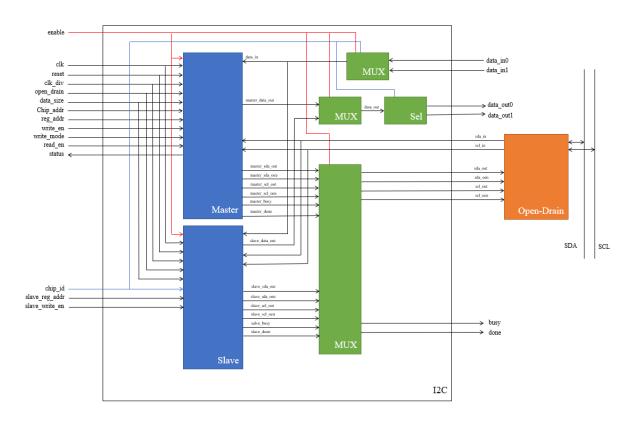

#### 3.1.3 I<sup>2</sup>C Integrated Architecture

Once the RTL designs of both the master and slave are complete, we merge them together to facilitate the synthesis and placement process described in the next chapter. However, this merging process can pose challenges due to the different port designs of the master and slave. To address this issue, we have created a complete structure diagram of the I<sup>2</sup>C system, as shown in Fig.3.3, which includes the master and slave components mentioned previously but also the data register for controlling signals. The shared ports are integrated, while the independent ports are placed separately. The enable signal in the output ports controls the multiplexer to determine whether the output comes from the master or slave. The control signal is the input signal of the system, and the Enable signal can control the work of the master or slave, so the influence of the input signal on closing the device can be ignored. But for Data, the input and output registers of Master are shared by 16-Bit and Slave. In addition, Slave additionally designed a set of 16-Bit registers to

17

temporarily place the transmitted data stored in different addresses.

Figure 3.3: I<sup>2</sup>C Architecture

#### 3.1.4 Open-Drain Structure for Bidirectional Communication

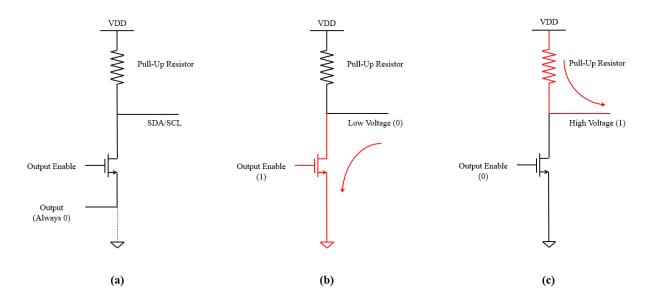

Open\_drain, consisting of a pull-up resistor and a pull-down transistor, is the transmission structure that supports multi-input coexistence and enables the interconnection of multiple devices on a single data line with the bidirectional data flow. When the output signal is high, the transistor can pull the line to low, which is usually grounded. Conversely, when the output signal is low, the pull-up resistor pulls the bus to a high voltage. As no device can output a high voltage on the line, the bus can never encounter the problem of communication signal collision. This enables the master and slave devises to communicate simultaneously on the same data line (SDA).

Fig.3.4 (a) depicts the Open-Drain structure. According to the I<sup>2</sup>C protocol specification, this

Figure 3.4: Open-Drain Structure

design has two input signals: "output" (OUT) and "output enable" (OEN). In the design and simulation presented in this article, the output is always 0, which means that the drain is grounded by default in the Open-Drain structure. Figures (b) and (c) illustrate the states of the Open-Drain circuit when the "output enable" signal is 0 and 1. We use conditional statements in the testbench during the ModelSim simulation to describe the Open-Drain design since it does not include an analog circuit structure, as shown in Fig.3.5.

```

assign SDA = master_sda_oen ? 1'bz : master_sda_out;

assign SDA = slave_sda_oen ? 1'bz : slave_sda_out ;

assign SCL = master_scl_oen ? 1'bz : master_scl_out;

assign SCL = slave_scl_oen ? 1'bz : slave_scl_out ;

pullup(SDA);

pullup(SCL);

```

Figure 3.5: Open-Drain Verilog Code

#### 3.1.5 SDA and SCL

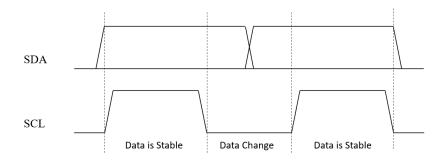

In the I<sup>2</sup>C protocol standard, Serial Data Bus (SDA) and Serial Clock Bus (SCL) are the only two data lines for data exchange, and there are some important rules to be aware of when using them for data transmission.

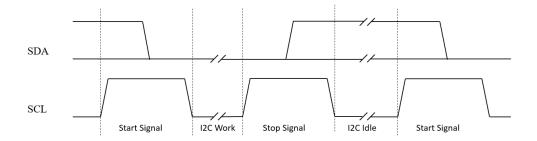

During data transmission, I<sup>2</sup>C supports the use of different frequencies. Having sound transfer requirements in place is critical to ensuring data is correct. During data transmission, when SCL is high (1), the voltage on SDA is fixed, and the receiver will read the value on SDA. When SCL is low (0), SDA changes to the value stored in the transmitter's shift register, as illustrated in Fig.3.6.

Figure 3.6: Data Transmission

Another important rule in the I<sup>2</sup>C protocol is that the falling edge of SDA is used as the beginning of communication. Therefore, in our design, we ensure that SDA is pulled down from high (1) to low (0) when SCL is high (1) since SDA is high when the system is idle, as shown in Fig.3.7. At the same time, the change when SCL is high is used to distinguish it from the data transmission process. In a complex system containing multiple I<sup>2</sup>Cs, the start signal (falling edge of SDA) wakes up all I<sup>2</sup>C slaves, which then checks whether their chip ID matches the address received from SDA. If there is no match, the slave returns to the idle state. Otherwise, it sends a response signal.

Figure 3.7: Start and Stop Signal

#### 3.1.6 Master and Slave Finite state machine

Compared to SPI, the Finite State Machine (FSM) structure of I<sup>2</sup>C is more complex due to its single data line(SDA), and the clock line (SCL) being generated only by the master to signal operation completion.

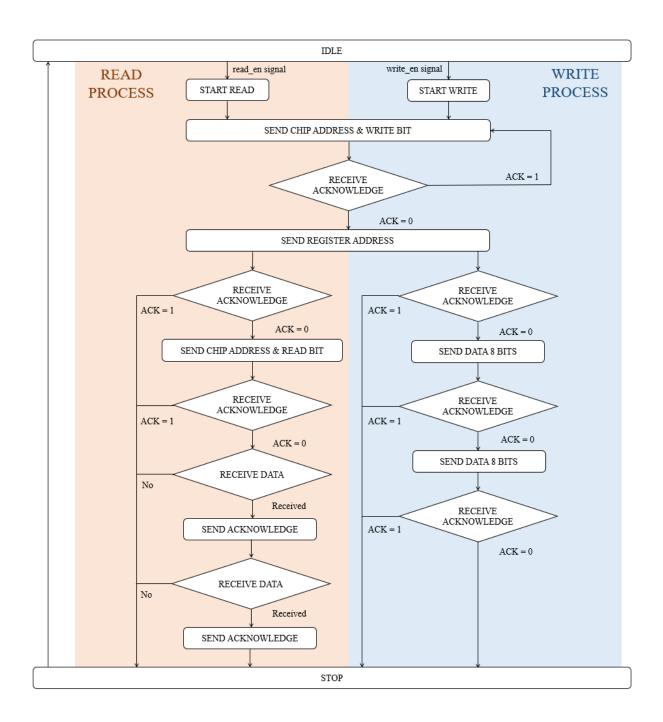

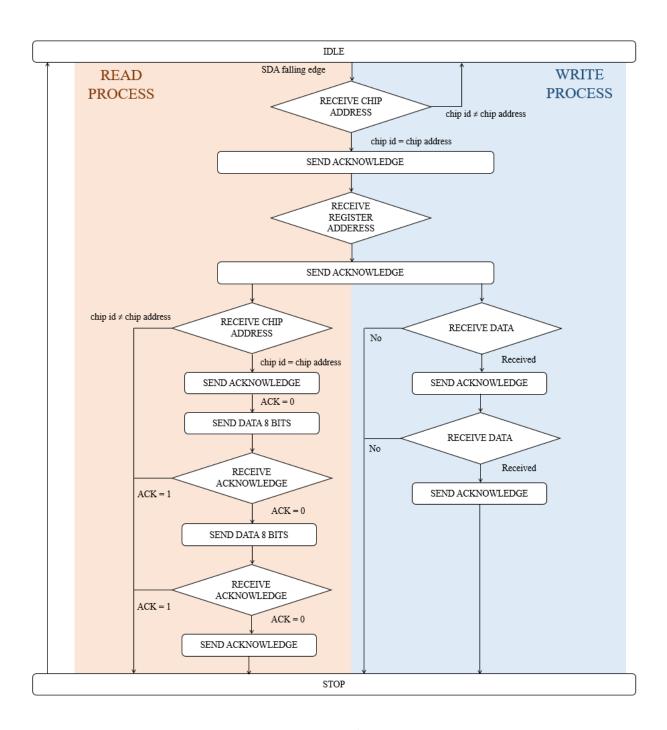

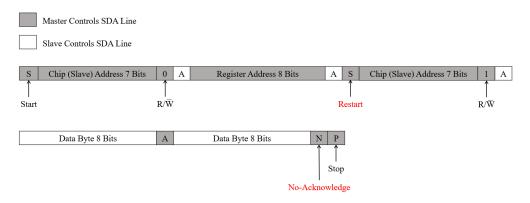

When the I<sup>2</sup>C master performs read and write operations, it behaves differently. As shown in the flowchart in Fig.3.8, a write operation involves four frames transfer. Including a 7-bit target chip address and a 1-bit write operation signal, an 8-bit target register address, and two 8-bit data. On the other hand, a read operation requires five frames to complete. First, the master sends the 7-bit target chip address and 1-bit write operation signal, followed by the 8-bit target register address. After receiving the response from the slave, the master restarts and sends a 7-bit target chip address and a 1-bit read operation signal, and the slave then sends two 8-bit data.

The operation details of the slave become clear from the operation process of the master. Notably, the master's start is controlled by two enable signals, read\_en and write\_en, while the slave's start is triggered by the falling edge of the SDA data line, which is high when idle. Each exchange of information on the SDA data line is 9 bits, with the first 8 bits being messages and the last 1 bit being a response (ACK).

To better explain the operation of I<sup>2</sup>C, we explain it from the signal changes on the SDA data bus. We don't need to focus on the signal on SCL that the master provides, as some details will be mentioned later.

Figure 3.8: Flowchart of I<sup>2</sup>C Master Operation

Figure 3.9: Flowchart of I<sup>2</sup>C Slave Operation

Figure 3.10: SDA Active When Write Operation

Fig.3.10 illustrates the activity of the SDA during a write operation. When the Start signal is sent, the master uses the SDA to send the target chip address and 'write' signal. If the slave chip does not respond, the master chip continues to send the chip address. When the slave chip receives the address from SDA that matches its chip id, it sends an acknowledge signal (low voltage, 0). The master then sends the target register address and the data, and the slave sends a 1 bit ACK signal when it receives each piece of data.

Figure 3.11: SDA Active When Write Operation

The process of I<sup>2</sup>C's read operation is significantly different from that of the write operation, as shown in Fig.3.11. The articles about the I<sup>2</sup>C protocol and some product manuals of sensors with I<sup>2</sup>C components clearly define I<sup>2</sup>C's read operation. The master sends the target chip address and 'write' signal, followed by the target register address. The master then enters the start\_read state, shown in the SDA as the start signal is resent, and the SDA changes from a high to a low when the

SCL is high voltage. Later in the process, the slave will send data twice, and the master sends an ACK signal when the first completion is completed, then sends a NACK signal (high voltage, 1) when the second completion is completed. In the  $I^2C$  read operation, the master will only send a NACK signal after receiving the last byte of data when more information is transmitted.

#### 3.1.7 I<sup>2</sup>C Data Register

To ensure efficient data transfer in I<sup>2</sup>C communication, it is essential to have a register file specifically designed for this purpose. Attempting to grab data from memory during each run can be impractical since it may take multiple clock cycles, which can slow down the process. Additionally, the I<sup>2</sup>C slave cannot pause and wait for the arrival of data, further highlighting the importance of having a register file. Equipping the register file for I<sup>2</sup>C allows the data to be readily available for transfer, reducing delays and improving overall system performance.

Given the limited number of registers available in the SPI-I<sup>2</sup>C Protocol Converter chip, to test the I<sup>2</sup>C read and write function at the specified position on the SPI-I<sup>2</sup>C Protocol Converter chip's register, we have incorporated four 16-bit registers in the current design.

Figure 3.12: I<sup>2</sup>C Data Register

#### 3.2 Simulation and Result

Due to the unique nature of the I<sup>2</sup>C module, it can be challenging to simulate and test the master and slave components separately. This is because both read and write operations require the transmission and reception of data on SDA by both the master and slave. Moreover, if the ACK signal

is not received in a timely manner, the system may crash or terminate. To perform the simulation, we use the  $I^2C$  module depicted in Fig.3.3 and connect the SDA and SCL of the two  $I^2Cs$  using the wiring illustrated in Fig.3.2. In this setup, the first  $I^2C$  is configured as the master (enable = 1), and the second  $I^2C$  is set as the slave (enable = 0).

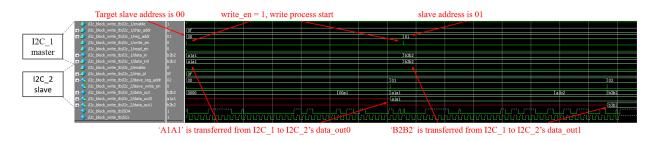

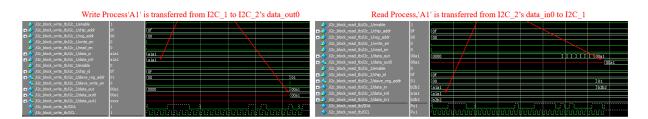

The I<sup>2</sup>C write operation involves two times write processes and is depicted in Fig.3.13. In this simulation, I<sup>2</sup>C<sub>2</sub>1 is set up as the master, operating at 100KHz, while I<sup>2</sup>C<sub>2</sub>2 is configured as the slave, working at 25KHz. The clk\_div value is set to 100, resulting in an SCL frequency of 1KHz. It's worth noting that the master and slave can operate at different frequencies. Still, the SCL frequency must be smaller than the input frequency of the I<sup>2</sup>C. During the chip test, the I<sup>2</sup>C operating frequency is usually at least three times that of the SCL. We increased the clk\_div value from 10 to 100 to meet the requirements in this simulation. At begin of the simulation, we assign the target chip address (chip\_addr) of the master and the chip address (chip\_id) of the slave to 0001111 (0F). We then assign the target register address (reg\_addr) of the two operations to 00 and 01, respectively, verifying that the I<sup>2</sup>C slave can write to different registers. In the first operation, I<sup>2</sup>C<sub>2</sub>1 sends the target register address 00 and 2-byte data 'A1A1' to I<sup>2</sup>C<sub>2</sub>2. According to the address in slave\_reg\_addr, the data in data\_out is stored in the corresponding register (data\_out0) using the register pointer logic. Similarly, the second operation stores the data 'B2B2' in the register data out1.

Figure 3.13: I<sup>2</sup>C Write Simulation

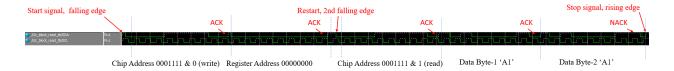

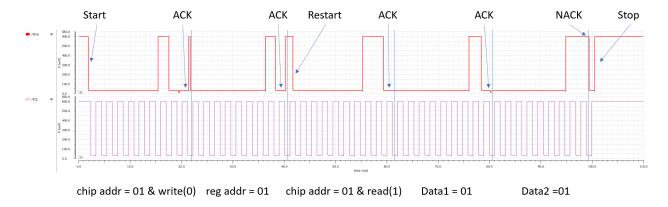

The changes in the Serial Data (SDA) and Serial Clock (SCL) lines during an I<sup>2</sup>C write simulation are presented in Fig. 3.14. As shown in Fig. 3.10, the I<sup>2</sup>C write operation consists of four segments, each with 9 bits. In this example, the master sends the chip address 0F, register address 00, and data

A1A1 to the slave. During transmission, when SCL is high, the value of SDA remains unchanged, and when SCL is low, the value of SDA changes. Sometimes, the value of SDA may change multiple times due to the control of SDA changing, which is approved because of the low voltage on SCL. Additionally, the start signal occurs when SDA changes from high to low while SCL is high, and the stop signal occurs when SDA changes from low to high while SCL is high.

Figure 3.14: SDA and SCL in I<sup>2</sup>C Write Simulation

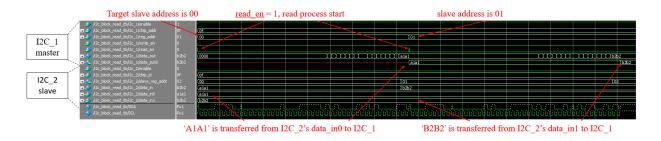

Fig. 3.15 illustrates two I<sup>2</sup>C read operations. In the first operation, the data from the data\_in0 register of I<sup>2</sup>C<sub>2</sub> is read and displayed in the data\_out register of I<sup>2</sup>C<sub>1</sub>. In the second operation, the data from the data\_in1 register of I<sup>2</sup>C<sub>2</sub> is accessed. The simulation confirms that I<sup>2</sup>C can read values from any register.

Figure 3.15: I<sup>2</sup>C Read Simulation

Fig. 3.16 presents the changes in the Serial Data (SDA) and Serial Clock (SCL) lines during the first read operation. Similar to Fig. 3.11, the SDA and SCL processes depicted in Fig. 3.16 are divided into five parts, each comprising 9 bits. However, unlike the write operation, the read operation includes two starts, indicated by two rising edges of SDA. Additionally, the master will send a NACK signal in the last response before the operation is completed.

In addition, we also simulated the scenario where the data length is limited to 1 byte. As previously

Figure 3.16: SDA and SCL in I<sup>2</sup>C read Simulation

mentioned, I<sup>2</sup>C supports both 1-byte and 2-byte transmission modes. And while most sensors on the Texas Instruments website use the 2-byte protocol, some only support the 1-byte I<sup>2</sup>C protocol. Fig. 3.17 shows that the read operation comprises three parts, whereas the write operation consists of four parts. As we did not establish a separate testbench and I<sup>2</sup>C register the device for the 1-byte transfer mode, the data is stored in the lower 8 bits of the 16-bit data register. In the process depicted in Fig. 3.17, both the read and write operations use 8-bit data 'A1'.

Figure 3.17: I<sup>2</sup>C write and read Simulation with 1-Byte Operation

### **Chapter 4**

## Design and Implementation of SPI-I<sup>2</sup>C Protocol Converter chip

Upon completing the simulation of the I<sup>2</sup>C module, our next objective was to test the actual performance of I<sup>2</sup>C by designing a chip with the SPI to I<sup>2</sup>C protocol. The SPI-I<sup>2</sup>C protocol converter chip includes an optimized SPI module and I<sup>2</sup>C module with adjustable output voltage. The SPI-I<sup>2</sup>C protocol converter has significant potential applications, not only because it facilitates protocol conversion from SPI to I<sup>2</sup>C for connecting a microcontroller with an SPI interface and a sensor with only an I<sup>2</sup>C interface but also because it enables better interconnection between two SoCs, which can be challenging to approach in SPI application scenarios.

This chapter will detail the process of implament the I<sup>2</sup>C module, from RTL design to generating the GDSII file and final chip layout. Emulation is performed at various stages to ensure the proper functioning of the I<sup>2</sup>C component. During the RTL stage, we use Modelsim simulation to verify the functionality of the Verilog file. After completing the synthesis and automated place and route, we use Cadence Specter simulation to verify the functionality of the device described by the netlist structure and ensure the success of the synthesis process. Moreover, we stitch the components together in Virtuoso to generate the complete chip.

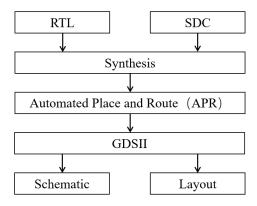

#### 4.1 RTL to GDSII flow for I<sup>2</sup>C Module

According to the process in Fig.4.1, the schematic and layout of the I<sup>2</sup>C module are generated through Synthesis and Automated Place and Route (APR).

Figure 4.1: RTL to GDSII Flow

Synopsys Design Constraint (SDC) [31] is a standard format for constraining the design, supported by almost all Synthesis tools. Generally, timing, power, and area constraints of design are provided through the SDC file; this file has an extension .sdc.

```

set clk_period 20

set clk_uncertainty_setup [expr $clk_period/10]

set clk_uncertainty_hold 0.75

create_clock [get_ports clk] -name clk -period $clk_period

# virtual clock asynchronous to system clocks for inputs

create_clock -name vclk -period $clk_period

set_clock_groups -name cgl -asynchronous -group {clk} -group {vclk}

set_clock_uncertainty -setup $clk_uncertainty_setup clk

set_clock_uncertainty -hold $clk_uncertainty_hold clk

set_input_delay -clock clk 0 [remove_from_collection [all_inputs] {clk}]

set_input_delay -clock vclk 1 {data_in0 data_in1 sda_in scl_in chip_id read_en write_en write_mode reg_addr chip_addr clk_div reset enable}

set_output_delay -clock clk 0 [all_outputs]

set_driving_cell -lib_cell BUF_X0P7B_A9TH -from_pin A -input_transition_rise 1 [remove_from_collection [all_inputs] {clk} ]

set_load 0.2 [all_outputs]

```

Figure 4.2: SDC Code

In the I<sup>2</sup>C module, there's only one system clock CLK, but we also create a "virtual clock" that's asynchronous to "CLK." By defining two clocks as asynchronous, Genus [32] and Innovus [33] will ignore and not clock any paths from one domain to another. We create a virtual asynchronous

clock to associate the input signal ports that contain the I<sup>2</sup>C block because they're asynchronous to CLK. If we skip this step, Genus/Innovus will waste resources optimizing timing paths for other registers in the input port designs. We don't need to specify any parameters for the virtual clock because it doesn't exist in the design, and it's asynchronous to the clock that does exist. We will determine the clock frequency during Synthesis and need to consider the trade-offs of the design. Adding input delay can lengthen the input-to-output and input-to-register data paths, so we set the input delay to 0 for all inputs. Finally, we specify a significant load on the output so that Genus/Innovus will enlarge the cell driving the output.

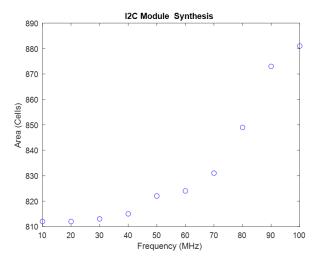

During Synthesis, we sweep the frequency from 10MHz to 100MHz to get the best results, as shown in Fig.4.3. When the frequency exceeds 30MHz, the generated area begins to increase, and when the frequency exceeds 50MHz, the frequency rises rapidly. We'll synthesize this design at 20 MHz since the application doesn't require the module to operate at a very high frequency. Moreover, the oscillator we provide for the I<sup>2</sup>C module works below 100KHz. After Synthesis, we use Innovus software for automated place and route, where we need to focus on Floor Planning and IO Placement. Floor Planning defines the module's area, while IO Placement specifies the input and output port information, which provides the component layout for placement and arrangement in the final stage.

Figure 4.3: Frequency Sweep

After completing Synthesis and APR, Genus and Innovus automatically generate GDSII files and Verilog codes. We import these files into Cadence Virtuoso, where we can access the layout, schematic diagram, and symbols of the I<sup>2</sup>C module.

## 4.2 I<sup>2</sup>C Additional Circuit Design

In addition to using the I<sup>2</sup>C module described by Verilog, we also need to add some circuits to ensure the regular operation of I<sup>2</sup>C. When doing Modelsim simulation, we use some logic circuits instead of the Open-Drain structure. Now the Open-Drain structure will be drawn separately to meet the requirements of the I<sup>2</sup>C protocol standard.

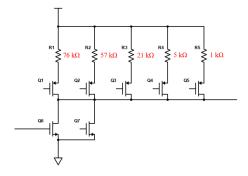

As shown in Fig.4.4, we designed an Open-Drain structure consisting of five pull-up resistors and two NMOS by calculating the transmission line's rising and falling edge times. In addition to the maximum size of the resistor, other components are controlled by a separate logic stored in the SPI register, which allows us to explore the impact of different pull-up capabilities on the SDA signal in the test. We have designed multiple sets of pull-up and pull-down structures for different connection situations. In addition, we explored the power consumption and performance of the I2C module through different structures.

Figure 4.4: Open-Drain Structure

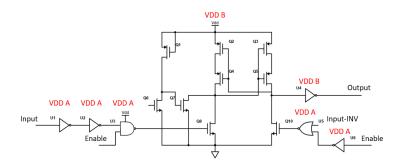

At the same time, to improve the compatibility between the I<sup>2</sup>C module and commercial devices, we added a levell shifter to the circuit to control the voltage on the SDA line because the I<sup>2</sup>C

module works at 0.6V but almost Texas Instruments temperature Sensors work at the lowest is 1.02V. The level shifter can be adjusted to operate safely within the range of 0.6V-1.2V. Fig.4.5 shows the structure of the level shifter.

Figure 4.5: Level Shifter

## 4.3 Cadence Spactre Simulation

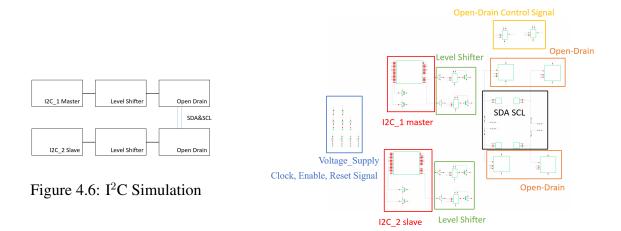

After importing the I<sup>2</sup>C module into Cadence, perform the Spectre simulation to ensure the proper functioning of each component is crucial in completing the final design. The block diagram during simulation is shown in Fig. 4.6, which includes two complete I<sup>2</sup>C modules.

The schematic during simulation is shown in Fig. 4.7. The blue part represents the voltage supplies of the I<sup>2</sup>C and pull-up resistor, which correspond to the I<sup>2</sup>C module and the Open-Drain circuit. Two I<sup>2</sup>C clock signals, enable signals, and reset signals are also included. The red part shows two I<sup>2</sup>C modules, and we added a buffer circuit before the SDA and SCL input ports. The green parts are two-level shifter circuits analyzed in detail in the previous section. The Open Drain circuit is marked in yellow, and this part provides the control for the Open-Drain circuit and determines the details of the pull-up and pull-down circuits. The black part represents two buses containing devices that simulate the PCB ports and the transmission line impedance. Finally, both read and write operations are shown, Fig. 4.8 and Fig. 4.9, and each part is consistent with the simulation results. Cadence simulation is an indispensable step in the design process. In the simulation, we consider the influence of various factors on the circuit, as described in the schematic. Through this

Figure 4.7: Schematic

simulation, we can estimate the actual operating conditions of the I2C module.

As described in the I<sup>2</sup>C module state machine chapter and the Modelsim simulation results section, we analyzed the simulation results at this stage. In the write operation, the signal on the SDA transmission line is divided into four frames for analysis, and each frame is 9 bits. In Fig. 4.8, each frame signal is analyzed, which contains the target chip's address, the target register's address, and two bytes of data.

Figure 4.8: I<sup>2</sup>C write Simulation

Similarly, in the I<sup>2</sup>C write function test, the signal on the SDA line is divided into five frames. In

addition, when the second frame ends, the master resends the start signal by sending the falling edge of the SDA line.

Figure 4.9: I<sup>2</sup>C read Simulation

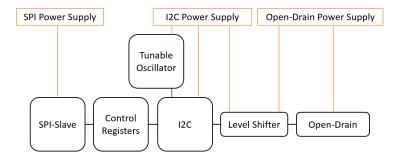

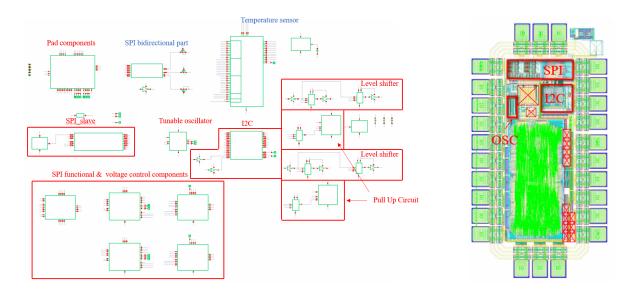

## 4.4 Schematic and Layout of Chip

After completing the simulation of the I<sup>2</sup>C module, we integrated the SPI and I<sup>2</sup>C parts to create the SPI-I<sup>2</sup>C protocol converter chip, illustrated in Fig.4.12. Along with the SPI slave and I<sup>2</sup>C modules, the chip includes an output voltage control module that allows selecting between 0.6V, 1.2V, and 1.8V and a temperature sensor for testing purposes. The SPI bidirectional components, which occupy a large area, are not directly related to the SPI-I<sup>2</sup>C protocol converter and will not be discussed in detail in this article.

Figure 4.10: Chip Block Diagram

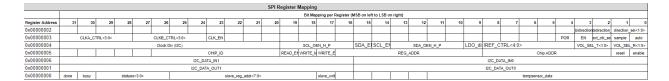

Figure 4.11: SPI Register Table

Figure 4.12: Schematic

Figure 4.13: Layout

Once SPI and I<sup>2</sup>C are connected, we create a table to map the SPI register functions Fig.4.11 to the control port and registers of I<sup>2</sup>C. This allows us to use SPI to control I<sup>2</sup>C. Although this simulation involves too many components that can not be run, tests in the next chapter confirm that it works correctly.

The layout of the SPI and I<sup>2</sup>C parts is marked in red in Fig.4.13. In the next chapter, we will test this part to ensure the proper functioning of controlling the I<sup>2</sup>C through SPI. We will utilize a low-power oscillator to clock the I<sup>2</sup>C. Besides, the red boxes with an 'X' in the figure denote the capacitors in the TSMC library and do not imply any component errors or disabled features. Finally, we have completed the SPI-I<sup>2</sup>C Protocol Converter chip design, and the next chapter will start chip testing.

## Chapter 5

## **Chip Test Results and Analysis**

This chapter will comprise a series of tests conducted to assess the functionality of the SPI-I<sup>2</sup>C protocol converter chip, including function check, static power consumption measurement, dynamic power consumption estimation, and analysis. Additionally, the chapter will explore the implementation of a topology that utilizes three chips.

## **5.1** Build Testing Board

After successfully designing the PCB using PADS software, we soldered the necessary components onto the board. This included filter capacitors and linear and low-dropout (LDO) regulators, essential to ensuring a reliable power supply. ITWOC and PULLUP supply power to the I<sup>2</sup>C module and Open-Drain pull-up resistors.

ESD\_Board and ESD\_I/O are crucial components for protecting electronic devices from damage due to high voltage. With each successive generation of IC development, achieving smaller form factors and thus smaller process nodes, these devices exhibit an increased vulnerability to damage or latch-up from electrostatic discharge (ESD) threats. Our ESD protection can ensure that the voltage exceeds the ESD\_Board and ESD\_I/O interface is grounded to protect the chip from

Figure 5.1: Testing Board

breakdown by excessive voltage. During testing, 1.2V is applied to ESD components, meaning any voltage exceeding this threshold in the power supply circuit will trigger automatic discharge through the ESD mechanism. This prevents the chip from being broken down and ensures optimal performance.

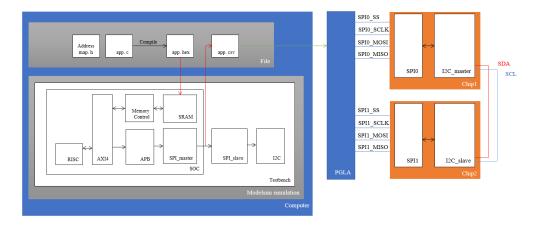

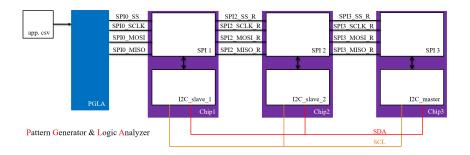

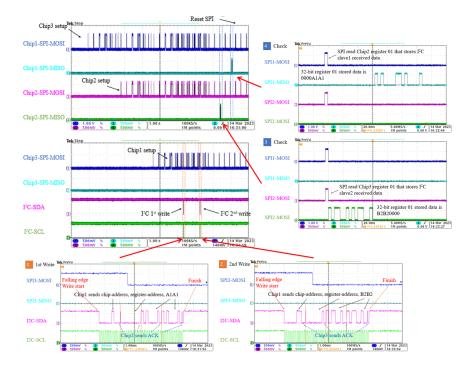

### **5.2** I<sup>2</sup>C Basic Function Test

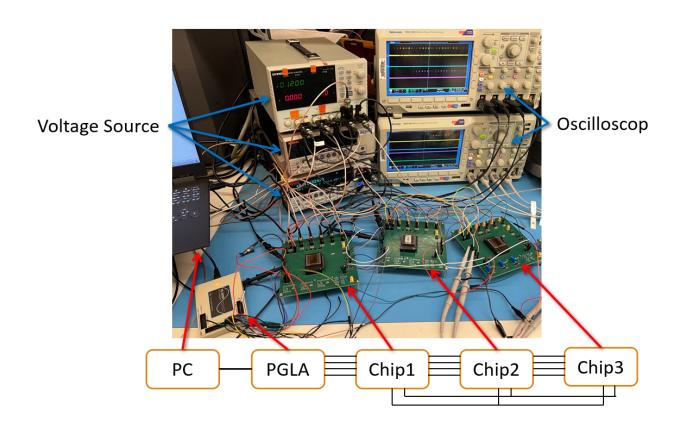

The block diagram used during the test is depicted in Fig.5.2. As previously stated, the I<sup>2</sup>C test must be conducted on two chips since the Master and Slave cannot function independently and work together on one chip. The specifics of controlling SPI and I<sup>2</sup>C using C code are illustrated in the left part of Fig.5.2. As two chips are utilized in the test, two SPI Master components are implemented on the SoC. The C code is compiled into machine code (.hex) by the compiler and subsequently uploaded to the SRAM in the SoC via the testbench. During runtime, the RISC core transmits relevant instructions to the SPI through the AXI4 and APB protocols in the SoC. Fig.5.3 displays a test code that effectively drives the SPI.

This code demonstrates how to use C code to control  $I^2C$ . The SPI1\_write function writes values to the specified SPI register. The  $I^2C$  control information is described in the SPI register table created during the Chip top design and connected to  $I^2C$  in the previous chapter.  $I^2C$  can be configured and

Figure 5.2: Block Diagram of Test

started by modifying the corresponding position's value. At the end of the configuration process, the read\_en and write\_en signals must finally be given. This is because the Pattern Generator Logic Analyzer (PGLA) has a slow transfer rate, and it's important to avoid starting the system before the configuration is completed.

```

//Master Journal (19):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // ID-check

SPII_MRITE(0x1, 0x03, 0xFF800000, 8, 4, 32); // CLK_en 1, CLK_frequency ff (00-ff)

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010000b, 8, 4, 32); // CLK_div register 10, Pulldown SDA 1 SCL 1, Pullup SDA 1111 SCL 1111

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010000b, 8, 4, 32); // set all the register values, CHIP ID 0001, REG_ADDR 0000, CHIP addr 0002

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010000b, 8, 4, 32); // disable read

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010000b, 8, 4, 32); // disable read

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // set all the register values, CHIP ID 0001, REG_ADDR 0001, CHIP addr 0002

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // set all the register values, CHIP ID 0001, REG_ADDR 0001, CHIP addr 0002

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // enable read

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // disable read

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // disable read

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // disable read

Wait(3):

SPII_MRITE(0x1, 0x05, 0x0010020b, 8, 4, 32); // disable read

Wait(3):

```

Figure 5.3: C Code for I<sup>2</sup>C Master Setup and Run

The most time-consuming aspect of gate-level simulation for digital circuits is generating input waveforms or stimuli. One efficient approach is to run the simulation initially as an RTL simulation and then export all the input waveforms to a .csv file. After a successful SoC simulation, we can use the testbench code to export the data of the specific segment we want to simulate. The Pattern Generator Logic Analyzer (PGLA) is a specialized tool for generating pulse signals. We use it to describe the data in the .csv file and generate accurate electrical signals. The PGLA is then connected to the test circuit board, enabling us to simulate communication between the SPI Master

and the SPI slave on the chip and modify the value in the SPI register. Then we use an oscilloscope to observe the signals on the SDA and SCL lines to ensure the  $I^2C$  is working correctly.

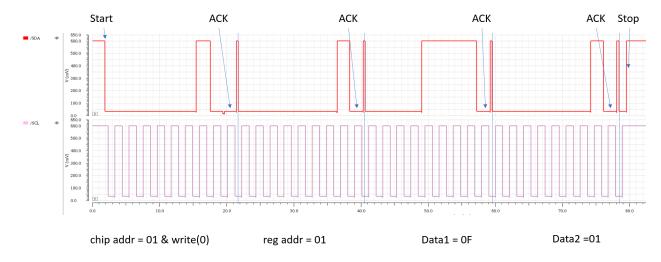

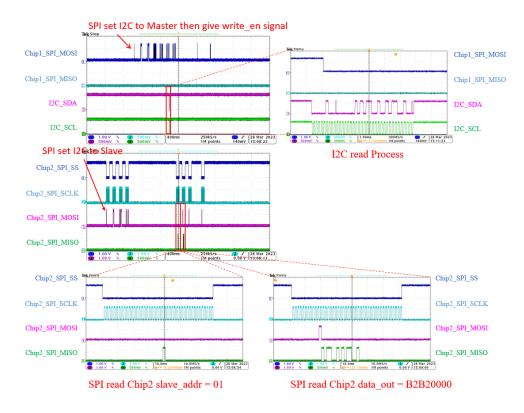

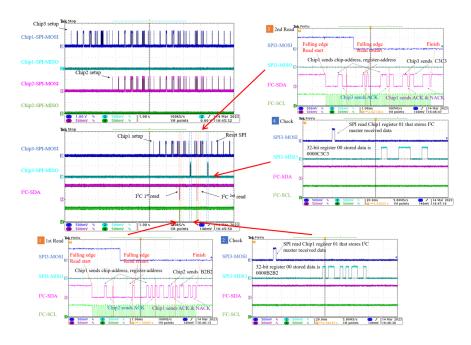

Figure 5.4: Write Process

The write operation results are shown in Fig.5.4. Once the I<sup>2</sup>C operation is completed, we can query the value of the corresponding register through SPI to verify that the I<sup>2</sup>C operation was performed correctly. We first set the address of our I<sup>2</sup>C master to 01 and the address of the slave to 00. By comparing the C code, we want the master to change the register with a slave address of 01 to B2B2. Since the register with address 00 and the register with address 01 is placed in a 32-bit SPI register, and address 00 refers to the upper 16 bits in the SPI register, we can verify the test's success. Like the previous simulation results, the operation is divided into four segments of 9 bytes each. At the same time, the information transmitted is B2B2, and the transmitted address is 01, which is consistent with the previous observation of the register through SPI.

The reading test was conducted twice, displayed in Fig.5.5, with the master successfully reading

the information on the two registers of the slave chip. To confirm the test's success, we cross-checked the C code, the register information read by SPI, and the oscilloscope's reading of the SDA line.

Figure 5.5: Read Process

In this part of the test, we checked the I2C ability to read and write to the specified register. The regular operation of the I2C module is verified by reading the value in the I2C register through SPI and comparing it with the expected value.

## 5.3 Power Consumption Measurement and Modeling

#### **5.3.1** Static Power

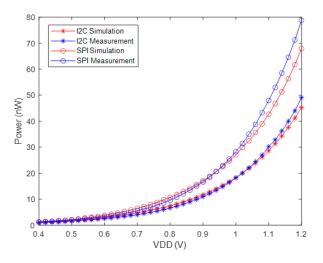

We first tested the static power consumption of SPI and I<sup>2</sup>C. At the same time, based on the simulation results, we drew a comparison chart of SPI and I<sup>2</sup>C from 0.4V to 1.2V, by simulation

and test. We found that the SPI-I<sup>2</sup>C protocol converter can operate at a minimum of 0.4V, which is lower than expected. When we tested the static operating voltage of I<sup>2</sup>C, we discovered that it only consumes 2.49nW at 0.4V and 4.19nW at 0.6V, but as much as 40.9nW at 1.2V. The figure shows that static power consumption increases exponentially as the supply voltage increases. We chose I<sup>2</sup>C as the communication protocol because its static power consumption is lower than SPI's. However, we found that our simulation and test results had errors between 0.4V and 1.2V, likely due to the mutual influence of multiple power supply ports on the chip. The significant error occurred when SPI operated at 1.2V, at about 9.2%.

Figure 5.6: Dynamic power

#### **5.3.2** Active Power

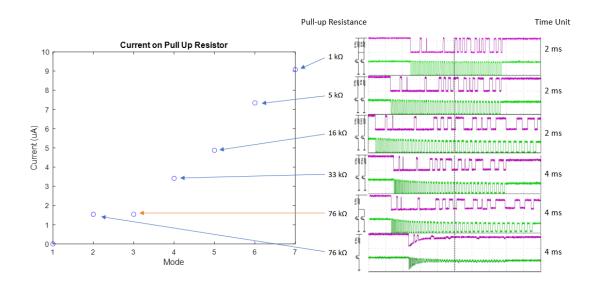

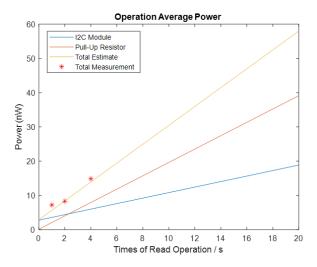

Our investigation revealed that the power consumption during the operation of the I<sup>2</sup>C component is primarily due to the loss resulting from the short circuit of the pull-up resistor in the Open-Drain design. In the previous chapter, we discussed the design of the pull-up resistor, which involved creating various resistance values and developing a backup solution for the pull-down MOS design. Fig.5.7 illustrates that using only one pull-down MOS is insufficient to handle the pull-down capability of the circuit, resulting in abnormal operation of the I<sup>2</sup>C module. Furthermore, as the

resistance value of the pull-up resistor decreases, the waveforms on SDA and SCL become more standardized, but the power consumption increases. Ultimately, we selected the scheme indicated by the red arrow and tested its working power consumption.

Figure 5.7: Current on Pull Up Resister

We conducted a simulation with a duration of 10mS to analyze the power consumption of the I<sup>2</sup>C module during a read operation. Our findings indicate that the average power consumption of the I<sup>2</sup>C module during this operation is 30.4nW, while the pull-up resistor consumes 195nW. This suggests that the dynamic power consumption of the I<sup>2</sup>C module is significantly lower than the short-circuit power consumption of the pull-up resistor. To estimate the overall power consumption of the I<sup>2</sup>C module in its working state, we considered both the dynamic and static power consumption observed in our simulation. Additionally, we tested the power consumption of the I<sup>2</sup>C module using the SPI-I<sup>2</sup>C chip. We conducted the test at different frequencies: once per minute, twice per minute, and four times per minute. We observed some deviation in the test results, which can be attributed to the difference between the actual operating frequency of the I<sup>2</sup>C module and our estimate. By averaging multiple measurements of the three operating states, we estimated the overall power consumption of the I<sup>2</sup>C block operation based on the duty cycle.

The current in Fig.5.7 results from the Cadence simulation. At the same time, the power consump-

Figure 5.8: Active Power

tion measured in Fig.5.8 is the measurement result of the actual chip. There is a gap between the two because there is a certain error in the measurement process, and the simplest model is used in the simulation in order to use the gap between the current and the performance. In an actual chip, the magnitude of the current cannot be directly measured, so we cannot obtain the magnitude of the current flowing through the resistor.

## **5.4** System Topology Test

After completing the basic test of the I<sup>2</sup>C module, we conduct a systematic topology test on the SPI-I<sup>2</sup>C protocol converter chip. Since there are only two SPI masters in the current test platform, we used some optimized functions during the test. In the SPI-I<sup>2</sup>C chip, SPI differs from the traditional design and can pass the MOSI and MISO signals to the next level through the switch, which means that we can connect the SPI in series and identify the communication target through the chip ID, which is similar to how the I<sup>2</sup>C module completes chip ID identification, as Fig.5.9.

Through the connection of the three chips, we can set their SPI module and I2C module in turn and then read the registers in the chip through the SPI Master to realize the detection of the I2C

Figure 5.9: 3 Chip I<sup>2</sup>C Write Test

operation. In Fig.5.10, we did two write operations using the I<sup>2</sup>C master. The first time, we write 'A1A1' to slave1, whose chip address is 02, and the target register address is 01. And the second time, we write 'B2B2' to slave2, whose chip address is 03, and the target register address is 00. In the following verification process, since we can only perform operations on the SPI sequentially, we sequentially read "A1A1" stored in Chip2 (Slave1) and "B2B2" stored in Chip3 (Slave2).

Figure 5.10: 3 Chip I<sup>2</sup>C Write Test

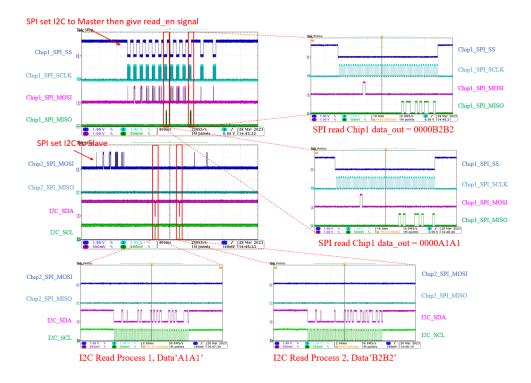

When performing a read operation, we first read the 'B2B2' stored in Chip2 Register 00 and then use SPI to read the data from the I<sup>2</sup>C master for verification. Then read 'C3C3' in Chip3 Register

45

01. The data out of the I<sup>2</sup>C master is always connected to the last 16 bits of the 32-bit register, consistent with what we described in the I<sup>2</sup>C data register.

Figure 5.11: 3 Chip I<sup>2</sup>C Read Test

Our latest testing round has proven the successful functionality of the I<sup>2</sup>C module, as we were able to read from and write to various registers on different chips. This success highlights the I<sup>2</sup>C's ability to interconnect chips effectively within a distributed system, ultimately contributing to its efficiency. We also plan to test the four-chip interconnection to prove that the protocol conversion chip can do the job in the mesh network structure. The test results are the same as those shown in this chapter, and the structure is complex, so it is not shown.

## Chapter 6

## Integrate the I<sup>2</sup>C Module into the SoC

Now that the SPI-I<sup>2</sup>C Protocol Converter Chip testing is complete, the next step is integrating the I<sup>2</sup>C block into the System-on-Chip (SoC). The current SoC features multiple SPI masters, a necessary compromise to facilitate communication with several chips. Adding the I<sup>2</sup>C protocol block to the SoC can reduce the number of required SPI protocol blocks, resulting in lower power consumption.

Integrating I<sup>2</sup>C into an existing SoC can be challenging, as it requires a thorough understanding of the system architecture and the internal protocols of the SoC. This chapter will discuss these aspects in detail and explore the process of adding components to a complete system.

### **6.1 SoC Architecture**

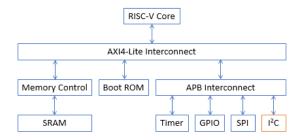

The currently established SOC includes RISC-V Core, Boot ROM, memory management unit, SRAM, and system interconnects. The core named BottleRocket [34] is a 32-bit, RISC-V microcontroller-class processor core built as a customized microarchitecture from the Free Chips Project Rocket core components. The SoC uses two different interconnect protocols, ARM Advanced Microcontroller Bus Architecture (AMBA) Advanced eXtensible Interface (AXI) [35] [36] and ARM

AMBA Advanced Peripheral Bus (APB) [37]. AMBA AXI4-Lite has a more straightforward interface than the complete AXI4 and is suitable for connecting the microcontroller with boot ROM, SRAM memory controller, and APB bridge in this project. APB bridge [38]. The APB bridge connects peripheral components, such as General-Purpose Input/Output (GPIO), SPI, and I<sup>2</sup>C. By setting addresses for different components, the CPU can write to the control registers of different components to achieve the purpose of register control.

Figure 6.1: SoC Architecture

## **6.2** Connect I<sup>2</sup>C module with APB bus

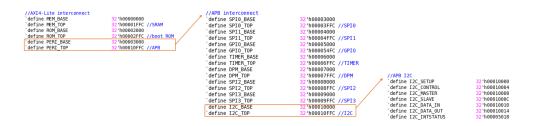

### **6.2.1** Update Address Map

In the address map, all components included, such as the corresponding addresses of SRAM, Boot ROM, and APB interconnect, are defined first because this part is the essential component requirement of SOC, which is prepared for AXI4-Lite interconnect identification. AXI4-Lite interconnect transfers instructions of different addresses to the corresponding modules. The APB interconnect works similarly, distributing instructions to additional peripherals.

As shown in Fig.6.2, in the AXI4 interface, the address bits covered by the APB interface and I<sup>2</sup>C components present an inclusion relationship. Among the address bits covered by I<sup>2</sup>C, six sets of registers are enabled and have corresponding addresses corresponding to them. In addition, there is a single address for implementing the interrupt mechanism. Because the virtual space allocated

Figure 6.2: Address Map

to I<sup>2</sup>C is abundant, it is easy to find and supplement corresponding functions.

| 3                        | 1 1:              | i                     |           |                                    |    |                                        |                     |             | 0       |

|--------------------------|-------------------|-----------------------|-----------|------------------------------------|----|----------------------------------------|---------------------|-------------|---------|

| 0x 00010000 I2C_SETUP    |                   | CLK_DIV[11:0]         |           |                                    |    | DS                                     | OD                  | RS          | EN      |

| 0x 00010000 I2C_CONTROL  |                   |                       | В         | U DO                               | sw | ST                                     | RE                  | WM          | WE      |

| 0x 00010000 I2C_MASTER   |                   | REG_ADDR [15:8]       |           | CHIP_ADDR [6:0]                    |    |                                        |                     |             |         |

| 0x 00010000 I2C_SLAVE    |                   | SLAVE_REG_ADDR [15:8] |           | CHIP_ID [6:0]                      |    |                                        |                     |             |         |

| 0x 00010000 I2C_DATA_IN  | DATA_IN_1 [31:16] | DATA_IN_0 (15:0)      |           |                                    |    |                                        |                     |             |         |

| 0x 00010000 I2C_DATA_OUT | DATA_OUT_0 [15:0] | DATA_OUT_0 [15:0]     |           |                                    |    |                                        |                     |             |         |

|                          |                   | • EN • RS • OI • DS   | Re:<br>Op | able<br>set<br>en_Drain<br>ta_Size | :  | WE<br>WM<br>RE<br>ST<br>SW<br>DO<br>BU | Writ<br>Rea<br>Stat | e_Writ<br>e | e<br>le |

Figure 6.3: I<sup>2</sup>C Control and Data Register Map

Then, I put all the signals related to I<sup>2</sup>C in the planned address area, as shown in Fig.6.3. Essential parameters are stored in I<sup>2</sup>C\_SETUP to determine the working condition of I<sup>2</sup>C, and each parameter is introduced in detail when introducing the I<sup>2</sup>C port. I<sup>2</sup>C\_CONTROL contains the startup and status signals when I<sup>2</sup>C is running. Monitoring this register can effectively understand the running status of I<sup>2</sup>C. The last two registers are connected to the data input and output of I<sup>2</sup>C. They store two pieces of data, each of which is 2 bytes.

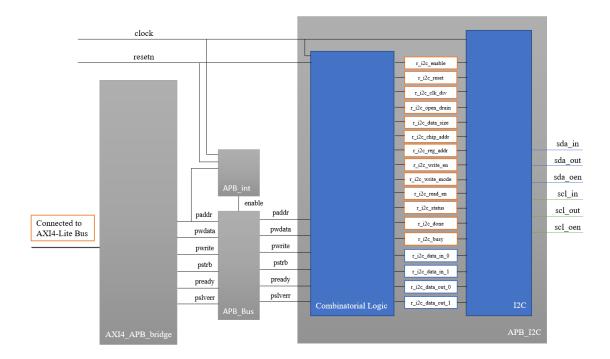

## 6.2.2 Build APB to I<sup>2</sup>C Logic

The APB\_I<sup>2</sup>C file contains all the logic from the APB interface to the I<sup>2</sup>C control registers. According to the structure in Fig.6.4, the output of the APB slave is matched to the corresponding control register. At the same time, the internal logic of APB also needs to be modified because new functions are expanded.

Figure 6.4: AXI4-Lite to APB to I<sup>2</sup>C Structure

After the information is delivered to APB, according to the target address stored in APB\_paddr, APB\_int will transmit the APB data to the corresponding APB\_slave. In APB\_I<sup>2</sup>C, the output of APB\_slave will store the message in the corresponding register.

In the Digital\_Top file, put the APB\_I<sup>2</sup>C module, we can see that the control signal terminal of the module and the APB interface are connected through APB\_int\_to\_I<sup>2</sup>C\_Bus. On the other hand, the I/O port is connected to the SOC pad via I<sup>2</sup>C\_Pad\_Bus. In addition, a dedicated interrupt signal port is provided for I<sup>2</sup>C to use when it is written into data. I<sup>2</sup>C\_interrupt occurs when the slave\_write\_en signal is generated, and its function is to wake up the core to ensure that the written data is stored in the correct position.

Figure 6.5: Connection of APB\_I<sup>2</sup>C

#### **6.3** Modelsim Simulation

Compared to the simulation of the  $I^2C$  module, the difficulty of completing the system simulation in Modelsim is very serious, even if the SoC is complete. Designing the simulation environment directly in the testbench for system testing is not feasible. Fortunately, this complete system can run C code, so we can design corresponding code to control SoC and finally achieve the purpose of controlling  $I^2C$ .

#### **6.3.1** Structure of SoC and Testbench

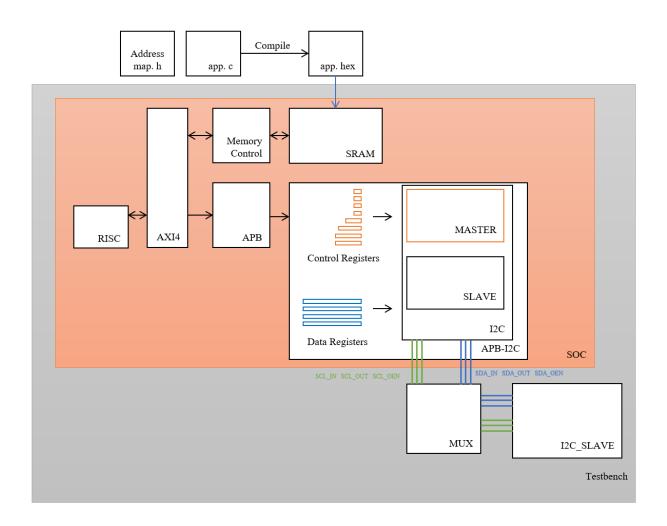

A complete set of the simulation process is used to simulate the digital circuit system. According to the description of the testbench in Fig.6.6, from the C code to the signal generation on the I<sup>2</sup>C data line, we successfully put I<sup>2</sup>C into the system.

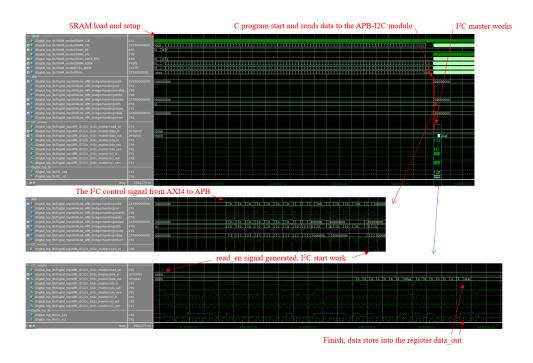

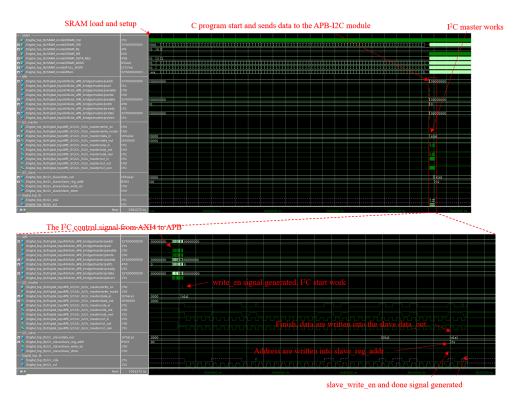

To show the process of SOC simulation implementation more clearly, the whole process of realizing SOC Modelsim simulation is described with simple C code. First, compile the code "app.c" and the address mapping table to save the machine code in hexadecimal. Import the machine code into SRAM through the statement in Testbench. RISC modifies the registers that control I<sup>2</sup>C located in the APB\_I<sup>2</sup>C module by running instructions stored in SRAM. The interface of the AXI4 protocol is complex, directly connected to RISC, and can respond quickly. As shown in Fig.6.4,

Figure 6.6: SoC-I<sup>2</sup>C Simulation Flow

when the target address is a peripheral component, with AXI4\_int, the AXI4 slave will pass the information to the APB master. Similarly, APB\_int will help the APB slave connect with the corresponding address in the APB\_I<sup>2</sup>C module, and then the internal logic will store the data in the register. As described in Fig.6.6, the registers are connected to the input and output of the I<sup>2</sup>C module. In short, through the RISC, AXI4, and APB protocols, the I<sup>2</sup>C is implemented using the C program.

### **6.3.2** Design I<sup>2</sup>C operation program